内容介绍

项目备注

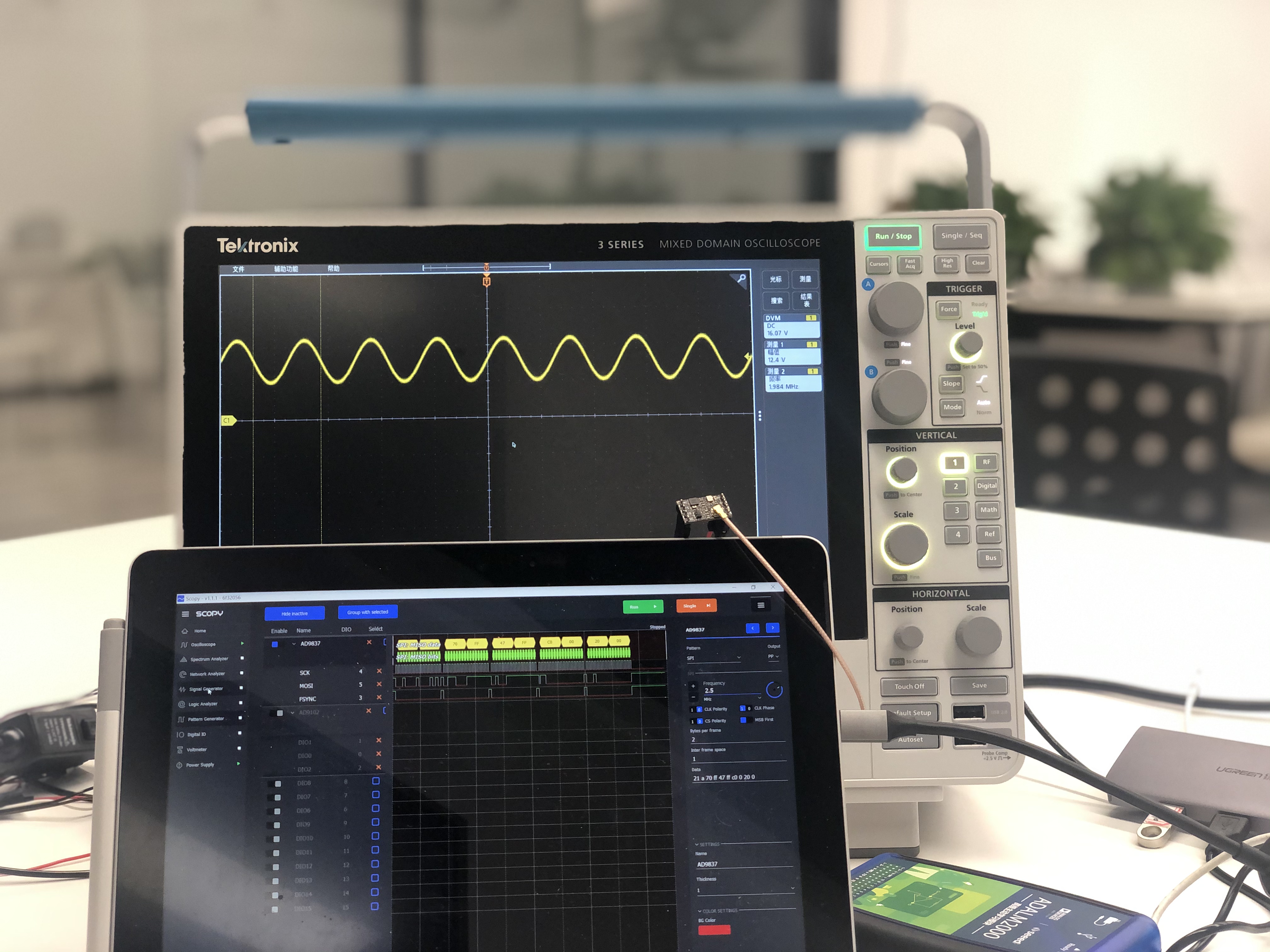

参考案例

内容介绍

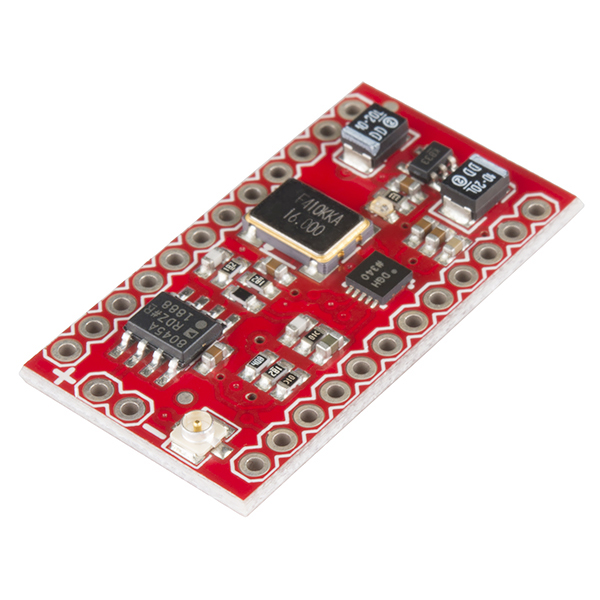

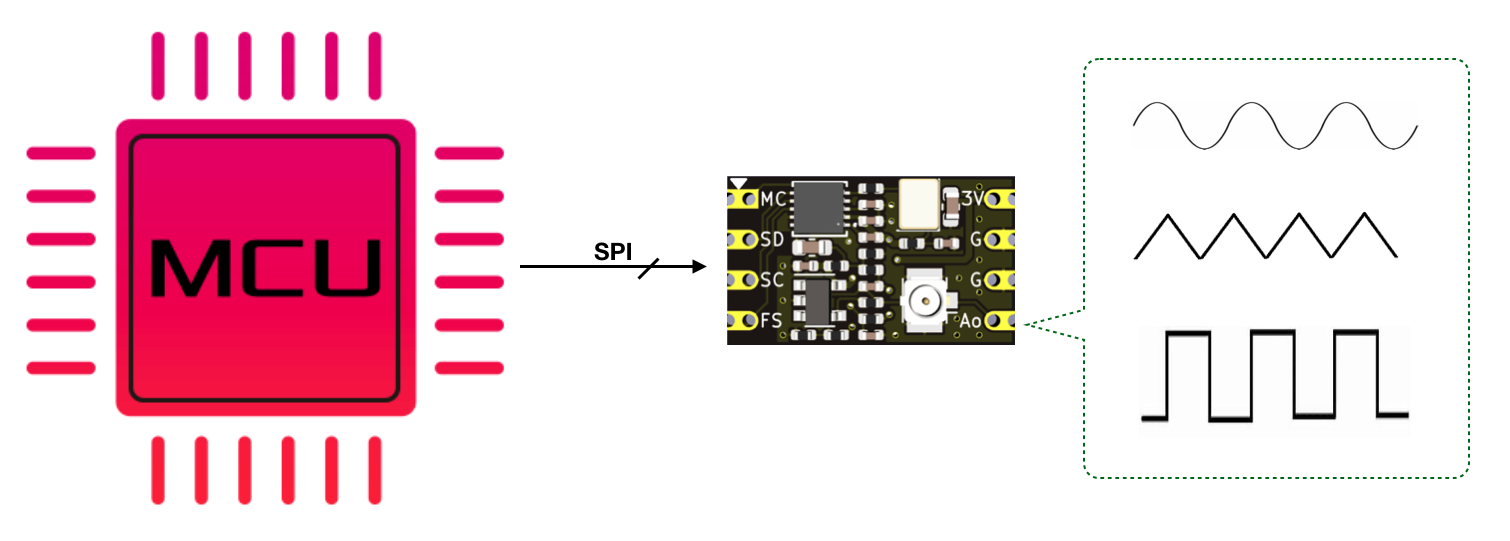

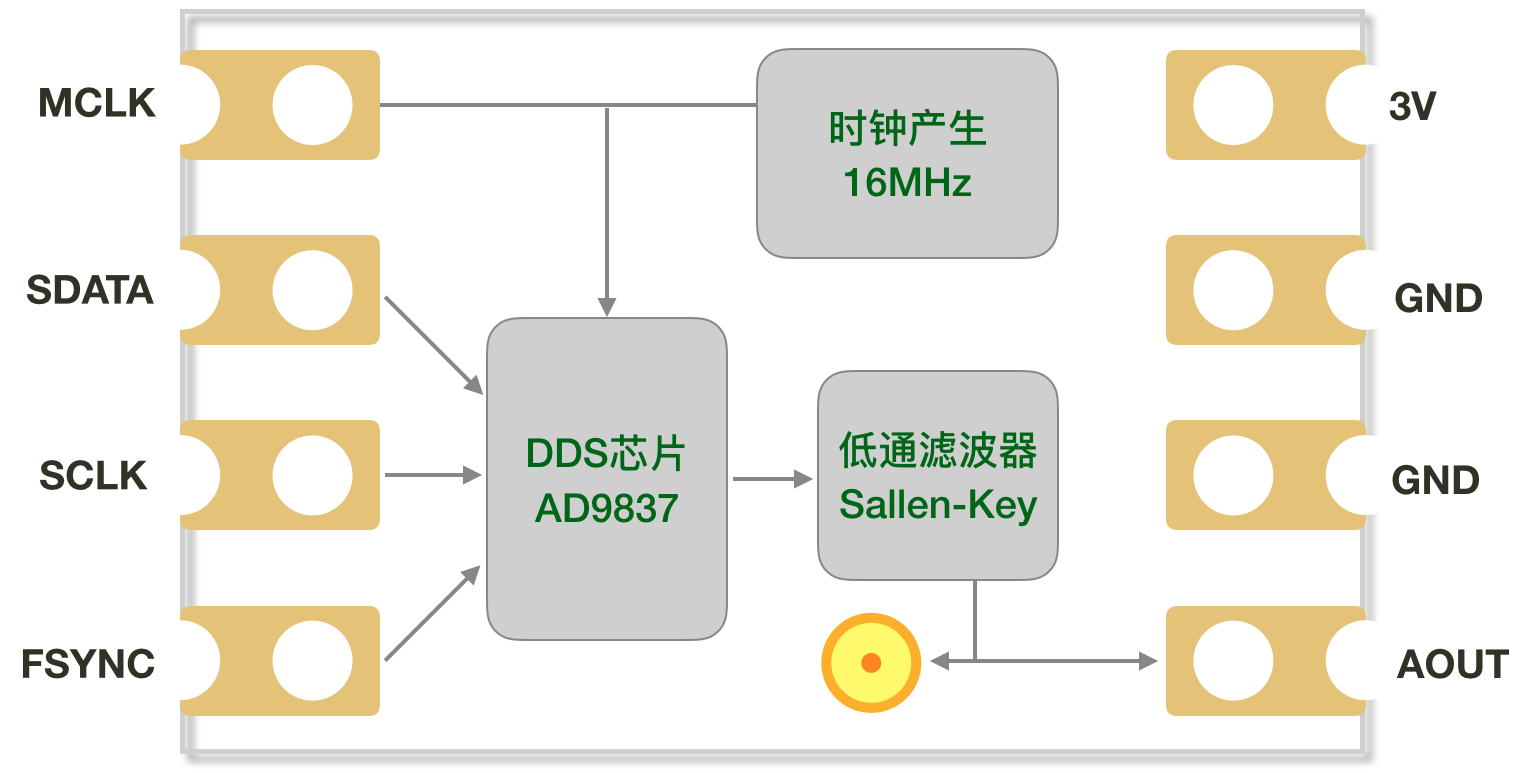

这是我们硬禾实战营开发的DDS信号发生器模块中的一枚,只有8个管脚,其中用SPI总线可以通过任何一款MCU或FPGA对其进行配置,它工作于16MHz的主频,能够输出正弦波、方波和三角波三种波形,输出模拟信号的最高频率可以达3MHz,幅度能够到1Vp-p。

该模块的输出信号可以通过板上的Pin5或u.FL的射频连接器,输出信号以1.65V为直流偏置点(3.3V供电的情况下),输出信号的幅度和直流偏置都是固定的,不能调节。

- DDS内部采用了10位DAC以实现较高的波形准确度

- 2个频率寄存器,可以用来设置输出信号的频率

- 频率分辨率能够精密到0.06Hz

- 2个相位寄存器

- 外部的MCU或FPGA可以通过SPI接口对其进行配置

- SPI的接口总线速度达40MHz

- 工作电压范围:3-3.3V

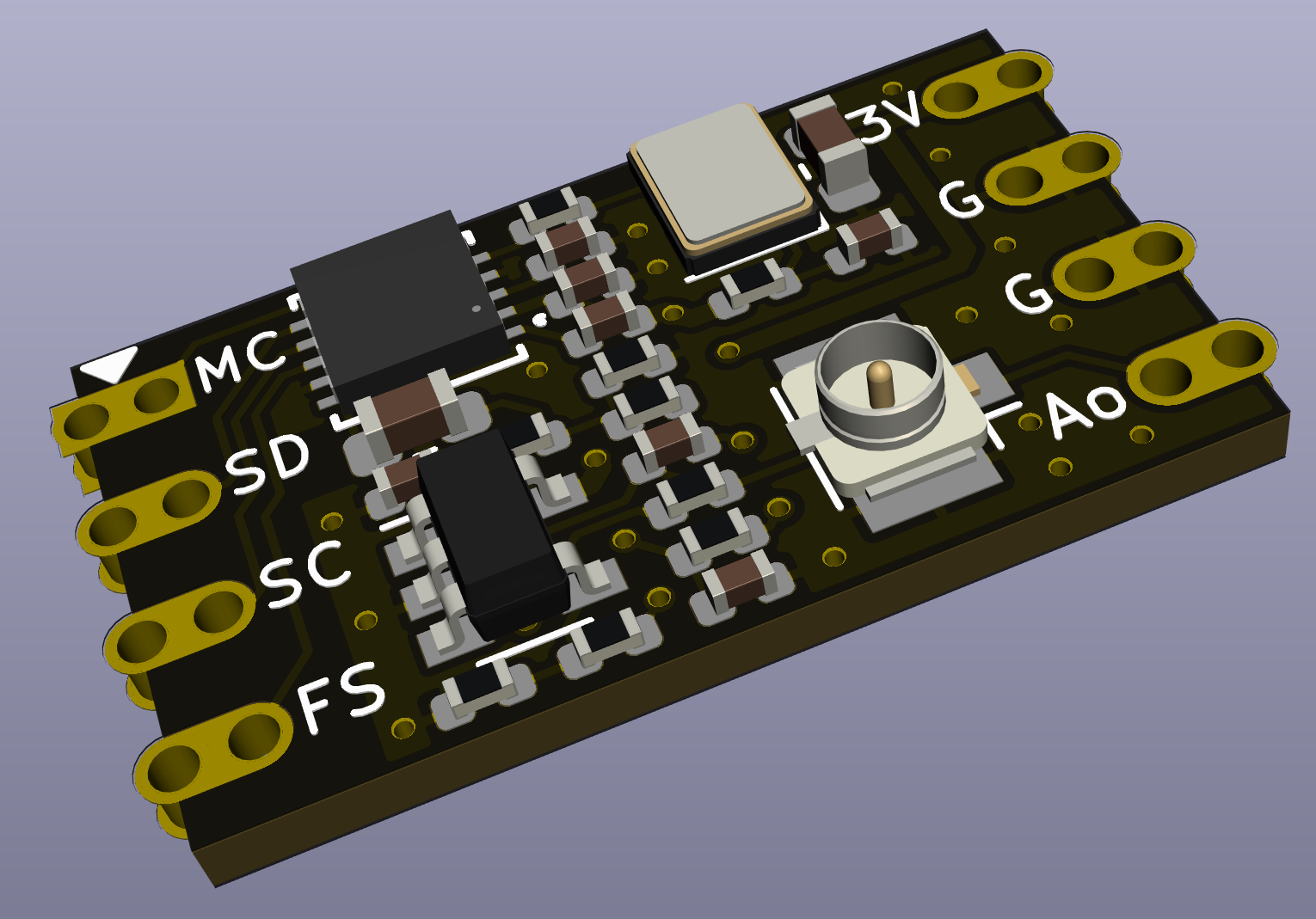

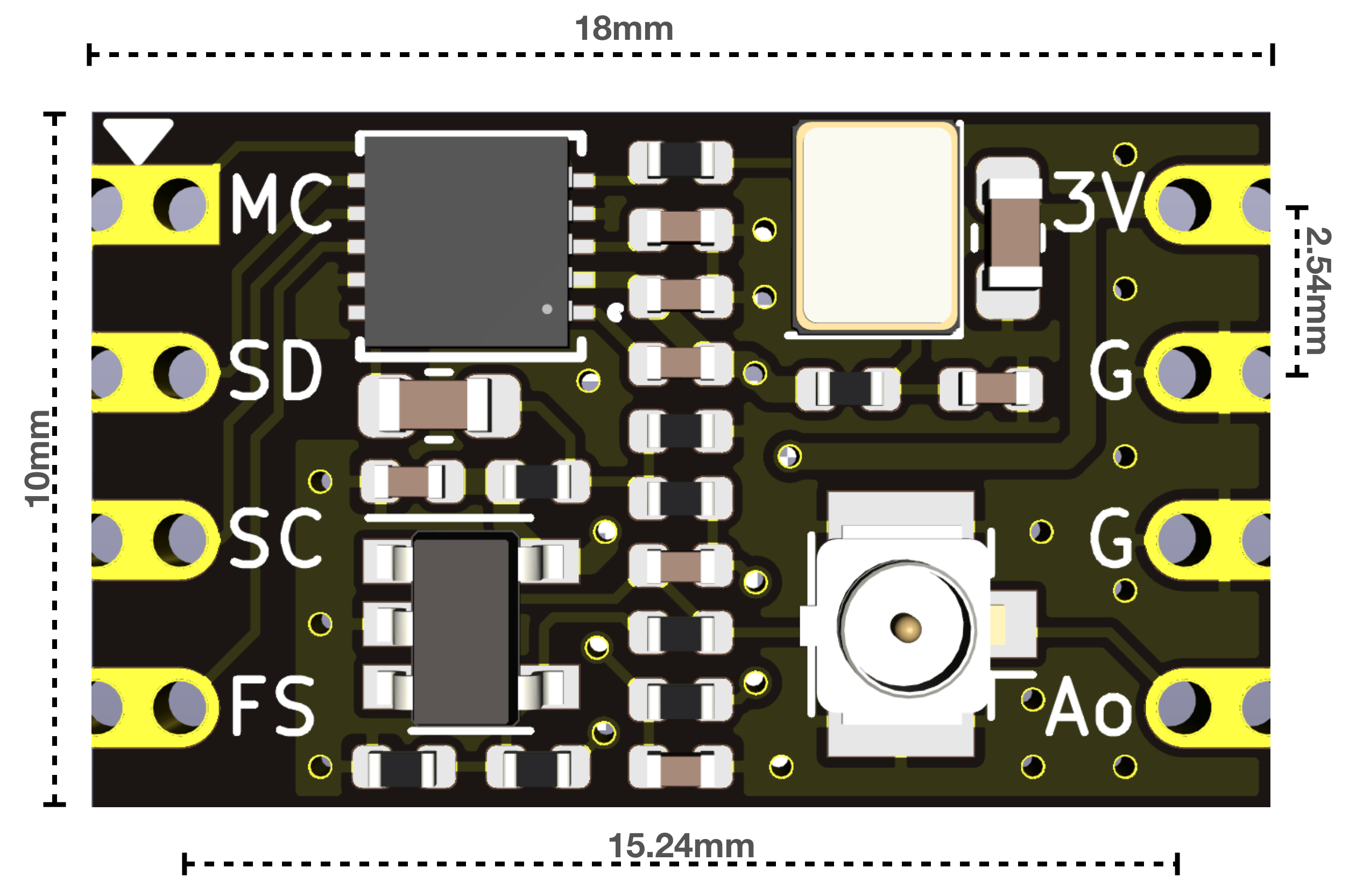

模块的3D效果图

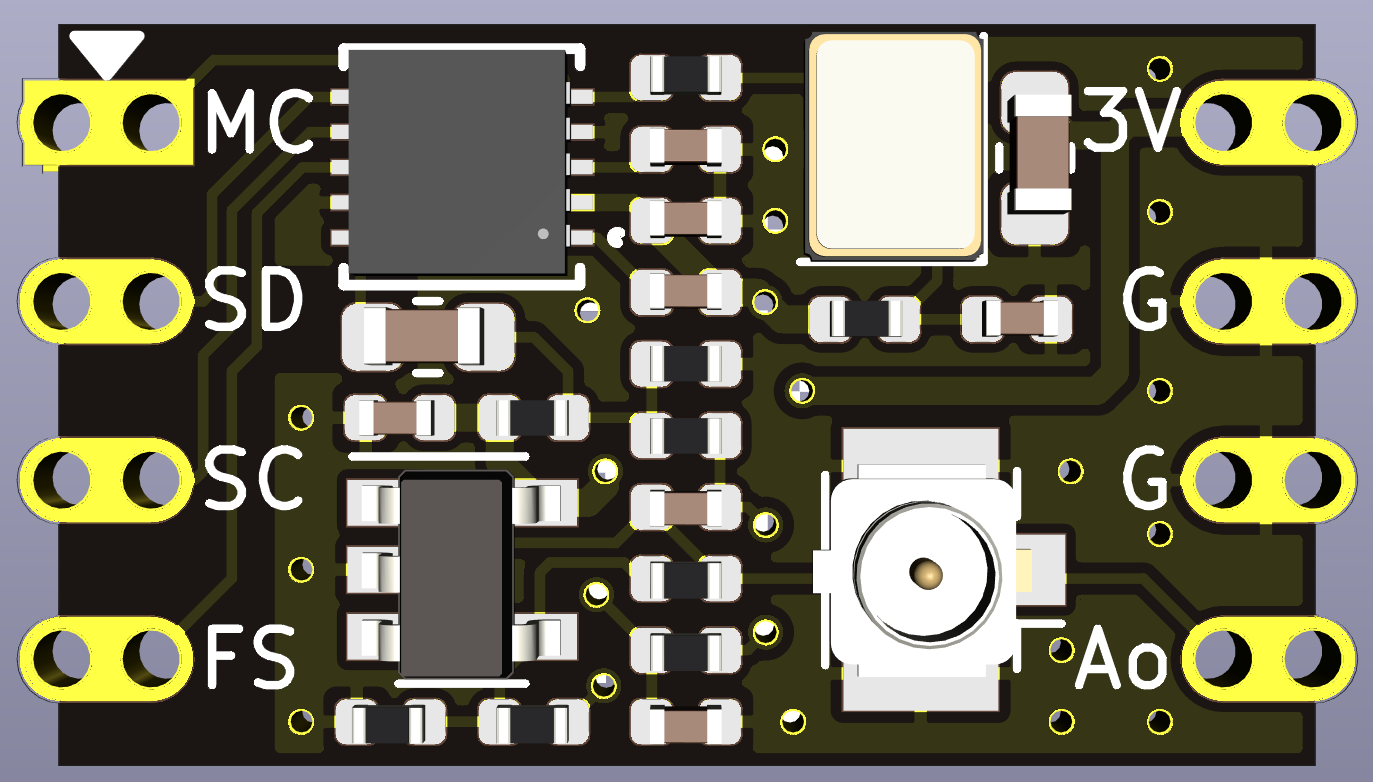

模块的结构图

模块的物理尺寸

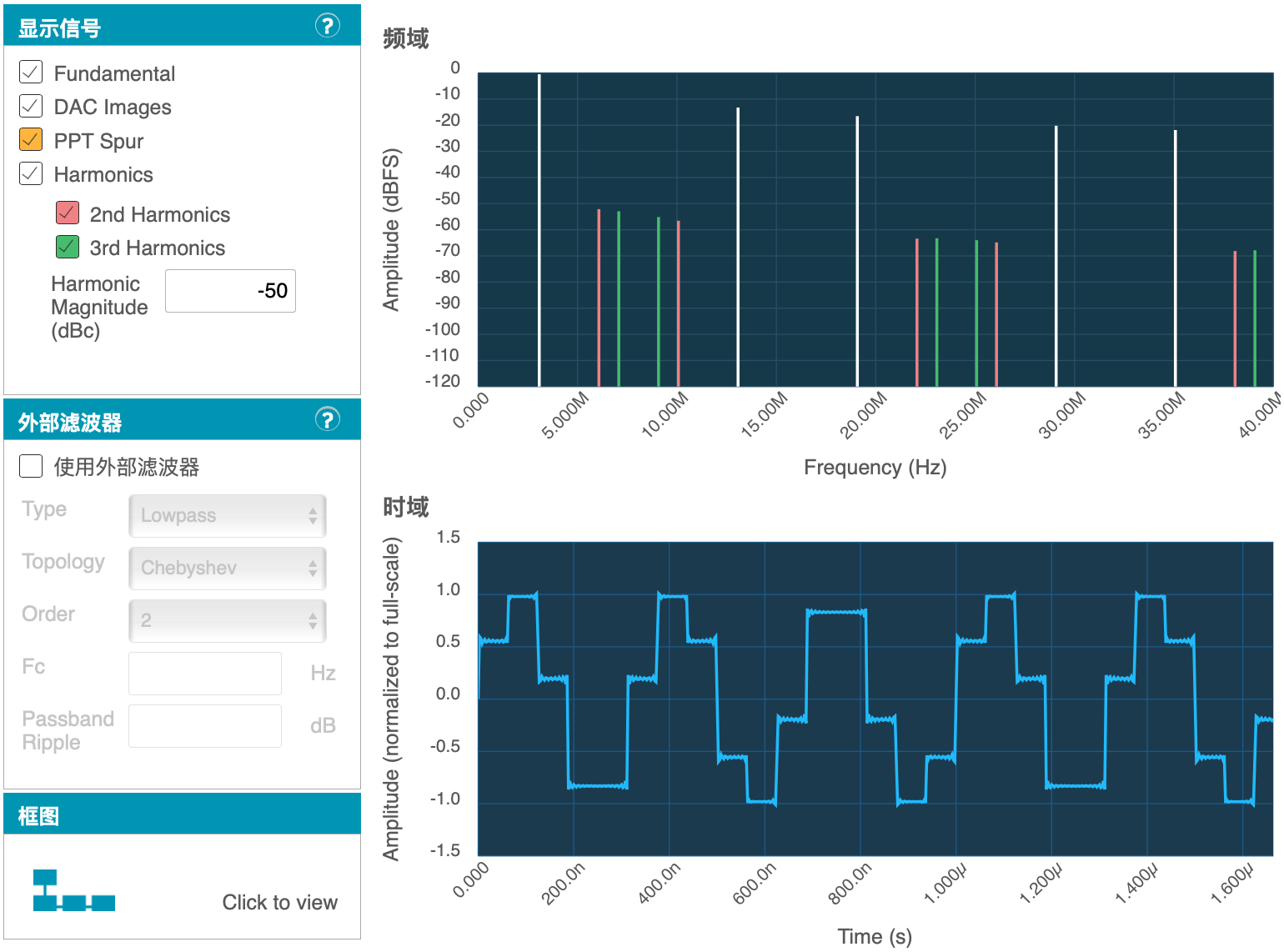

为方便设计,ADI专门提供了基于网页的ADIsimDDS的程序, 用于帮助设置正确的频率控制字,并直观地查看输出信号的频谱分量以及需要的滤波器及其参数。

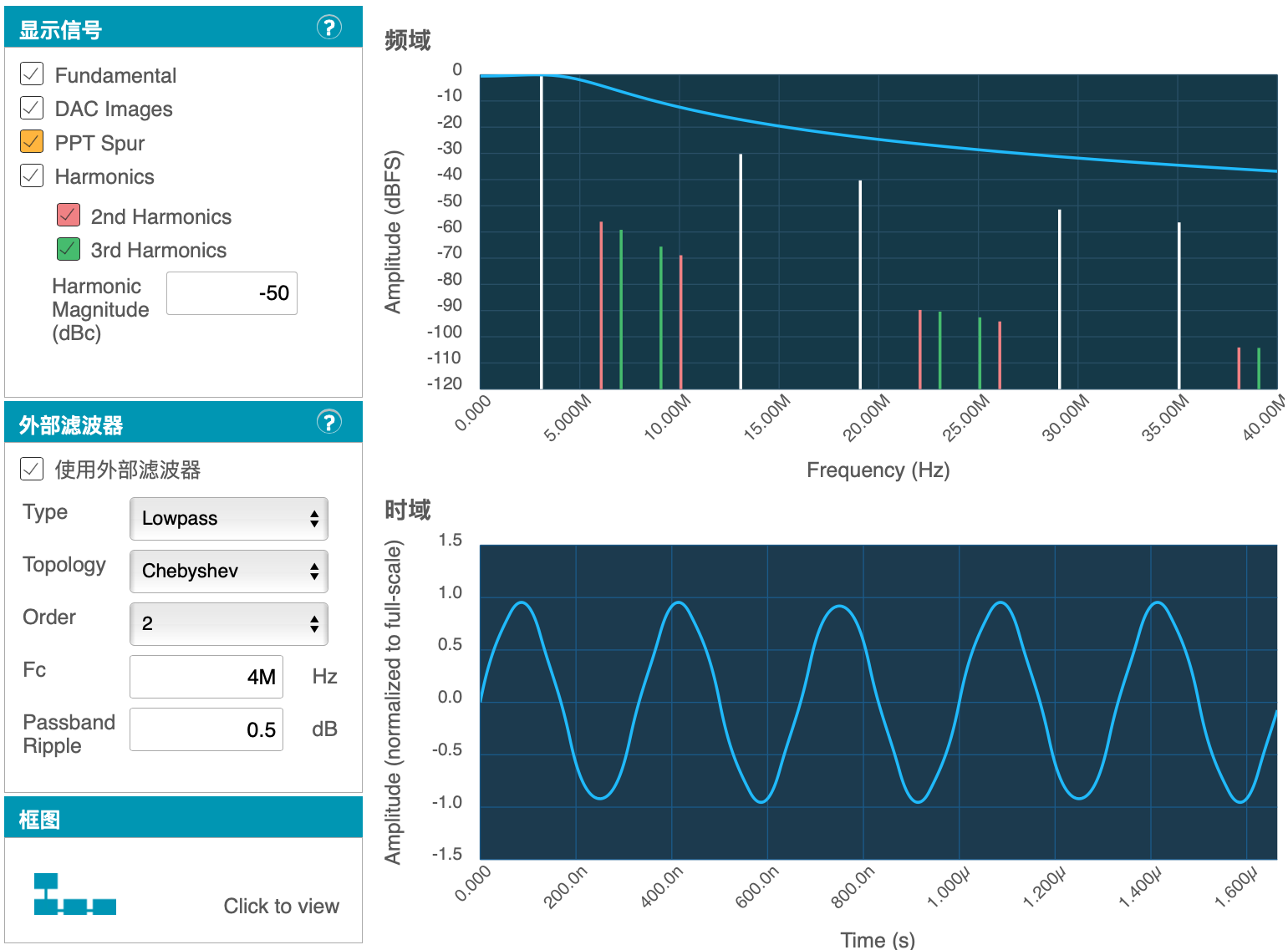

16MHz主频,未加低通平滑滤波器,输出3MHz正弦波时的频谱和时域波形

在输出端加上截止频率位4MHz的2阶低通滤波器输出波形的效果,最高的混叠频谱 - 13MHz同主信号相比低了30dBc。

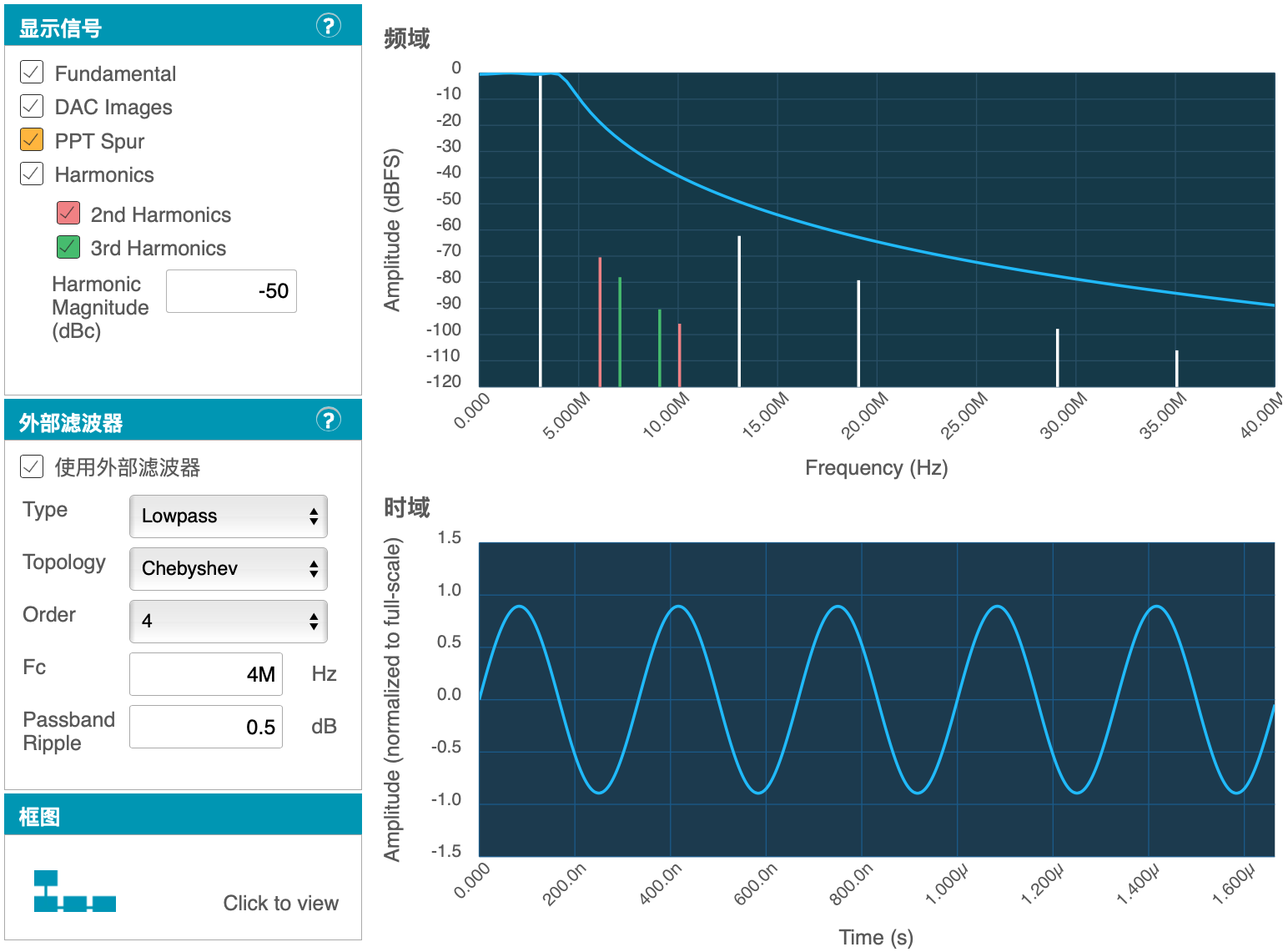

如果加入4阶截止频率为4MHz的低通滤波器,13MHz的混叠信号的能量相比于主信号低60dBc。

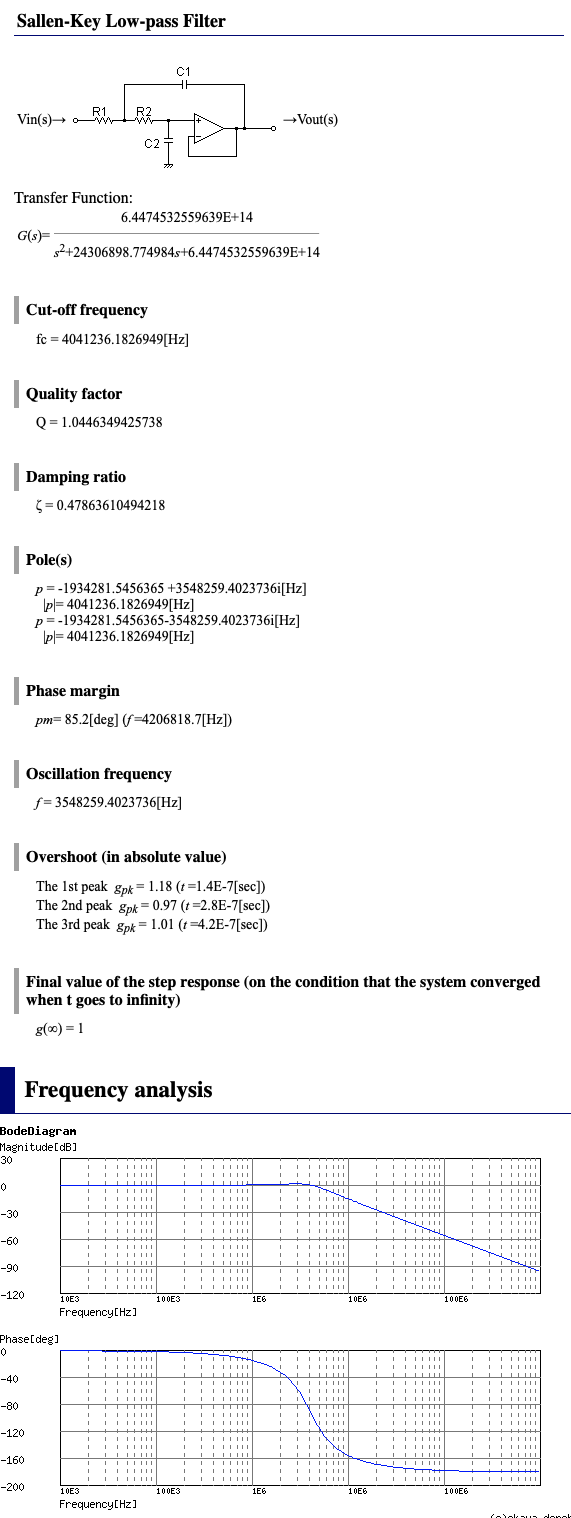

在本模块中,采用了2阶的Sallen Key有源低通滤波器,仿真的结果如下:

相关设计资料

相关器件的技术资料

-

AD9837 - 低功耗、8.5 mW、2.3 V至5.5 V可编程波形发生器

-

产品的主要功能特性:

-

数字可编程频率和相位

-

功耗:8.5 mW(2.3 V时)

-

MCLK速率:16 MHz(B级),5 MHz(A级),在本设计中我们采用了16MHz的版本 - AD9837BCPZ-RL

-

28位分辨率:0.06 Hz(16 MHz参考时钟)

-

正弦波/三角波/方波输出

-

2.3 V至5.5 V电源供电

-

三线式SPI接口

-

扩展温度范围:–40°C至+125°C

-

关断选项

-

10引脚LFCSP封装

-

-

-

SGM8061 - 500MHz,轨到轨输出的CMOS运算放大器

-

主要功能特性:

-

轨到轨输出

-

输入偏移电压: 8mV (MAX)

-

高速:

-

500MHz, -3dB Bandwidth (G = +1)

-

420V/μs, Slew Rate

-

16ns Settling Time to 0.1% with 2V Step

-

-

供电范围: 2.5V to 5.5V

-

输入电压范围: -0.2V to 3.8V with VS = 5V

-

优异的视频指标(RL = 150Ω, G = +2):

-

增益平坦: 0.1dB to 80MHz

-

差分增益: 0.015%, Diff Phase: 0.05 Degree

-

低供电电流: 8.2mA (TYP)

-

-40℃ to +125℃ 工作温度范围

-

有绿色SOT-23-5和SOIC-8两种封装,在本设计中我们采用了SOT23-5的封装

-

-

参考设计资源:

物料清单

附件下载

DDS_AD9837.pdf

用KiCad绘制的原理图 - PDF格式

DDS_AD9837_Gerber.zip

可以直接做电路板的Gerber文件,双层板,用KiCad设计,有邮票孔

DDS_AD9837.zip

KiCad设计源文件,包含了原理图、PCB布局布线文件

团队介绍

硬禾工程师团队专注于基于FPGA和嵌入式系统学习平台的开发和生态系统的建设,在过去5年里成功推出的小脚丫FPGA学习平台被全国上百所高校采用于数字电路教学实践中,并一直积极推动开源、免费PCB设计工具KiCad在高校学生及硬件工程师中的应用。

团队成员

苏公雨

与非网/硬禾学堂创始人,电子创客爱好者,15年硬件研发、设计背景。

王安然

资深硬件设计工程师、FPGA教学导师,12年硬件研发经验,主持开发了基于小脚丫FPGA的系列学习平台。

评论

0 / 100

查看更多

猜你喜欢

基于CH579的DDS信号发生器使用沁恒BLE芯片(CH579)控制AD9837从而实现手机APP控制输出信号,目前可以输出0-2MHz内的任意频率的正弦波、三角波、方波。

我叫搞事情

3044

基于小脚丫FPGA实现本地控制的DDS信号发生器本次项目使用小脚丫FPGA和电赛开发板完成了本地控制的DAC波形发生器。本项目主要分为几个部分:DDS波形时序控制模块,OLED初始化与控制模块,编码器等外设控制逻辑模块等。

curious

2211

基于AD9837的DDS信号发生器模块使用ADI公司的AD9837DDS芯片制作的信号发生器模块,通过SPI总线进行配置,板上有16MHz时钟,输出端通过SK滤波器得到最高3MHz的模拟信号

adking

161