RISC-V在FPGA系统上的移植和功能演示

项目需求

功能要求

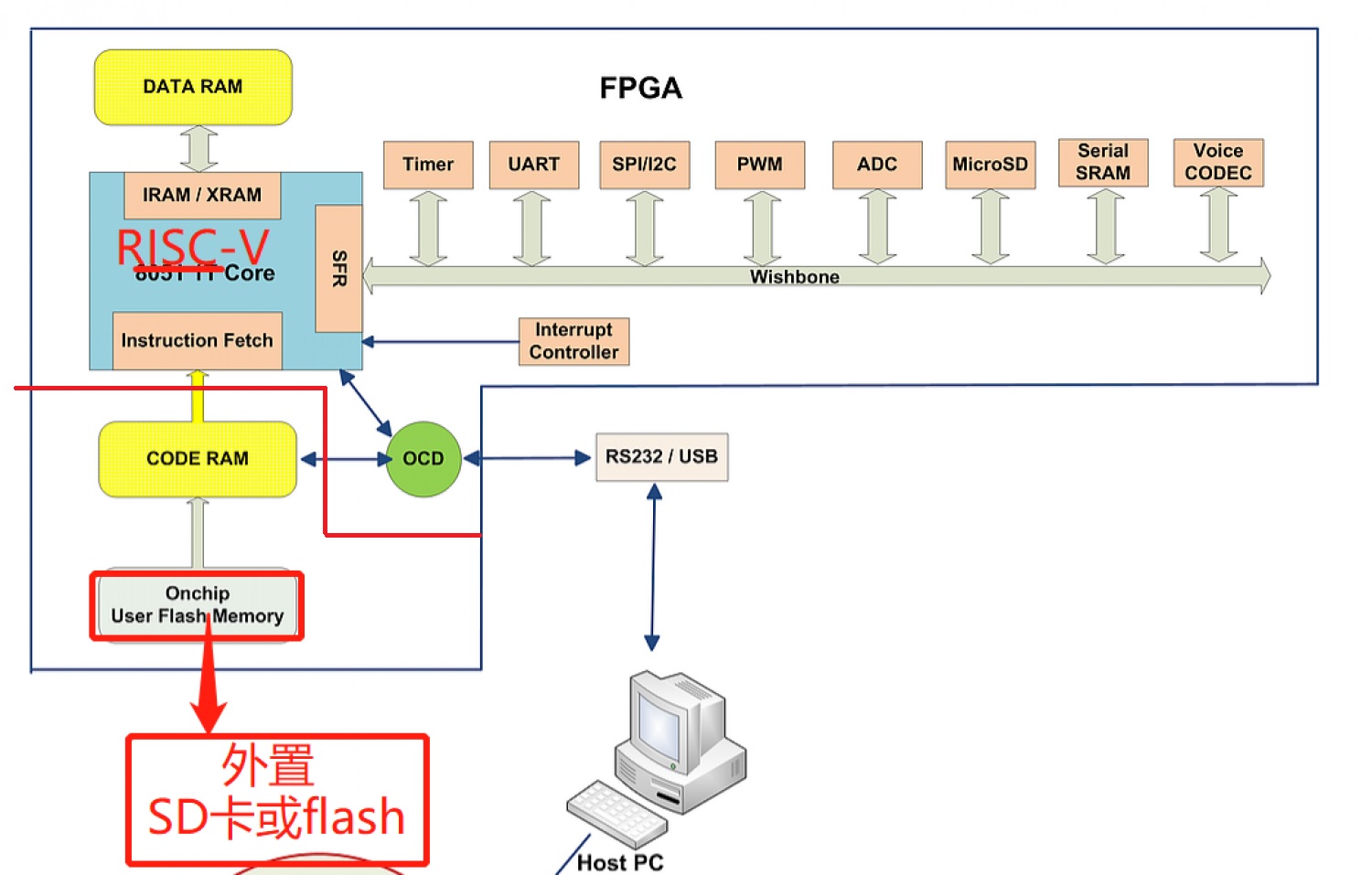

本项目的内容是在STEP CYC10开发板上移植和仿真Reindeer RISC-V CPU软核。将软核移植到FPGA平台上既可以在FPGA里面灵活地设计底层电路,又能够利用像Arduino一样的开发环境快速地开发应用程序。熟悉已有的STEP MAX10 + FP51软核移植方案中,FLASH,RAM,OCD之间的通信机制。

1.在扩展板上增加FLASH模块:搭载RISC-V软核的Intel Cyclone 10 FPGA芯片没有包含DRAM和FLASH,目前板上已有SDRAM,还没有FLASH,项目的目标是实现FLASH中代码的存放和Boost功能。

2.基于STEP CYC10功能扩展板增加外设模块:a.使用一个距离传感器,实现当有人进入感应范围时,随着距离的变化,使得LED灯的亮度也随之发生变化;b.在LCD显示屏上显示一张图片。

性能要求

* 通过以上的功能来进行RISC-V系统在FPGA上的功能演示

* 可以根据距离的远近控制LED灯的亮度

* 可以在LCD屏上显示特定的图片

* 熟悉Makefile for RISC-V

*(sketch for DRAM test)

资源要求

* 其他的LCD、LED、ADC、DAC、距离传感器均使用公司已有器件

进度要求

- 第一周:熟悉STEP CYC10开发板相关内容;选择合适的SPI-FLASH以及相关的外设元器件;熟悉Reindeer RISC-V软核的Makefile;

- 第二周:学习PCB的设计以及FPGA相关知识;完成PCB板设计;阅读FP51 OCD、RAM、FLASH数据传输相关代码。

- 第三周:学习Verilog语法以及System Verilog语法;编程设计FLASH-SDRAM接口,实现程序的存放和Boost功能;编写程序实现以上外设模块的相应功能。

- 第四周:继续修改;项目总结。

成本要求

- 新增FLASH价格:1.25元

其它要求

项目方案

方案综述:

目前RISC-V软核中嵌入了OCD (onchip debugger)模块,相当于MCU内部的硬件BOOT模块,通过外接串口同样可以实现串口一键下载。只不过程序下载到RAM区,掉电数据会丢失,如果想程序掉电不丢失还是需要将Arduino IDE 生成的.hex文件存放到到外部的FLASH中。

目前STEP CYC10开发板上已经在FPGA片外实现了SDRAM,片内的OCD模块将RISC-V的运行程序烧录到SDRAM,如前文所述,如果SDRAM下电,那么RISC-V的运行程序就丢失了。本项目的第一项任务是将RISV-V的代码经SDRAM存入外部FLASH,该任务实现之后,代码在板子下电之后也不会被擦除。

目前STEP CYC10开放板上的Boost是通过OCD模块实现,从串口读入SDRAM。本项目的第二项任务是设计FLASH Boost电路,该任务实现之后,SDRAM可以从FLASH Boost将代码送入软核运行。

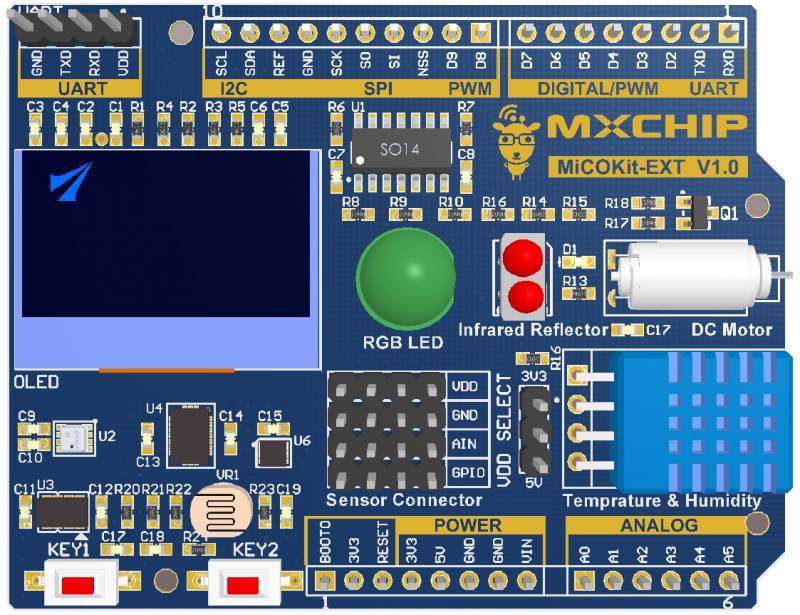

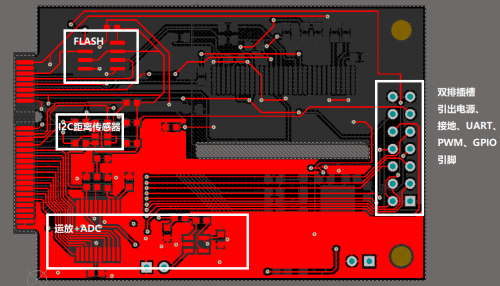

在完成代码下电不擦除的功能之后,继续完成扩展板上的功能设计,这是本项目的第三项任务。扩展板上的预置模块如上图所示,主要演示的内容包括:1. 根据距离传感器的反馈输出PWM信号调节LED灯的亮暗;2. 在LCD屏上显示图片。还预留了PWM+电机、ADC、DAC的位置。板子上的器件除了FLASH和ADC/DAC,均参考MiCOKit扩展版上的器件,具体尺寸参照器件文档(目前还没找到),需要注意的是LCD需要开槽将引脚引到背面。ADC/DAC的器件选用公司已有器件micokit-samg55原理图及生产资料.zip。FLASH器件的参数如下所示

关键元器件:

* SPI-FLASH

* LCD显示屏

实施计划:

项目实施

PCB设计

#### PCB制造

#### PCB焊接、调试

FPGA连接和Verilog编程

系统测试

项目答辩

项目进展

- 完成原理图和PCB

目前的扩展板上包含有SPI FLASH、R2R电阻网络DAC+运放、运放+ADC、距离传感器、LCD屏幕、4个GPIO引脚、2个PWM引脚、2对UART引脚、2个3.3v电压引脚、3个接地引脚。

版本1:

正面图

背面图

版本2:

正面图

3D图

原理图和PCB文件:riscv.rar

建议后续改进:扩展板上应该加上LED灯,方便程序调试。

2.BOM表:riscv_final_board.xlsx

3.完成了DAC、ADC、距离传感器、FLASH的FPGA验证

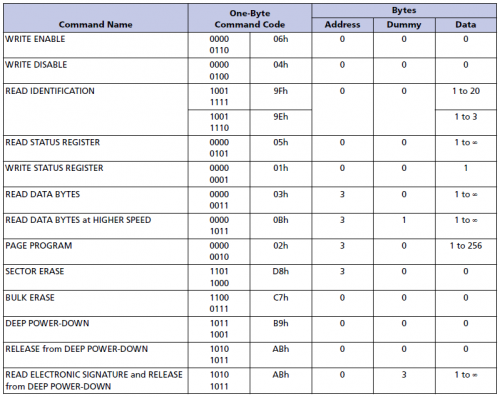

FLASH验证方案:对于FLASH内部的STATUS REGISTER进行读写操作。STATUS REGISTER中的bit4、bit3、bit2是SECTOR擦除保护控制位,可读可写。本项目选用的M25P32器件采用4线SPI,在时钟的上升沿从外部读取数据,在时钟的下降沿准备输出数据。控制命令采用“控制字+数据字节”的形式,共有13个控制命令。验证用到了WRITE ENABLE、WRITE STATUS REGISTER、READ STATUS REGISTER这三条命令。WRITE ENABLE是写使能。只有写使能执行之后才能执行WRITE STATUS REGISTER,该命令将STATUS REGISTER中的bit2、bit3、bit4置为100。READ STATUS REGISTER让FPGA读取STATUS REGISTER中的bit4、bit3、bit2的值,并将其接到LED的引脚输出。按键朝右边掰触发写,按键朝左掰触发读,最终LED[1:0]亮,LED[3]不亮,符合预期。

验证距离传感器(点击下图)

4.了解了FPGA+软核(8051,RISC-V)+高级语言编程的操作流程

参考

RISC-V软核-Reindeer_step调试笔记

在软核wishbone总线上增加PWM外设,经过跑通流水灯完成验证。

在软核wishbone总线上增加LCD模块,完成刷屏输出。

…更新中…

#### 设计文件

1.PCB版本1:

郭子钰:原理图+PCB 提取码5n4p,flash验证代码

PCB版本2:

卢凯丽:原理图 task3_5_13.pdf

2.

遇到的问题和解决过程

- 一开始对Flash片选引脚S#的功能不清楚,在原理图中直接接了低电平。但是S#其实是个控制信号,需要产生上升沿和下降沿,因此直接把它接到低电平是错误的,flash将无法工作。后来将芯片的引脚掰直,用杜邦线连接到GPIO2引脚,对齐进行电平控制。

- 对RISC-V软核理解还不够深入。目前把工具链熟悉了,后面通过读代码,改代码来加深理解。

项目参考资料

学习顺序

- 熟悉Intel Cyclone FPGA、Quartus Prime软件(Lattice MXO2 FPGA、Diamond软件)及FPGA设计流程

- 熟悉STEP CYC10开发板硬件资源

- 操作一遍FPGA + Arduino + 软核这种开发方式,在小脚丫FPGA板上玩转开源农场(FARM)——FPGA+Arduino+RISC-V+Make

- 看RISC-V相关资料,了解ReindeerStep软核内部结构,对比FP-1T 8051软核,基于FPGA使用Arduino编程的8051软核FP51-1T,主要参考外设IP - 尝试修改ReindeerStep外设并测试

- 尝试修改Reindeer Arduino IDE固件并测试

- 分工:

- RISC-V的验证和仿真的改进

- 设计基于STEP CYC10的功能扩展板以演示RISC-V系统

- sketch for DRAM test

- Makefile for RISC-V

FPGA

硬件平台

- STEP FPGA核心板

- STEP CYC10开发板

参考文档

- [1] Intel Cyclone 10 LP Device Overview (C10LP51001), Intel Corporation, 05/08/2017

- [2] Intel Cyclone 10 LP Device Datasheet (C10LP51002), Intel Corporation, 05/07/2018

- [3] Intel Cyclone 10 LP Core Fabric and General Purpose I/Os Handbook (C10LP51003), Intel Corporation, 01/24/2019

- [4] UltraFast High-Level Productivity Design Methodology Guide, UG1197 (v2018.3) , Xilinx Inc., December 5, 2018

- [5] Building Embedded Systems, Programmable Hardware, Changyi Gu, Apress Media LLC, 02/2016

- [6] Synchronous Resets? Asynchronous Resets? I am so confused! How will I ever know which to use?, Clifford E. Cummings and Don Mills, SNUG (Synopsys Users Group) San Jose, 2002

- [7] Asynchronous & Synchronous Reset Design Techniques - Part Deux, Clifford E. Cummings, Don Mills, Steve Golson, SNUG Boston 2003

- [8] A Review on Clock Gating Methodologies for power minimization in VLSI circuits, Harpreet Singh1, Dr. Sukhwinder Singh, International Journal of Scientific Engineering and Applied Science (IJSEAS) – Volume-2, Issue-1, January 2016

- [9] Crossing the abyss: asynchronous signals in a synchronous world, By Mike Stein, Paradigm Works, EDN Magazine, Jul 24, 2003

- [10] Keep metastability from killing your digital design, by Debora Grosse, Unisys, EDN Magazine, June 23, 1994

- [11] Practical design for transferring signals between clock domains, By Michael Crews and Yong Yuenyongsgool, Philips Semiconductors, EDN Magazine, Feb 20, 2003

- [12] Simulation and Synthesis Techniques for Asynchronous FIFO Design, Rev 1.2, Clifford E. Cummings, Sunburst Design, Inc., SNUG (Synopsys User Group Conference), San Jose, 2002

- [13] CMOS Digital Integrated Circuits - Analysis and Design (3rd Edition), Sung-Mo Kang, Yusuf Leblebici, McGraw-Hill Higher Education, 2003

- [14] Intel 8080 Microcomputer Systems user's Manual, Sep 1975

- [15] MC6800 8-bit Microprocessing Unit (MPU), Motorola Semiconductor Products Inc. 1984

- [16] M6800 Programming Reference Manual 1st Edition, Motorola, Inc. 1976

- [17] Verilog Digital Computer Design - Algorithms into Hardware, Mark Gordon Arnold, University of Wyoming, Prentice Hall PTR, 1999

RISC-V

- Reindeer RISC-V CPU软核Reindeer及Reindeer_Step

- [1] RISC-V from Wikipedia (https://en.wikipedia.org/wiki/RISC-V)

- [2] RISC-V Geneology, Tony Chen and David A. Patterson, Electrical Engineering and Computer Sciences, University of California at Berkeley, Jan 24, 2016

- [3] ARM Kills Its RISC-V FUD Website After Staff Revolt,by Joel Hruska, EXTREMETECH Jul 12, 2018

- [4] PulseRain FP51-1T Microcontroller, Technical Reference Manual. (Doc#TRM-0923-00001, Rev 1.0.0). PulseRain Technology, LLC, Sep 2017

- [5] The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Document Version 2.2, Editors Andrew Waterman and Krste Asanović, RISC-V Foundation, May 2017

- [6] The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10, Editors Andrew Waterman and Krste Asanović, RISC-V Foundation, May 2017

- [7] The RISC-V Reader: An Open Architecture Atlas, by David Patterson and Andrew Waterman, Strawberry Canyon, November 7, 2017

- [8] Design of the RISC-V Instruction Set Architecture, by Andrew Shell Waterman, A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate Division of the University of California, Berkeley, Spring 2016

- [9] System and method for fusing instructions, Ronny Ronen, Alexander Peleg and Nathaniel Hoffman, Intel Corp, United States Patent No: US6675376B2, 12/29/2000

- [10] ARM Cortex-A Series Programmer’s Guide for ARMv8-A, Version: 1.0, ARM Limited, Mar 24, 2015

- [11] Building Embedded Systems, Programmable Hardware, Changyi Gu, Apress Media LLC, 02/2016

- [12] JEDEC from Wikipedia (https://en.wikipedia.org/wiki/JEDEC)