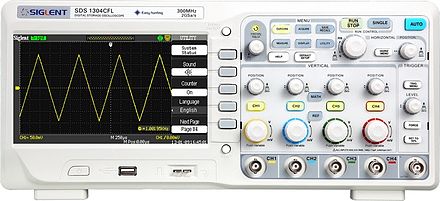

示波器是电子工程师的眼镜,它同万用表、信号发生器、电源一起号称工程师四大件。随着技术的发展,当前使用的几乎所有的示波器都是数字示波器,其核心就是将被测量的模拟信号通过高速的A/D变换器变换成数字信号,在显示屏幕上以时域波形的方式显示出来。不同价位的示波器主要差别在于取样频率、波形的存储深度以及内置的数字信号处理功能。

图1 通用的数字波器

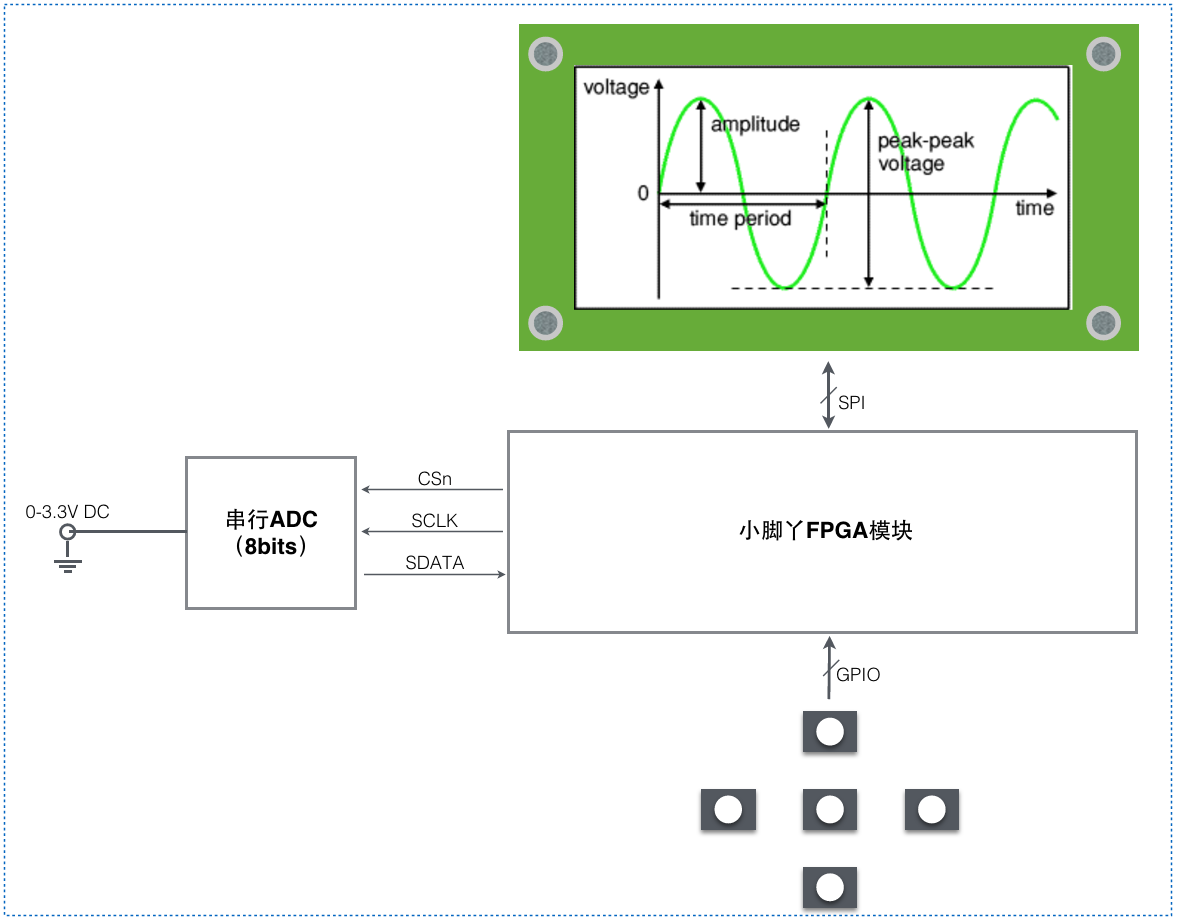

为了更深入地掌握示波器的工作原理,我们在本项目中采用串行ADC对模拟信号进行量化,通过FPGA内部的存储器进行采样数据的缓冲,再通过LCD将波形显示出来。

项目要求:

- 显示屏128*64,SPI接口

- 通过按键控制波形的左右移、放大、缩小

- 采样频率>1Msps

- 被测模拟信号幅度0-3.3V

- 存储深度:1KByte

- 能够测量频率和幅度并在LCD屏上以文本的方式显示出来

- 具有直流电平触发功能,触发电平可以在0-3.3V之间进行调节

实现原理:

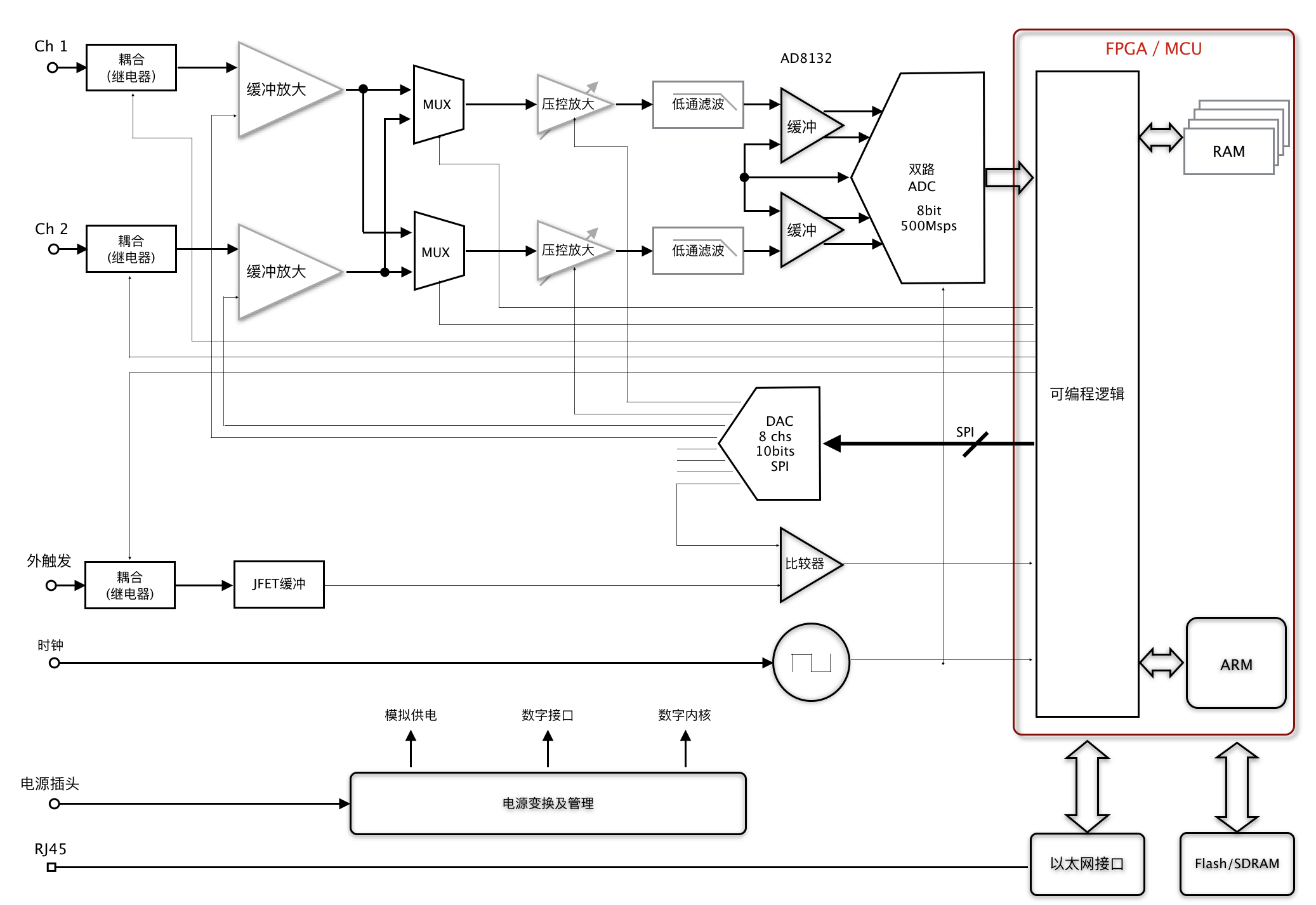

一个典型的商用示波器(以普通的双通道数字示波器为例),从电路角度主要有如下几个部分:

- 最核心的部分 - 模/数转换(ADC):这部分的功能负责将待测的模拟信号进行量化,转换成数字信号,在数字域进行处理。ADC主要的指标有三个

- 转换率 - 根据奈奎斯特定律,ADC的转换速率至少需要达到被测模拟信号带宽的2倍以上,为了更好地重现被量化的波形,一般选择的ADC的转换率是被测量的模拟信号最高带宽的5倍以上。比如被测的模拟信号最高带宽为100MHz,我们可以采用500Msps的ADC进行量化

- 分辨率 - ADC的分辨率(ADC的位数)越高,量化误差越低,转换到数字域以后的被测信号的信噪比越高

- 模拟带宽 - ADC内部模拟部分的带宽

- 模拟信号调理 - 能够测试几mV到几十V、带宽从DC到100MHz的交流或直流的模拟电压信号,因此需要模拟信号调理电路,以保证信号带宽的前提下,能够实现所需要的被测信号的动态范围

- 微处理器部分 - 处理键盘/编码器输入、波形显示输出以及网络通信等

- 电源 - 提供以上电路所需要的各组电源,比如模拟电路所需要的+/-12V供电电压;数字电路接口所需要的+3.3V电压;MCU以及FPGA所需要的内核电压(1.5V、1.2V或更低),电源电路的设计要满足系统的功能、性能、转换效率、散热等各方面的要求

图2 双通道示波器的典型构成框图

在我们的训练中,我们通过一个简化的系统尽可能地理解示波器的基本原理、基本电路构成以及关键的技术指标的来历,主要做了如下简化:

- 被测信号简化为0-3.3V,带宽为DC-20KHz(音频信号的频率范围)的直流耦合的信号,因此在学习板上没有模拟信号调理电路部分,直接将待测的模拟信号送给ADC的输入端

- 只支持一个通道

- 采用串行ADC:8位精度、1Msps转换速率、SPI串行数据接口

- 存储深度 - 1KByte,通过FPGA内部的块RAM来实现

- LCD显示:128*160分辨率的图形化LCD屏

- 控制按键:上、下、左、右

- 触发 - 在FPGA内部实现

图3 用小脚丫FPGA模块和串行ADC、串行LCD屏构成的简单示波器方框图

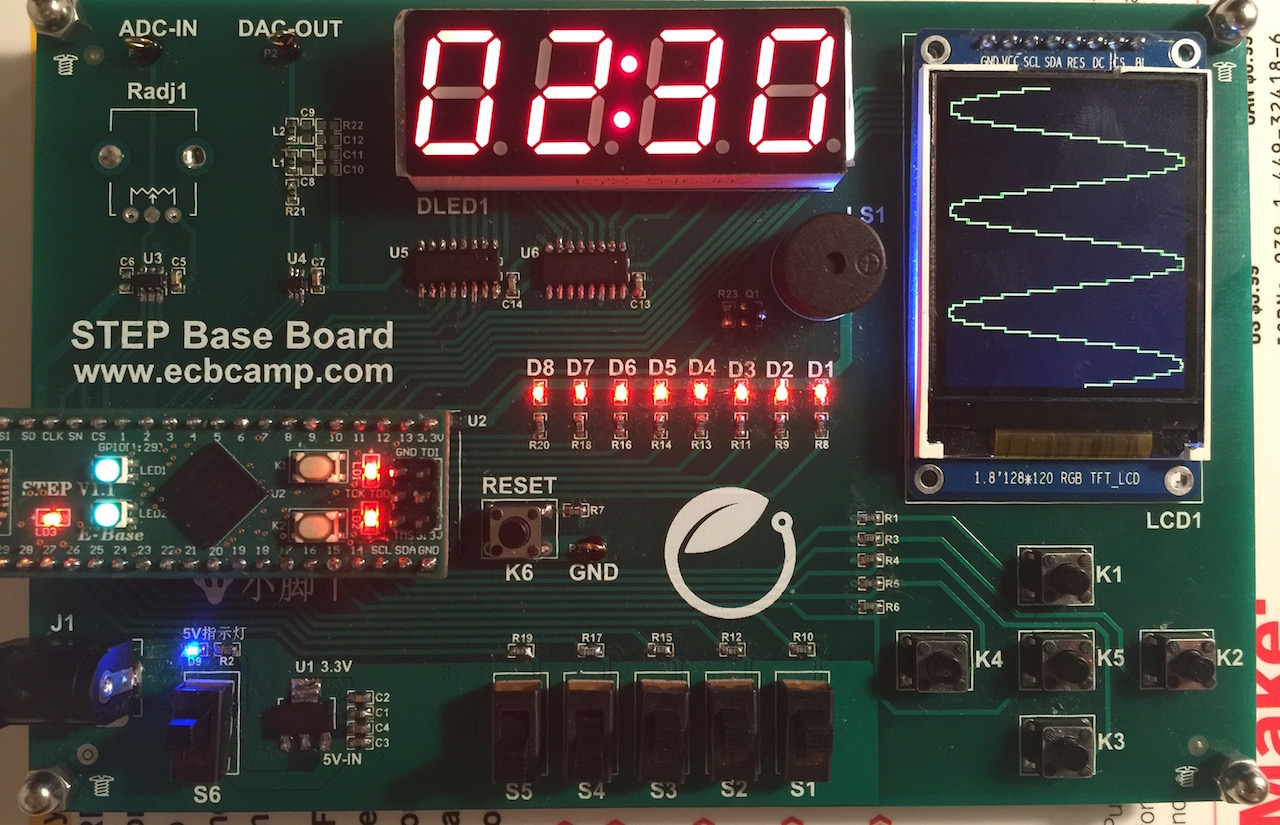

图4是我们基于小脚丫/扩展板上做成的简易示波器的实物图,可以看到LCD屏上显示的正弦波波形,改变输入端的信号大小、频率,可以看到LCD屏上的信号幅度和间隔会发生相应的变化

图4 用小脚丫FPGA做的简易示波器实物