Σ-Δ型ADC

从概念上讲,Σ-Δ转换器的数字特性多于模拟特性,但这并未降低Σ-Δ型ADC的模拟部分的重要性。五阶Σ-Δ调制器的设计(例如在双通道18位ADC AD1879中)绝不是轻而易举的小事一桩,数字滤波器同样如此。Σ-Δ转换器本质上是一种过采样转换器,尽管过采样只是成就整体性能的多种技术中的一种。总的说来,Σ-Δ转换器是利用分辨率非常低(1位)的ADC以极高采样速率对模拟信号进行数字化处理。但通过将过采样技术与噪声整形和数字滤波技术结合使用,使有效分辨率得以提高。然后,通过抽取过程降低ADC输出端的有效采样速率。1位量化器和DAC的线性度使Σ-Δ型ADC表现出极佳的微分和积分线性度,并且不必像其它ADC架构那样需要调整。

它的特点:

- 混合信号VLSI芯片的理想拓扑结构

- 过采样

- 利用Σ-Δ调制器进行噪声谱整形

- 数字滤波

- 抽取

- 可实现16位及更高的分辨率

原文来自TEARING INTO DELTA SIGMA ADC’S Σ-Δ型ADC涉及到几种不同技能的组合:

- 过采样

- 噪声成型

- 数字滤波

这些功能并不需要多个芯片来完成,目前单颗Σ-Δ型的ADC芯片做的非常小巧。

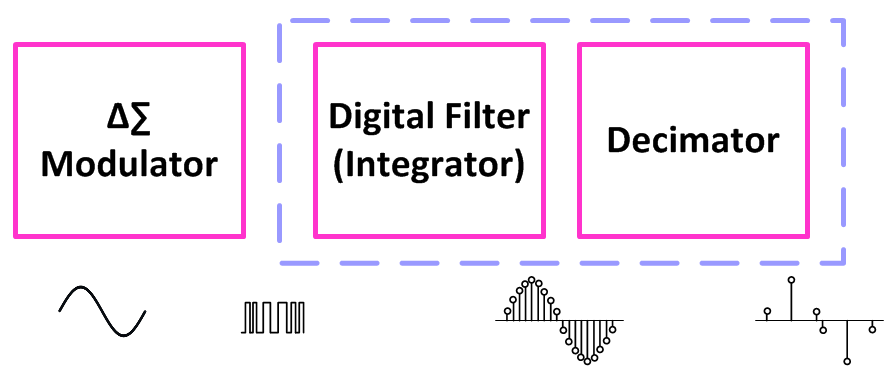

1. Delta-Sigma框图

下面是Delta Sigma ADC的框图,它包含三个部分:

- Delta Sigma调制 - 调制器的作用是将输入的模拟信号转换为一位的调制数据流

- 积分器 - 将这个1位数据流累积成能够代表信号平均值的多位数值,并附带其它额外信息

- 抽取滤波器 - 将额外不需要的信息去除掉,仅保留最精准的输出

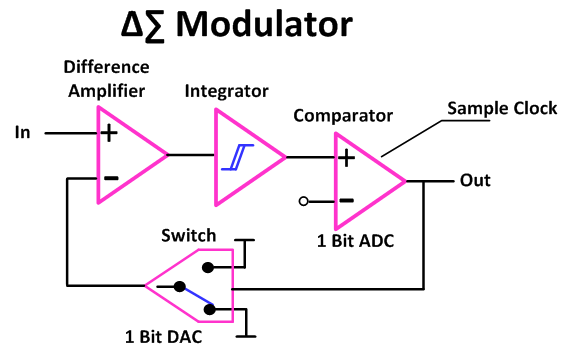

1.1 Delta Sigma调制器

它是ADC的核心,负责将输入的模拟信号数字化,并通过过取样以及噪声成型技巧来降低噪声。

从框图中可以看出,Delta Sigma调制器包含了一个差分放大器,用以累加输出的反馈信号; 一个积分器用于噪声成型 - 在低频段移除掉噪声;一个1bit的比较器以及一个开关将上一个取样点的结果取反以后有效地反馈回去。

由于反馈路径,数字输出表示样本之间信号的差异。

它是ADC的核心,负责将输入的模拟信号数字化,并通过过取样以及噪声成型技巧来降低噪声。

从框图中可以看出,Delta Sigma调制器包含了一个差分放大器,用以累加输出的反馈信号; 一个积分器用于噪声成型 - 在低频段移除掉噪声;一个1bit的比较器以及一个开关将上一个取样点的结果取反以后有效地反馈回去。

由于反馈路径,数字输出表示样本之间信号的差异。

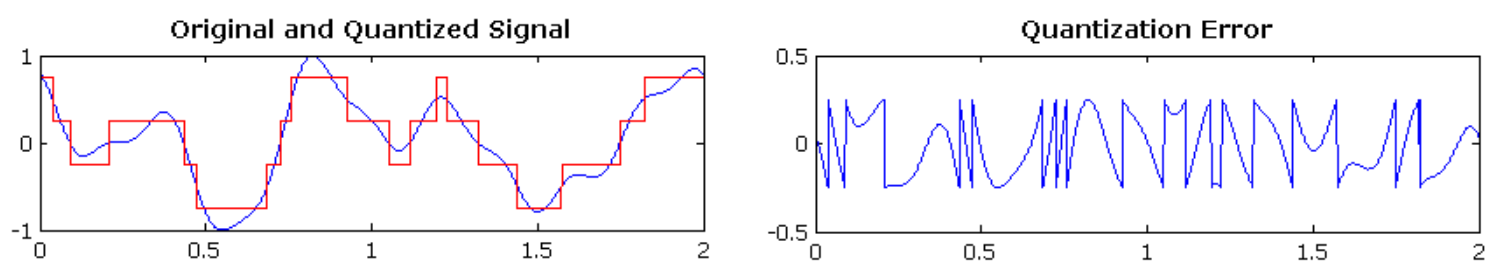

1.2 量化噪声

任何ADC中,由于不准确的量化过程导致的噪声或误差,称之为量化噪声。

ADC的分辨率越高,噪声越小,从数学角度我们可以给出ADC等效位数和信噪比的关系:

ENOB = (SNR-1.76)/6.02dB

ADC的分辨率越高,噪声越小,从数学角度我们可以给出ADC等效位数和信噪比的关系:

ENOB = (SNR-1.76)/6.02dB

SNR = (6.02 x N)+ 1.76db

1.3 过取样

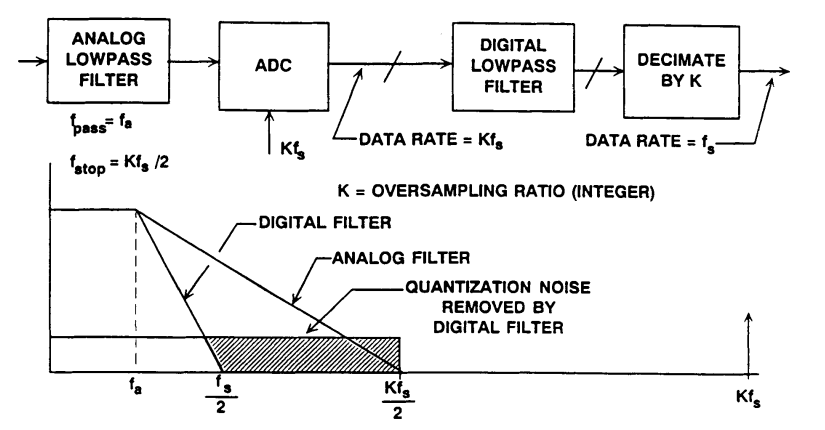

采用模拟和数字滤波进行过采样

降低噪声比较有效的一种方式是提高采样频率,这种技术叫过取样,它能够将量化噪声扩展到更宽的频谱范围,后面的滤波器可以将带外的噪声滤除掉。虽然它不能彻底去掉噪声,但是能够成比例地降低靠近我们信号的噪声的幅度。一个简单的规则 - 采样频率扩大4倍,有效位数增加一位。

1.4 噪声成型

Delta Sigma使用1级或2级积分器来做噪声成型,我们可以使用ADC的ADC评估软件来显示噪声成型的效果。

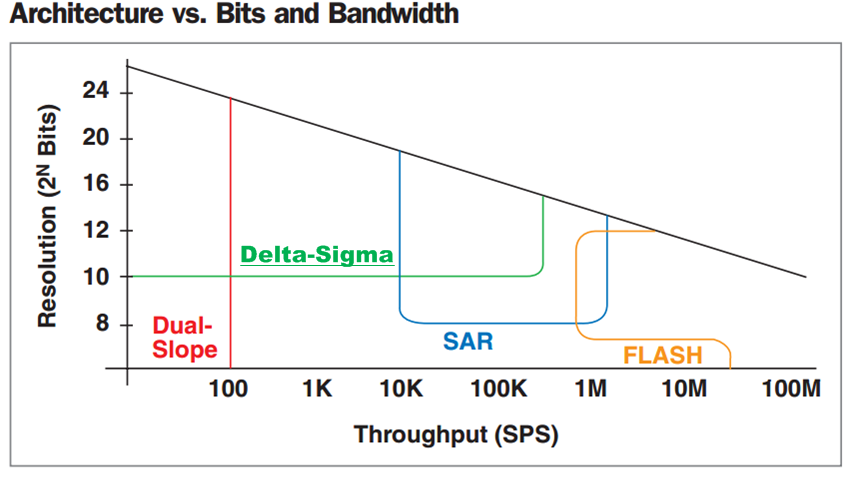

2. 应用

低频测量应用Σ-Δ型ADC工业过程控制、电子秤、温度和压力测量仪表等应用要求ADC能以16位或更高的分辨率对低频信号(通常小于10Hz)进行数字化处理。过去,这种需求几乎完全由积分(或双斜率)ADC来满足。Σ-Δ转换器提供了另一种有吸引力的选择。除了成本更低和尺寸更小外,低频Σ-Δ型ADC还能提供片上数字滤波以及系统和自校准功能。采样速率允许处理最高10Hz带宽的信号,而且与传统积分ADC相比,Σ-Δ型ADC能在宽得多的频率变化范围内保持电力线频率抑制特性。双斜率ADC的电源抑制特性取决于瞬时线路频率变化,原因是采样时钟与线路频率同步。