**这是本文档旧的修订版!**

DDS+PWM产生任意波形

工作原理

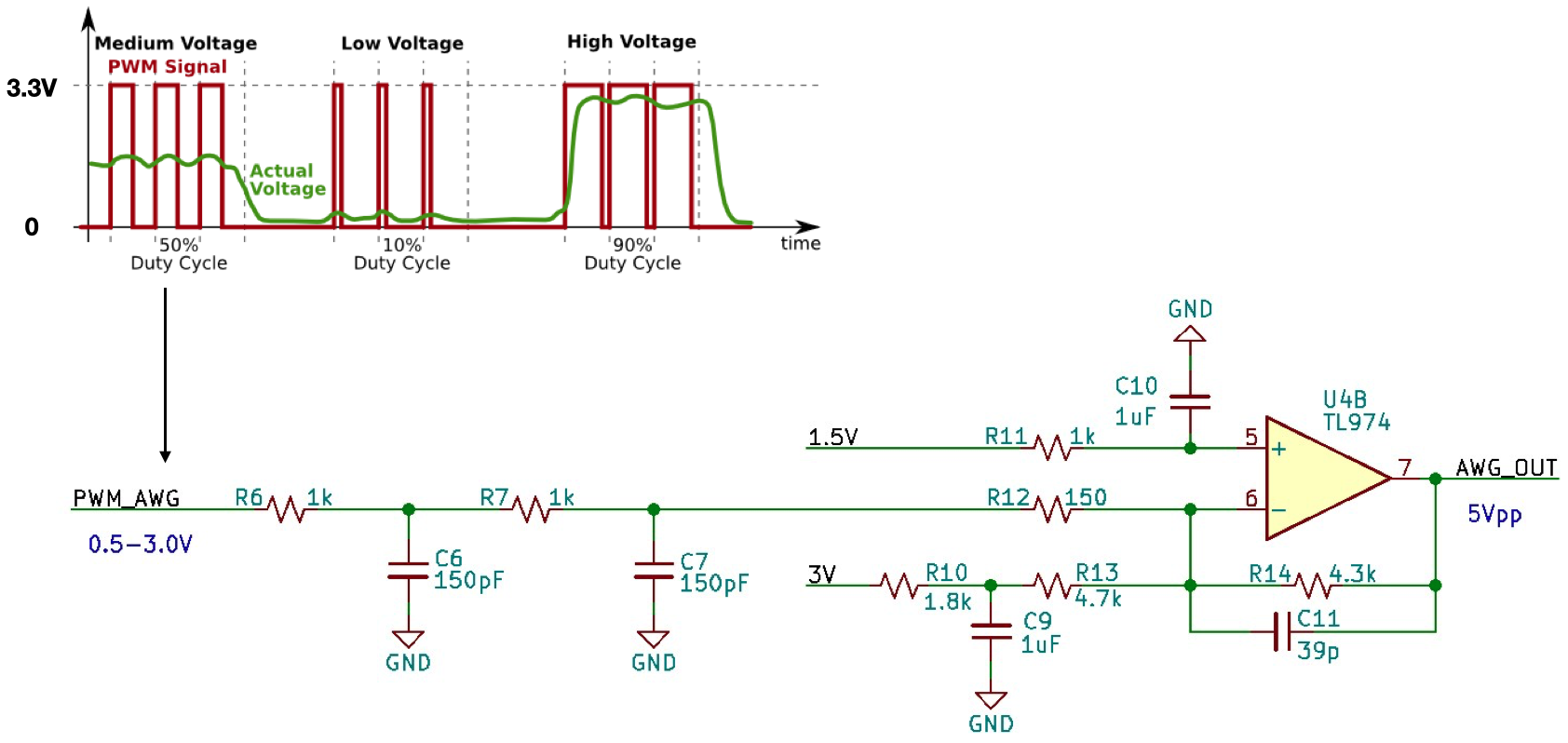

模拟电路

任意波形发生器模拟电路部分原理图

通过调节PWM的占空比(0.5V/3.3V ~ 3V/3.3V)得到等效幅度为0.5V - 3V之间的模拟信号,幅度变化的范围为2.5V,要得到幅度为5Vpp的模拟信号,则放大器的增益设定为G = 2: 也就是在电路原理图中放大器的增益为:R14/(R6+R7+R2) = 2 取R14 = 4.3KΩ,则R6+R7+R2 = 2.15KΩ PWM波形的中间值为(0.5V+3.0V)/2 = 1.75V,因此:

- 在PWM的输出为1.75V的时候,运算放大器的输出应为0V

- PWM的输出为0.5V的时候,运算放大器的输出为2.5V

- PWM的输出为3V的时候,运算放大器的输出为-2.5V

由此直流偏移的要求可以得到R10 + R13 = 6.5KΩ 同时R6、C6,R7、C7以及R14、C11共同构成低通滤波器。

能够生成模拟信号的最高频率 取决于PWM的主时钟频率,我们目前用的FPGA的输入时钟为12MHz,使用内部PLL以后可以得到12MHz倍数的时钟频率,最高可以到400MHz,我们取比较安全的中间值192MHz(12MHz * 16)作为PWM的主时钟。 假设DDS波表为10位精度(一般DDS信号发生器的精度,作为简易的口袋仪器,对性能指标要求不高,8位也能够满足要求),则对应于一个模拟电压值的PWM周期为192MHz/1024 = 155KHz 如果通过10个点

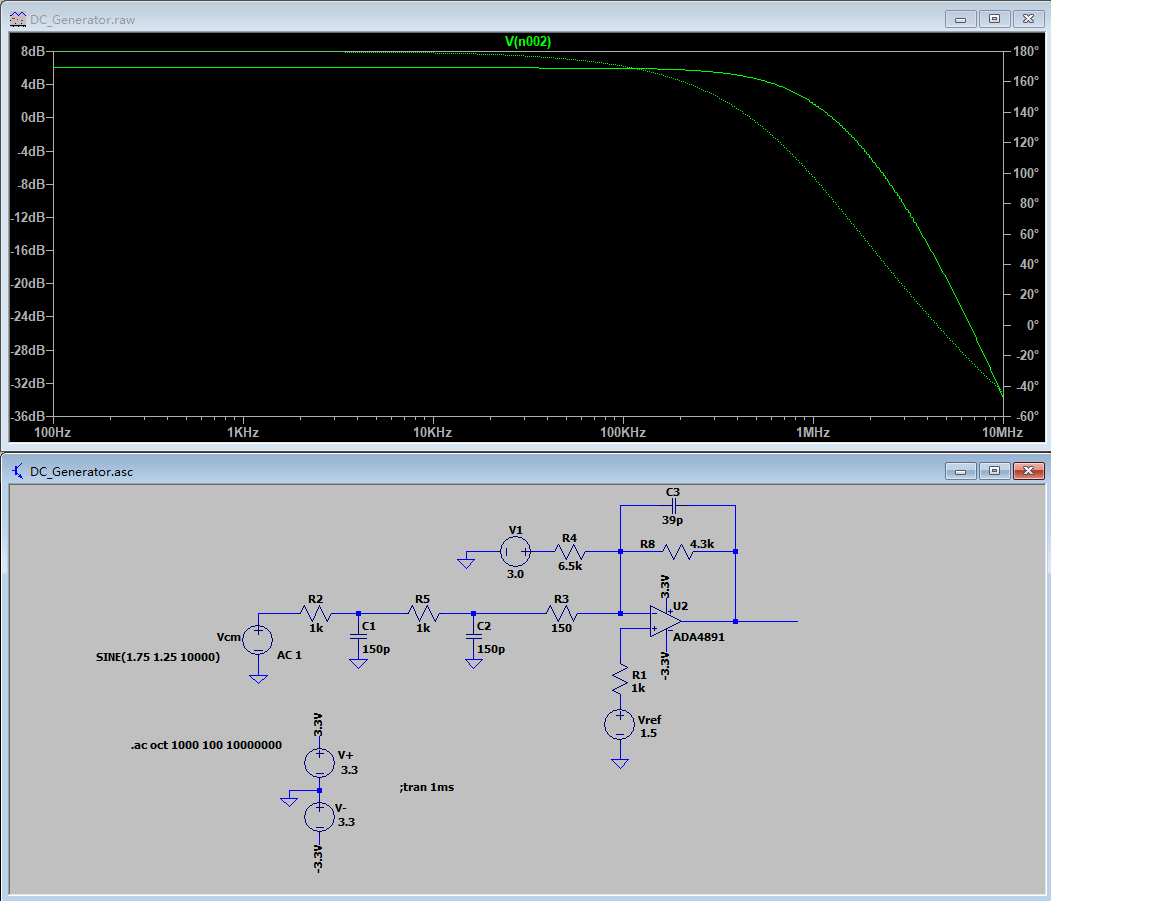

任意波形发生器模拟电路部分的仿真 - 频率响应(100Hz- 10MHz)

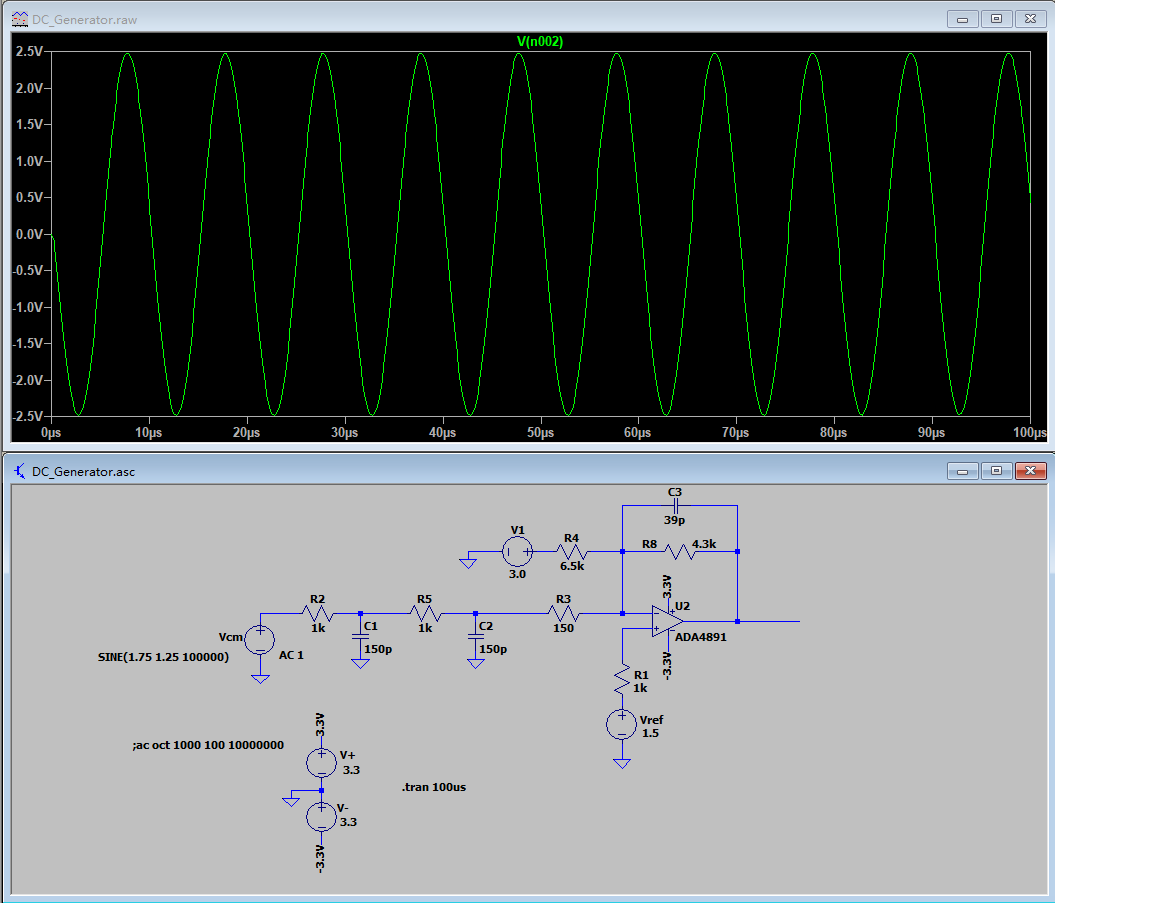

任意波形发生器模拟电路部分的仿真 - 波形(100KHz正弦波)