**这是本文档旧的修订版!**

使用Verilog来编程FPGA

1. 逻辑

FPGA是依赖数字逻辑的数字器件,计算机硬件使用的是数字逻辑,每一个计算,屏幕上每一个像素的呈现,音乐轨的每一个note都是使用数字逻辑构成的功能块来实现的。 虽然多数时候,数字逻辑是抽象的数学概念,而不是物理电子,逻辑门以及其它的数字逻辑器件则是由刻蚀在集成电路上的晶体管来实现的。对于FPGA来讲,可以通过绘制逻辑门构成的电路,将这些门映射到FPGA的通用门上,并将它们连接起来以实现你设想的逻辑设计。 另外一种方式是,使用Verilog(或其它的)硬件描述语言来实现逻辑。 你依然可以购买能够实现小数量逻辑门的器件,比如7400,内部只有4个二输入与非门,然而这些器件只是为了维护一些古老的系统或用于教学。

逻辑门

逻辑门有输入和输出,这些数字输入和输出可以是“高”或者“低”, 无论是输入端还是输出端,所谓的“低”指的是接近于0V(地)的电压,而“高”一般是超过提供给该逻辑器件的供电电压一半以上的电压,给FPGA提供的电压一般为1.8V、3.3V或着5V中的一个,多数的FPGA的工作电压范围有一定的冗余度,有些FPGA允许在一个器件中存在多个逻辑电压.

非门(NOT Gate)

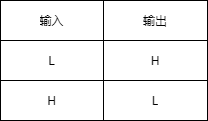

最简单的门就是非门(有时又被成为反相门),它有一个输入和一个输出,如果输入为高电平,输出则为低电平,反之亦然。图1.1 为一个非门的原理图符号,表1.1 为其真值表(列出针对各种输入类型得到的输出结果)

图1.1 一个非门

为描述逻辑门或一组逻辑门如何工作,我们一般使用“真值表”,它指定了针对不同的输入信号以及输出信号的组合,经过该逻辑以后的输出值。对于一个非门,表1.1即为其真值表。H(或1)和L(或0)用以表示“高”电平和“低”电平。

表1.1 一个非门的真值表

如果你将一个非门的输出连接到另一个非门的输入端,输出的结果将为输入的信号。

图1.2 两个非门串联

与门(AND Gate)

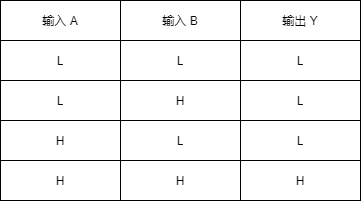

顾名思义,一个与门如果其所有的输入端都为高电平的时候,其输出为高电平。图1.3 为2输入与门的符号,表1.2为与门的真值表。

或门(OR Gate)

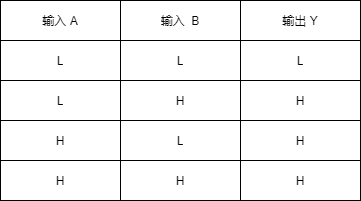

或门的任何一个输入端为高电平,其输出端都会变为高。图1.4为一个双输入或门的符号,表1.3为其真值表。

图1.4 一个或门

表1.3 一个或门的真值表

图1.3 一个与门

表1.2 一个与门的真值表

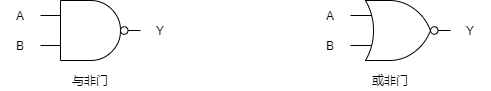

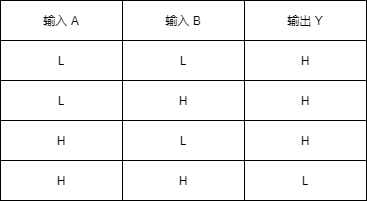

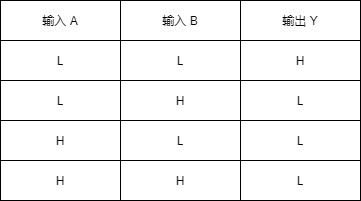

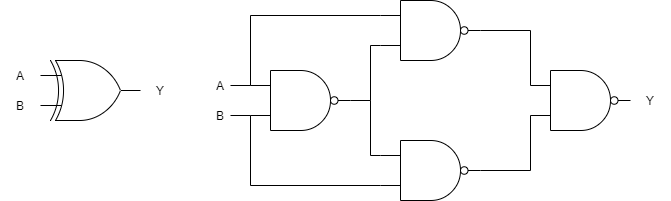

与非门(NAND Gate)和或非门(NOR Gate)

图1.1中非门符号的输出端一个小圆圈表示门的反相功能,一个与非门(与后非)就是一个与门再加一个输出端的反相器构成;或非门为一个或门再加一个输出端的反相器构成。图1.5显示了这两种门的符号,表1.4和表1.5分别为这两种门的真值表。

图1.5 一个“与非门”和“或非门”

表1.4 一个“与非门”的真值表

表1.5 一个“或非门”的真值表

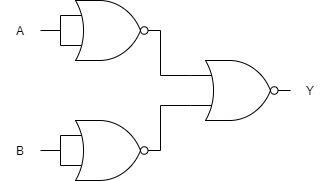

与非门和或非门都是非常通用的门,因为只需要反相它们的输入端或输出端就可以构成其它任何一种门,另外你可以用与非门或着或非门构成非门,只需要将两个输入信号连接在一起就可以。例如图1.6中你可以用3个或非门构成一个与门。

图1.6 用3个“或非门”构成一个“与门”

De Morgan定律

图1.6的设计利用了逻辑定律中的De Morgan定律 - 将两个输入端“与”后的结果进行取反,和先将两个输入端进行取反以后再“或”得到的结果是一样的。在图1.6中,两个输入端信号先被由“或非门”构成的“非门”取反以后进行“或”操作,再对输出的结果取反。

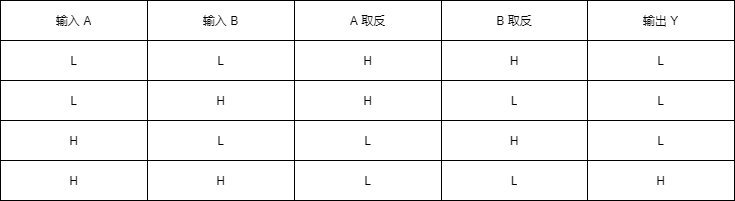

表1.6 用多个异或门构成一个与门的真值表

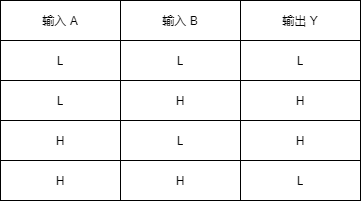

- 异或门(XOR Gate) 前面讲到的“或门”是一种包容性的或,两个输入端A、B只要任何一个为高电平或者两个都为高电平,其输出端就为高电平。但也存在这样一种排斥性的“或”,称之为异或,只有其输入端的电平不同(无论哪个信号是高还是低),其输出端才为高电平。异或门非常有用,可以用来比较输入信号。

二进制

用逻辑实现的“加法”

触发器 - Set-Reset触发器

移位寄存器

二进制计数器

总结

2. FPGA

FPGA是如何工作的?

小脚丫FPGA板

软件设置 - 安装Diamond/Quartus

项目文件

总结

3. 图形化设计逻辑

一个数据选择示例

- 第一步:创建一个项目

- 第二步:创建一个新的原理图

- 第三步:添加一个逻辑符号

- 第四步:连接各个门

- 第五步:添加输入输出(IO)标记

- 第六步:创建一个用户约束文件

- 第七步:生成.bit文件

- 第八步:编程你的板子

- 测试结果

一个4位计数器示例

- 绘制原理图

- 实现约束文件

- 测试计数器

总结

介绍Verilog

模块

Wires,Registers,Buses

并行执行

数值的格式

使用Verilog来实现数据选择

使用Verilog来实现计数器

同步逻辑

总结

4. 模块化Verilog

一个7段译码器

按键消抖

复用的7段数码管和计数器

- 项目结构

- Display7seg

- Counter_7_seg

- 用户约束文件

- 向模块导入源代码

- 设置顶层模块

- 3-digit版本

- 测试

总结

5. 定时举例

状态机

状态机设计

硬件

- 你需要 —

- 结构

模块

用户约束文件

定时模块

- 输入和输出

- 按键

- 报警模块Instance

- 为时间和显示建模

- 状态机实现

测试

总结

6. PWM和伺服电机

脉宽调制

一个PWM模块

- PWM模块的输入和输出

- PWM模块的测试程序

- 试一下

伺服电机

硬件

- 你需要的 —

- 构建

一个伺服模块

总结

7. 音频处理

简单的音调发生器

从小脚丫FPGA上声音输出

- 一个通用的音调/频率发生器

- 音调模块

- tone_tester模块

- 测试

播放一个音频文件

- 音频文件

- RAM

- wav_player模块

- 测试

- 准备好你的声音

总结

8. 视频处理

VGA

VGA的时序

画一个长方形

- 一个VGA模块

- VGA和小脚丫FPGA

移动物体

一个存储器映射的显示

- 准备一个图片