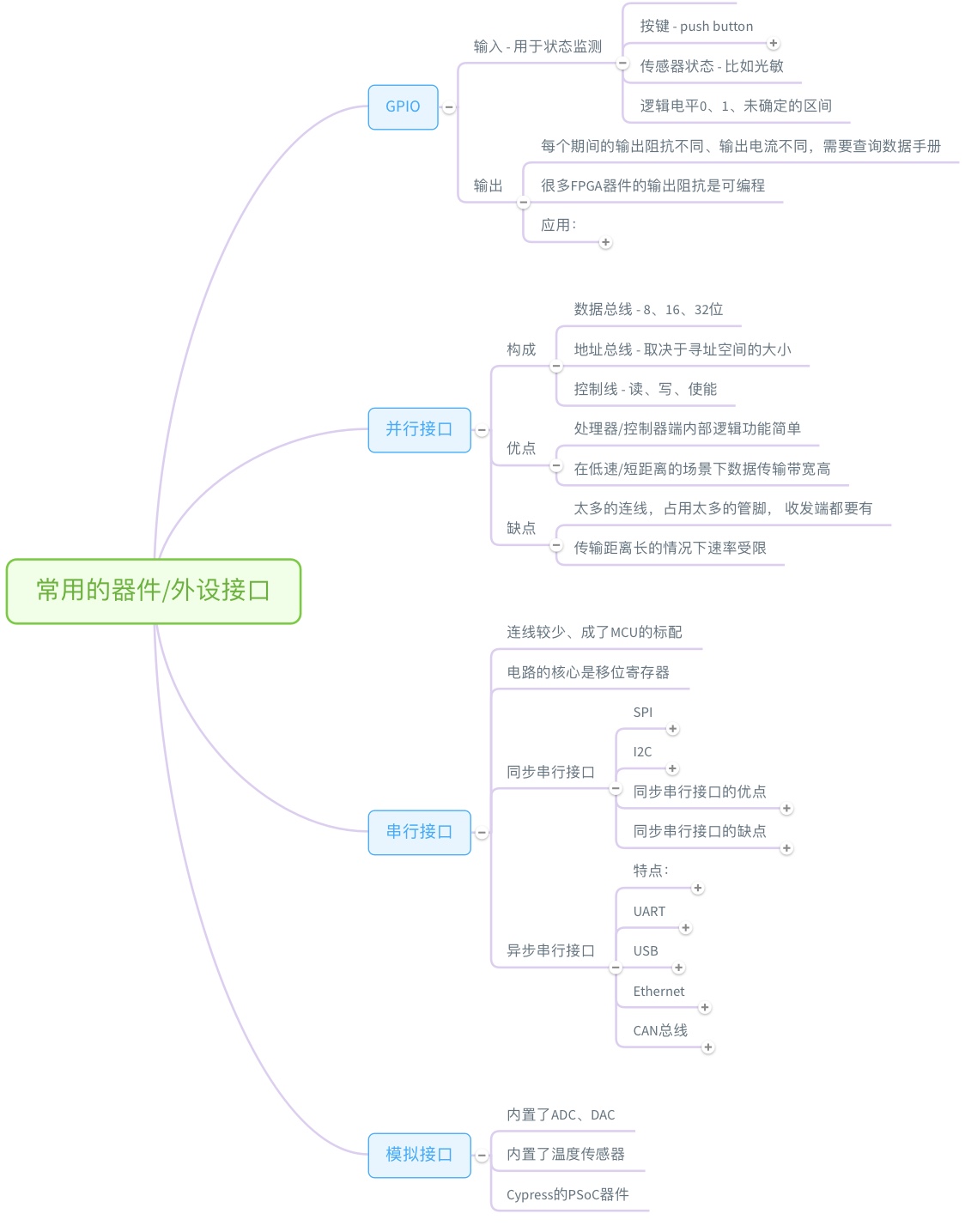

常用的器件/外设接口

GPIO

输入 - 用于状态监测

- 开关 - switch

- 按键 - push button

- 消抖动

- 传感器状态 - 比如光敏

- 逻辑电平0、1、未确定的区间

输出

并行接口

构成

- 数据总线 - 8、16、32位

- 地址总线 - 取决于寻址空间的大小

- 控制线 - 读、写、使能

优点

- 处理器/控制器端内部逻辑功能简单

- 在低速/短距离的场景下数据传输带宽高

缺点

- 太多的连线,占用太多的管脚, 收发端都要有

- 传输距离长的情况下速率受限

串行接口

连线较少、成了[[MCU]]的标配

电路的核心是移位寄存器

同步串行接口

-

- Serial Peripheral Interface - 串行外设接口

- 高速(50Mbps)、同步、全双工(SCLK、MISO、MOSI、nCS)

- 主、从结构,1主n从,靠nSS(或nCS)来寻址不同的外设

- 根据时钟的极性和相位有4种工作模式,收发端要一致

- 广泛应用在

- 传感器

- 信号调理

- 高速串行接口的ADC或DAC

- 优点:

- 简单、方便、低成本

- 用MCU指令或FPGA的逻辑来实现比较容易

- 局限性:

- 没有来自接收端的应答确认

- 没有寻址机制,多个从设备需要多个片选信号,占用太多管脚

- 没有纠错的机制

-

- Inter-Integrated Circuit,短距离的IC之间的连接

- 起源于Philips公司为其音、视频器件开发的一种总线

- 半双工、同步串行接口

- 只需要两根线(SCL、SDA),具有寻址和应答功能

- 两根线都需要上拉电阻才能正常工作

- 多个从设备连接时的电容效应会影响到传输速率

- 每个节点都可以做主/从,每个从设备都有一个地址

- 广泛应用在:

- 低速传感器接口

- 低速串行接口外设的配置

- 优点:

- 物理连接简单,只需要2根线,可以配置更复杂的网络,增减节点比较方便

- 可靠性相对较高

- 局限性

- 速度较慢

- 数据不够安全

- 很难应用在医疗、汽车和高可靠的应用中

- 用MCU代码或FPGA逻辑实现相对于SPI复杂度高

- 同步串行接口的优点

- 逻辑实现简单

- 时钟频率灵活

- 同步串行接口的缺点

- 每个数据传输需要一个多余的时钟信号线(SPI的SCLK或I2C的SCL)

- 时钟的带宽至少是数据带宽的2倍,限制了数据的传输速度

- 长距离传输数据和时钟信号会失去同步

异步串行接口

- 特点:

- 接收端提取时序信息

- 速率是确定的 - 每个节点需要准确且稳定的时钟源

- 每个Byte或Word都以Start和Stop位成帧

-

- Universal Asynchronous Receiver/transmitter - 异步收发

- TXD/RXD,全双工

- 可达3Mbps

- 设计中要注意的问题:

- 在接收端需要根据发送端的波特率进行正确设置

- TXD/RXD不要接反

-

- 最常用的总线

- PnP应用

- 分为Host、Slave、OTG(On The Go)模式,要正确选取

- 1.5Mbps(低速)、12Mbps(全速)、480Mbps(高速)、10Gbps(Type C)

- D+/D-/Vcc/GND四线连接,D+/D-为差分信号,要等延时走线

- Ethernet

- IEEE802.3标准,支持速率10Mbps、100Mbps、1Gbps、100Gbps

- 差分收、发信号TX+/TX-、RX+/RX-

- 以太网串行接数据包按帧进行封装传输,每一帧有收、发两端的MAC地址

- 以太网的数据采用曼切斯特编码以便时钟信号的提取

- CAN总线

- Controller Area Network

- 异步、半双工、固定比特率

- 最高1Mbps

- 所有节点都是平等的,配置为P2P

- 有仲裁机制确定各个节点的通信优先级

- 节点数没有限制

- 总线节点没有地址,但有“信息过滤”的机制

- 数据成帧进行传输

- 高度的数据安全级别、错误检查

模拟接口

内置了ADC、DAC

内置了温度传感器

Cypress的PSoC器件