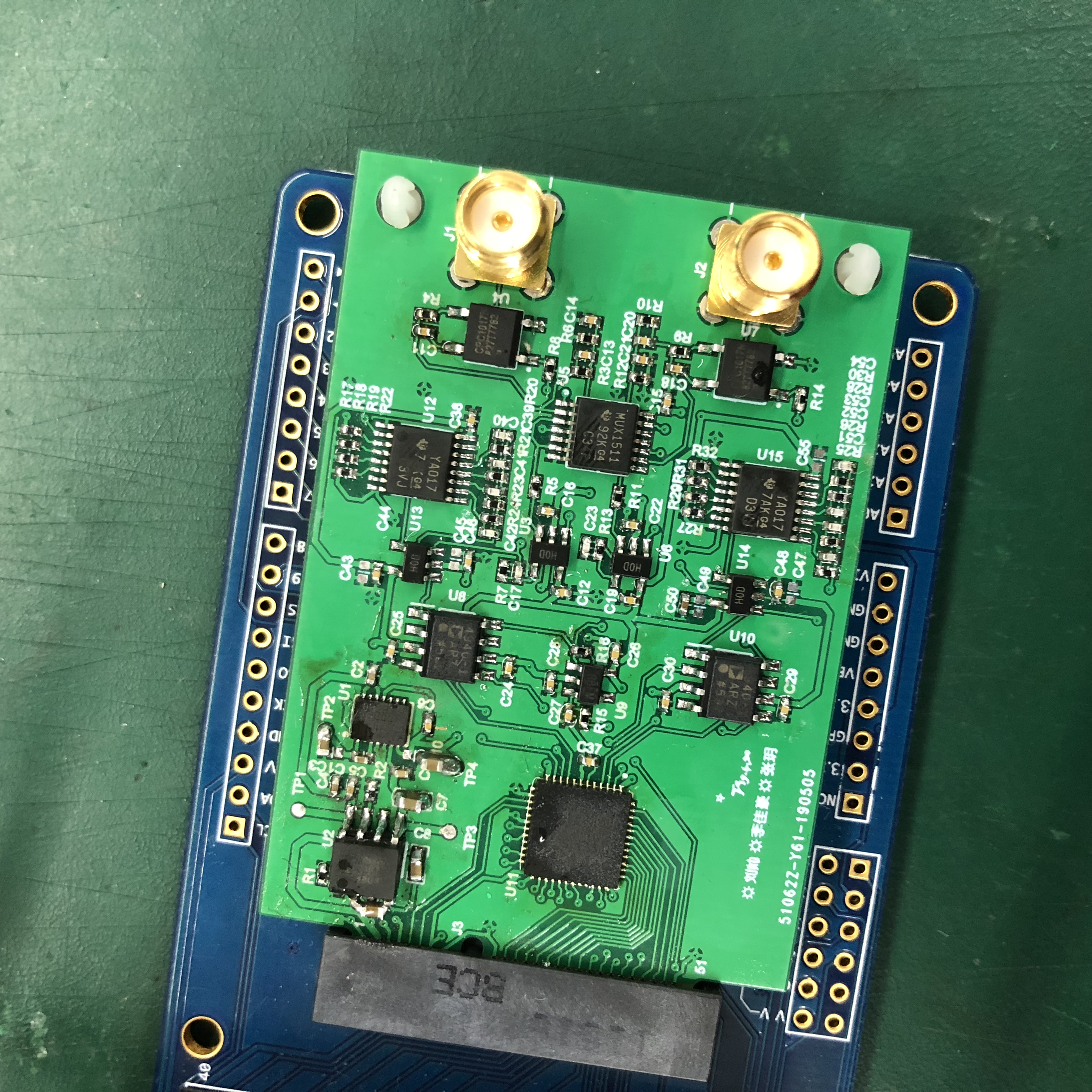

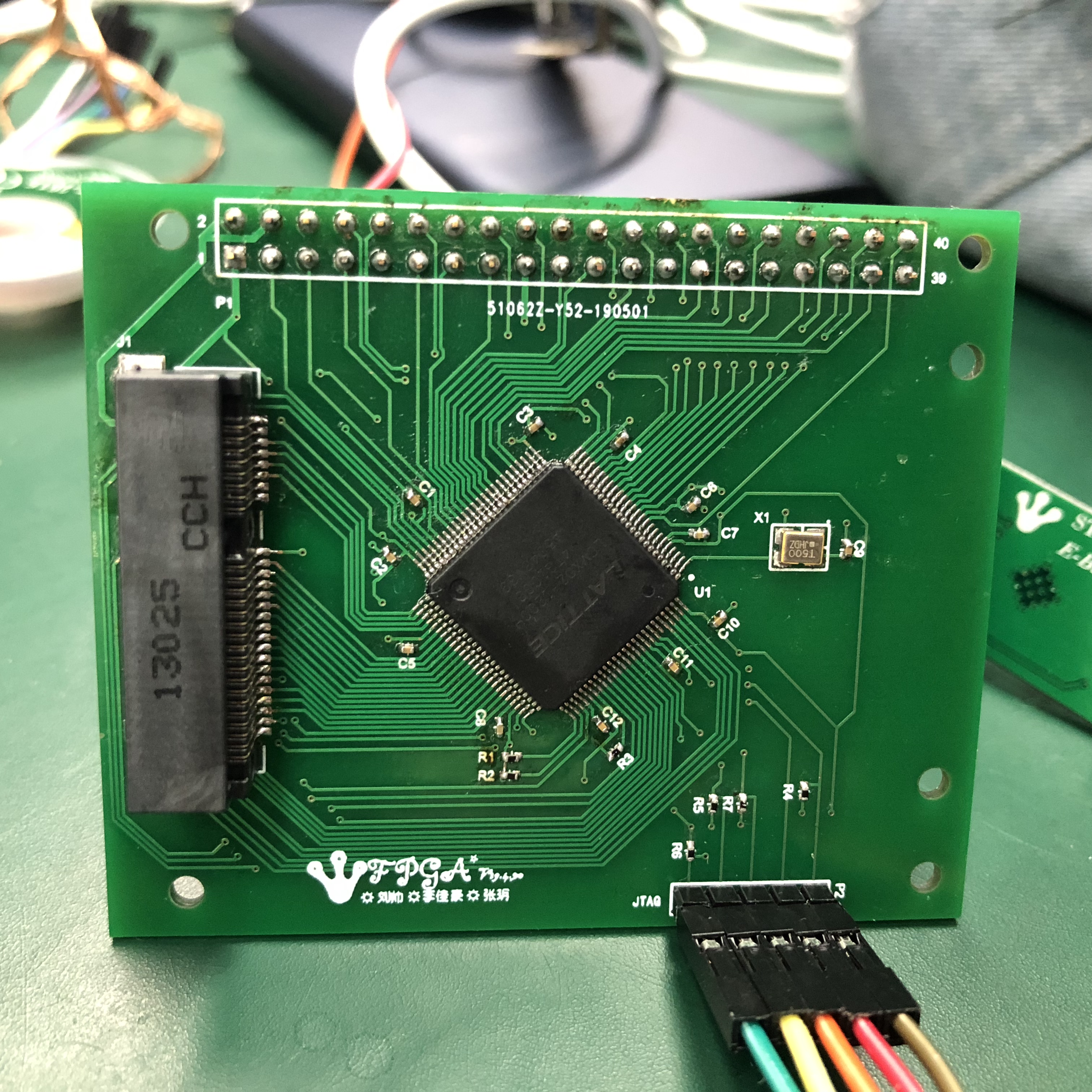

PCB焊接、调试

FPGA连接和Verilog编程

module Range_selection (

/*input range1_5mv_200mv,

input range2_200mv_800mv,

input range3_800mv_3v,

input range4_3v_8v,

input range5_8v_10v,*/

output reg TMU_SEL1,

output reg TMU_SEL2,

output reg TSA_IN1,

output reg TSA_IN2,

output CH1_DC

);

assign CH1_DC = 1;

assign range1_5mv_200mv = 0;

assign range2_200mv_800mv = 0;

assign range3_800mv_3v = 0;

assign range4_3v_8v = 0;

assign range5_8v_10v = 1;

always @ (*) begin

if (range1_5mv_200mv) begin //不衰减且放大20倍

TMU_SEL1 = 1'b1;

TMU_SEL2 = 1'b0;

TSA_IN1 = 1'b0;

TSA_IN2 = 1'b0;

end

else if (range2_200mv_800mv) begin //衰减40倍且放大20倍

TMU_SEL1 <= 1'b0;

TMU_SEL2 <= 1'b1;

TSA_IN1 <= 1'b0;

TSA_IN2 <= 1'b0;

end

else if (range3_800mv_3v) begin //衰减40倍且放大5倍

TMU_SEL1 <= 1'b0;

TMU_SEL2 <= 1'b1;

TSA_IN1 <= 1'b1;

TSA_IN2 <= 1'b0;

end

else if (range4_3v_8v) begin //衰减40倍且放大2倍

TMU_SEL1 <= 1'b0;

TMU_SEL2 <= 1'b1;

TSA_IN1 <= 1'b0;

TSA_IN2 <= 1'b1;

end

else if(range5_8v_10v) begin //衰减40倍且放大1.5倍

TMU_SEL1 <= 1'b1;

TMU_SEL2 <= 1'b0;

TSA_IN1 <= 1'b1;

TSA_IN2 <= 1'b1;

end

end

endmodule

module ceshiadc

(

input clk_in,

//input rst_in,

output reg clkp,

output reg clkm,

input [7:0] data_a,

input dclka_in,

//input dora,

input [7:0] data_b,

input dclkb_in,

//input dorb,

output reg [7:0] display_a,

output reg [7:0] display_b

);

always @(*)

begin

clkp = clk_in;

clkm = ~clk_in;

end

always@(posedge dclka_in )

begin

//if(!rst_in)

//begin

//display_a <= 8'b0;

//display_b <= 8'b0;

//end

//else

display_a <= data_a;

end

always@(posedge dclkb_in )

begin

//if(!rst_in)

//display_b <= 8'b0;

//else

display_b <= data_b;

end

endmodule