NMPSM3软处理器

NMPSM3概述

在UCSC扩展学院上了第一门FPGA课后,我对这些设备为普通人提供的功能感到惊讶,我决定更深入地研究它们。我最终意识到我有足够的逻辑设计知识,可以构建自己的简单处理器。在了解了KCPSM(nanoblaze)之后,我开始构建自己的处理器,并将其称为NMPSM(Nick Mikstas可编程状态机)。我花了三遍迭代才能制作出功能全面的处理器,因此命名为NMPSM3。即使NMPSM3受到nanoblaze IO方案的启发,其内部结构也完全不同。NMPSM3是具有四个独立中断和一个复位的16位处理器。NMPSM至少需要实现四个18Kb BRAMS:一个用于寄存器,一个用于堆栈,一个用于解码器,至少一个用于程序ROM。使处理器正常工作后,我为其编写了汇编程序,并创建了一个大型项目以展示其功能。

当我第一次设计NMPSM3时,它是在Digilent Nexys 2板上实现的。Nexys 2上有Xilinx Spartan 3部件。在成功实施该项目之后,几年来我对NMPSM3一无所获。我最终在SCU上了一门课,基本上和UCSC Extension上的一门课一样。我决定通过更新项目以使其在Digilent Basys 3 FPGA板上工作来使NMPSM3振作起来。由于新的FPGA部件(Artyx 7)比Spartan 3具有更多的功能,因此我也对该项目进行了一些升级。我也写了一份详尽的报告。

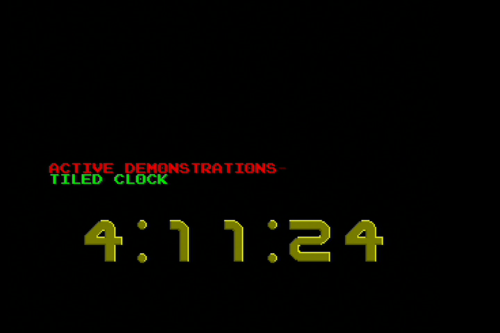

NMPSM3屏幕截图

NMPSM3硬件

与处理器一起,我还基于8位Nintendo构建了其他一些模块,包括UART和图片处理单元(PPU)。一些Verilog代码很粗糙,因为在创建此项目时我正在学习Verilog。

Final_Project.v

`timescale 1ns / 1ps module Final_Project( input clk, input [15:0]sw, input btnC, input btnU, input btnD, input btnL, input btnR, input data, input RsRx, output RsTx, output RxTest, output TxTest, output [15:0]led, output [6:0]seg, output [3:0]an, output dp, output [3:0]vgaRed, output [3:0]vgaGreen, output [3:0]vgaBlue, output Hsync, output Vsync, output sclk, output ce ); //UART test ports. assign RxTest = RsRx; assign TxTest = RsTx; wire clk100MHz; wire clk50MHz; wire clk25MHz; wire t0out; wire t1out; wire ack0; wire ack1; wire ack2; wire ack3; wire sigout0; wire sigout1; wire sigout2; wire sigout3; wire ce1k; wire blink; wire read; wire write; wire vblank; wire reset; wire [15:0]id; wire [15:0]outdata; wire [7:0]hour; wire [7:0]min; wire [7:0]sec; wire [35:0]inst; wire [15:0]in_port; wire [15:0]address; wire [7:0]romdata; wire [11:0]mdout; wire [7:0]vgadata; wire [9:0]addr; wire [10:0]romaddress; wire [11:0]mdin; //UART wires. wire [7:0]uartdata; wire [11:0]txcount; wire [11:0]rxcount; //Unused VGA bits in this design. assign vgaRed[0] = 1'b0; assign vgaGreen[0] = 1'b0; assign vgaBlue[0] = 1'b0; assign vgaBlue[1] = 1'b0; //Reset signal. assign reset = btnU; //Flip-flop for interrupt 0. FF ff0(.set(t0out), .reset(ack0), .sigout(sigout0)); //Flip-flop for interrupt 1. FF ff1(.set(t1out), .reset(ack1), .sigout(sigout1)); //Flip-flop for interrupt 2. FF ff2(.set(vblank), .reset(ack2), .sigout(sigout2)); //Flip-flop for interrupt 3(not used). FF ff3(.set(1'b0), .reset(ack3), .sigout(sigout3)); //Divide by 100,000. div100k divideBy100K(.clock(clk100MHz), .ce1k(ce1k)); //Clock divider. clk25 c(.clk_in1(clk), .clk_out1(clk100MHz), .clk_out2(clk50MHz), .clk_out3(clk25MHz)); //NMPSM3 soft processor. NMPSM3 nmpsm3(.clk(clk100MHz), .reset(reset), .IRQ0(sigout0), .IRQ1(sigout1), .IRQ2(sigout2), .IRQ3(sigout3), .INSTRUCTION(inst), .IN_PORT(in_port), .READ_STROBE(read), .WRITE_STROBE(write), .IRQ_ACK0(ack0), .IRQ_ACK1(ack1), .IRQ_ACK2(ack2), .IRQ_ACK3(ack3), .ADDRESS(address), .OUT_PORT(outdata), .PORT_ID(id)); //Program ROM for NMPSM3. Program_ROM prgROM(.clka(clk100MHz), .addra(address[9:0]), .douta(inst)); //Lookup ROM Lookup_ROM lookuprom(.clka(clk100MHz), .addra(romaddress), .douta(romdata)); //UART uart uart1(.clk(clk100MHz), .reset(reset), .id(id), .din(outdata), .write(write), .rx(RsRx), .tx(RsTx), .dout(uartdata), .rxcount(rxcount), .txcount(txcount)); //LED output controller. ledio LEDIO(.clk(clk100MHz), .reset(reset), .write(write), .id(id), .din(outdata), .ledsout(led[7:0])); //LED output controller 2. LEDIO2 ledio2(.clk(clk100MHz), .reset(reset), .write(write), .id(id), .din(outdata), .ledsout(led[15:8])); //Seven segment controller. seg7io seg7control(.clk(clk100MHz), .ce1k(ce1k), .write(write), .reset(reset), .id(id), .din(outdata), .segselect(an), .segs({dp,seg})); //Timer 0. timer0 time0(.clk(clk100MHz), .cein(ce1k), .write(write), .reset(reset), .id(id), .din(outdata), .dout(t0out)); //Timer 1. timer1 time1(.clk(clk100MHz), .cein(ce1k), .write(write), .reset(reset), .id(id), .din(outdata), .dout(t1out)); //ROM controller for lookup ROM. ROMcontroller ROMcontrol(.clk(clk100MHz), .id(id), .ain(outdata), .aout(romaddress)); //Processor input data MUX. dataMUX datamux(.read(read), .blink(blink), .id(id), .i2cdata(16'd0), .i2cstatus(16'd0), .xpos(16'd0), .ypos(16'd0), .uartdata({8'h00,uartdata}), .txcount(txcount), .rxcount(rxcount), .romdata(romdata), .switches(sw), .sec(sec), .min(min), .hour(hour), .micdata({btnD, 3'h0, mdout}), .dout(in_port)); //Clock control. ClockControl clockcontrol(.clock(clk100MHz), .ce_1KHz(ce1k), .button({btnD, btnL, btnC, btnR}), .blink(blink), .hour(hour), .min(min), .sec(sec)); //Picture processing unit. VGA ppu(.clk25MHz(clk25MHz), .clk(clk100MHz), .write(write), .id(id), .data(outdata[7:0]), .vblank(vblank), .vsync(Vsync), .hsync(Hsync), .vga({vgaBlue[3:2], vgaGreen[3:1], vgaRed[3:1]})); //Microphone control. MControl mc(.clk(clk100MHz), .reset(reset), .serialdata(data), .nenable(ce), .sclk(sclk), .micdata(mdout)); endmodule

NMPSM3.v

`timescale 1ns / 1ps module NMPSM3(clk, reset, INSTRUCTION, IN_PORT, IRQ0, IRQ1, IRQ2, IRQ3, ADDRESS, OUT_PORT, PORT_ID, READ_STROBE, WRITE_STROBE, IRQ_ACK0, IRQ_ACK1, IRQ_ACK2, IRQ_ACK3); input clk, reset, IRQ0, IRQ1, IRQ2, IRQ3; input [35:0]INSTRUCTION; input [15:0]IN_PORT; output READ_STROBE, WRITE_STROBE, IRQ_ACK0, IRQ_ACK1, IRQ_ACK2, IRQ_ACK3; output [15:0]PORT_ID; output [15:0]OUT_PORT; output [15:0]ADDRESS; localparam SIZE = 16; localparam JPNZ = 8'h16; localparam JPZ = 8'h19; localparam JPNC = 8'h1C; localparam JPC = 8'h20; localparam CLNZ = 8'h29; localparam CLZ = 8'h2C; localparam CLNC = 8'h30; localparam CLC = 8'h33; localparam RTNZ = 8'h39; localparam RTZ = 8'h3C; localparam RTNC = 8'h40; localparam RTC = 8'h43; localparam IRQADDR0 = 8'hCC; localparam IRQADDR1 = 8'hD0; localparam IRQADDR2 = 8'hD3; localparam IRQADDR3 = 8'hD6; localparam STEP = 8'hD9; wire [43:0]control; wire [15:0]portA; wire [15:0]portB; wire zero; wire [7:0]decodeAddr; wire I0, I1, I2, I3; wire [15:0]addrp1; wire [10:0] addrA; wire [15:0] dataA; wire weA; wire [10:0] addrB; wire [15:0] dataB; wire weB; wire [9:0]stackm1; wire [19:0]none; wire [7:0]portAup; wire [7:0]portAdn; wire [7:0]portBup; wire [7:0]portBdn; wire [4:0]sel; wire [15:0]a; wire [15:0]b; wire [15:0]inst; reg [1:0]IRQload = 2'b00; reg [15:0]wresult = 16'h0000; reg wcarry = 1'b0; reg [15:0]result = 16'h0000; reg carry = 1'b0; reg [1:0]load = 2'b00; reg IRQMreg = 1'b1; reg IRQ0reg = 1'b0; reg IRQ1reg = 1'b0; reg IRQ2reg = 1'b0; reg IRQ3reg = 1'b0; reg [9:0]stack = 10'h000; reg [15:0]addr = 16'h0000; //Used to synchronize interrupts and reset with internal clock. reg IR0 = 1'b0; reg IR1 = 1'b0; reg IR2 = 1'b0; reg IR3 = 1'b0; reg [1:0]rst = 2'b00; RAMB16_S36_S36 #( .INIT_A(36'h000000000), // Value of output RAM registers on Port A at startup .INIT_B(36'h000000000), // Value of output RAM registers on Port B at startup .SRVAL_A(36'h000000000), // Port A output value upon SSR assertion .SRVAL_B(36'h000000000), // Port B output value upon SSR assertion .WRITE_MODE_A("WRITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE .WRITE_MODE_B("WRITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE .SIM_COLLISION_CHECK("ALL"), // "NONE", "WARNING_ONLY", "GENERATE_X_ONLY", "ALL" // Micro-code for the decoder ROM .INIT_00(256'H00200001_00000000_00000000_04040007_00000000_00000000_04000007_00000000), .INIT_01(256'H00000000_08200007_00000001_00000000_00000000_08000007_00000000_04040007), .INIT_02(256'H00000000_0000000B_00000000_00000000_0000000F_00000000_00000000_0000000B), .INIT_03(256'H00000000_00000000_00000000_0000000B_00000000_00000000_0000000B_00000000), .INIT_04(256'H00000000_1950000F_00000000_00000000_1950000B_00000000_00000000_0000000B), .INIT_05(256'H00000000_00000000_00000000_1950000B_00000000_00000000_1950000B_00000000), .INIT_06(256'H00000017_12300001_00000000_00000000_1950000B_00000000_00000000_1950000B), .INIT_07(256'H00000000_00000000_00000017_12300001_00000000_00000017_12300001_00000000), .INIT_08(256'H00001137_12300001_00000000_00000017_12300001_00000000_00000017_12300001), .INIT_09(256'H00000000_00000000_00000000_44080407_00000000_00001157_12300001_00000000), .INIT_0A(256'H00000000_20000A07_00000000_00000000_20000C07_00000000_00000000_44080207), .INIT_0B(256'H00000000_00000000_00000000_04065007_00000000_00000000_04064007_00000000), .INIT_0C(256'H00000000_04066007_00000000_00000000_04063007_00000000_00000000_04062007), .INIT_0D(256'H00000000_00000000_00000000_0406C007_00000000_00000000_04067007_00000000), .INIT_0E(256'H00000000_04069007_00000000_00000000_0406D007_00000000_00000000_04068007), .INIT_0F(256'H00000000_00000000_00000000_0406A007_00000000_00000000_0406E007_00000000), .INIT_10(256'H00000000_00010007_00000000_00000000_0406B007_00000000_00000000_0406F007), .INIT_11(256'H00000000_00000000_00000000_00012007_00000000_00000000_00011007_00000000), .INIT_12(256'H00000000_04075007_00000000_00000000_04074007_00000000_00000000_00013007), .INIT_13(256'H00000000_00000000_00000000_04077007_00000000_00000000_04076007_00000000), .INIT_14(256'H00000000_00000027_00000000_00000000_00018007_00000000_00000000_00019007), .INIT_15(256'H00000000_00000000_00000000_00000067_00000000_00000000_00000047_00000000), .INIT_16(256'H00000000_000000C7_00000000_00000000_000000A7_00000000_00000000_00000087), .INIT_17(256'H00000000_00000000_00000000_00000107_00000000_00000000_000000E7_00000000), .INIT_18(256'H04040007_12300001_00000000_00000000_00000000_00000000_00000000_19100007), .INIT_19(256'H00000000_00000000_80000013_99900161_00000000_00000000_00000000_00000000), .INIT_1A(256'H00000013_19900161_00000000_00000013_19900161_00000000_00000013_19900161), .INIT_1B(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000007_00000000), .INIT_1C(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_1D(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_1E(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_1F(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_20(256'H00000080_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_21(256'H00000000_00000000_000000E0_00000000_00000000_00000000_00000000_00000000), .INIT_22(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_23(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_24(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_25(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_26(256'H00000000_00000370_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_27(256'H00000000_00000000_00000000_000003D0_00000000_00000000_000003A0_00000000), .INIT_28(256'H00000000_00000470_00000000_00000000_00000440_00000000_00000000_00000410), .INIT_29(256'H00000000_00000000_00000000_00000000_00000000_00000000_000004A0_00000000), .INIT_2A(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_2B(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_2C(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_2D(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_2E(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_2F(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_30(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_31(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_32(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_33(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_34(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_35(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_36(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_37(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_38(256'H00000000_00000C70_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_39(256'H00000000_00000000_00000000_00000CD8_00000000_00000000_00000000_00000000), .INIT_3A(256'H00000004_00000D6C_00000000_00000002_00000D4A_00000000_00000001_00000D19), .INIT_3B(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_3C(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_3D(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_3E(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000), .INIT_3F(256'H00000000_00000000_00000000_00000000_00000000_00000000_00000000_00000000)) DecoderROM ( .DOA(control[31:0]), // Port A 32-bit Data Output .DOB({none, control[43:32]}), // Port B 32-bit Data Output .ADDRA({1'b0, decodeAddr}), // Port A 9-bit Address Input .ADDRB({1'b1, decodeAddr}), // Port B 9-bit Address Input .CLKA(clk), // Port A Clock .CLKB(clk), // Port B Clock .ENA(1'b1), // Port A RAM Enable Input .ENB(1'b1), // Port B RAM Enable Input .SSRA(1'b0), // Port A Synchronous Set/Reset Input .SSRB(1'b0), // Port B Synchronous Set/Reset Input .WEA(1'b0), // Port A Write Enable Input .WEB(1'b0) // Port B Write Enable Input ); RAMB16_S9_S9 #( .INIT_A(18'h00000), // Value of output RAM registers on Port A at startup .INIT_B(18'h00000), // Value of output RAM registers on Port B at startup .SRVAL_A(18'h00000), // Port A output value upon SSR assertion .SRVAL_B(18'h00000), // Port B output value upon SSR assertion .WRITE_MODE_A("WRITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE .WRITE_MODE_B("WRITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE .SIM_COLLISION_CHECK("ALL")) // "NONE", "WARNING_ONLY", "GENERATE_X_ONLY", "ALL" RAMupper ( .DOA(portAup), // Port A 16-bit Data Output .DOB(portBup), // Port B 16-bit Data Output .ADDRA(addrA), // Port A 10-bit Address Input .ADDRB(addrB), // Port B 10-bit Address Input .CLKA(clk), // Port A Clock .CLKB(clk), // Port B Clock .DIA(dataA[15:8]), // Port A 16-bit Data Input .DIB(dataB[15:8]), // Port-B 16-bit Data Input .DIPA(1'b0), // Port A 1-bit parity Input .DIPB(1'b0), // Port B 1-bit parity Input .ENA(1'b1), // Port A RAM Enable Input .ENB(1'b1), // Port B RAM Enable Input .SSRA(1'b0), // Port A Synchronous Set/Reset Input .SSRB(1'b0), // Port B Synchronous Set/Reset Input .WEA(weA), // Port A Write Enable Input .WEB(weB) // Port B Write Enable Input ); RAMB16_S9_S9 #( .INIT_A(18'h00000), // Value of output RAM registers on Port A at startup .INIT_B(18'h00000), // Value of output RAM registers on Port B at startup .SRVAL_A(18'h00000), // Port A output value upon SSR assertion .SRVAL_B(18'h00000), // Port B output value upon SSR assertion .WRITE_MODE_A("WRITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE .WRITE_MODE_B("WRITE_FIRST"), // WRITE_FIRST, READ_FIRST or NO_CHANGE .SIM_COLLISION_CHECK("ALL")) // "NONE", "WARNING_ONLY", "GENERATE_X_ONLY", "ALL" RAMlower ( .DOA(portAdn), // Port A 16-bit Data Output .DOB(portBdn), // Port B 16-bit Data Output .ADDRA(addrA), // Port A 10-bit Address Input .ADDRB(addrB), // Port B 10-bit Address Input .CLKA(clk), // Port A Clock .CLKB(clk), // Port B Clock .DIA(dataA[7:0]), // Port A 16-bit Data Input .DIB(dataB[7:0]), // Port-B 16-bit Data Input .DIPA(1'b0), // Port A 1-bit parity Input .DIPB(1'b0), // Port B 1-bit parity Input .ENA(1'b1), // Port A RAM Enable Input .ENB(1'b1), // Port B RAM Enable Input .SSRA(1'b0), // Port A Synchronous Set/Reset Input .SSRB(1'b0), // Port B Synchronous Set/Reset Input .WEA(weA), // Port A Write Enable Input .WEB(weB) // Port B Write Enable Input ); always @(posedge clk) begin if(rst) begin carry <= 1'b0; IRQMreg <= 1'b1; IRQ0reg <= 1'b0; IRQ1reg <= 1'b0; IRQ2reg <= 1'b0; IRQ3reg <= 1'b0; stack <= 10'h000; result <= 16'h0000; addr <= 16'h0000; load <= 2'b00; rst <= rst + 1'b1; end else begin result <= wresult; carry <= wcarry; if(control[1]) addr <= ADDRESS; if(control[25:24] == 2'b01) stack <= stack + 1'b1; if(control[25:24] == 2'b10) stack <= stack - 1'b1; if(control[8:5] == 4'b0001) IRQ0reg <=1'b1; if(control[8:5] == 4'b0010) IRQ1reg <=1'b1; if(control[8:5] == 4'b0011) IRQ2reg <=1'b1; if(control[8:5] == 4'b0100) IRQ3reg <=1'b1; if(control[8:5] == 4'b0101) IRQ0reg <=1'b0; if(control[8:5] == 4'b0110) IRQ1reg <=1'b0; if(control[8:5] == 4'b0111) IRQ2reg <=1'b0; if(control[8:5] == 4'b1000) IRQ3reg <=1'b0; if(control[8:5] == 4'b1001) IRQMreg <=1'b1; if(control[8:5] == 4'b1010) begin IRQMreg <= 1'b1; IRQ0reg <= 1'b0; IRQ1reg <= 1'b0; IRQ2reg <= 1'b0; IRQ3reg <= 1'b0; end if(control[8:5] == 4'b1011) IRQMreg <= 1'b0; if(control[35]) load <= {carry, ~zero}; //Synchronize interrupts and reset with the internal clock. if(IRQ0) IR0 <= 1'b1; else IR0 <= 1'b0; if(IRQ1) IR1 <= 1'b1; else IR1 <= 1'b0; if(IRQ2) IR2 <= 1'b1; else IR2 <= 1'b0; if(IRQ3) IR3 <= 1'b1; else IR3 <= 1'b0; if (reset) rst <= 2'b01; end end assign IRQ_ACK0 = control[31]; assign IRQ_ACK1 = control[32]; assign IRQ_ACK2 = control[33]; assign IRQ_ACK3 = control[34]; always @(control) case(control[33:31]) 3'b001 : IRQload <= 2'h1; 3'b010 : IRQload <= 2'h2; 3'b100 : IRQload <= 2'h3; default : IRQload <= 2'h4; endcase and andIRQ0 (I0, IRQMreg, IRQ0reg, IR0); and andIRQ1 (I1, IRQMreg, IRQ1reg, IR1); and andIRQ2 (I2, IRQMreg, IRQ2reg, IR2); and andIRQ3 (I3, IRQMreg, IRQ3reg, IR3); assign decodeAddr = control[0] ? control[43:36] : ({control[0], I0} == 2'b01) ? IRQADDR0 : ({control[0], I0, I1} == 3'b001) ? IRQADDR1 : ({control[0], I0, I1, I2} == 4'b0001) ? IRQADDR2 : ({control[0], I0, I1, I2, I3} == 5'b00001) ? IRQADDR3 : ({zero, INSTRUCTION[35:28]} == {1'b1, JPNZ}) ? STEP : ({zero, INSTRUCTION[35:28]} == {1'b0, JPZ }) ? STEP : ({carry, INSTRUCTION[35:28]} == {1'b1, JPNC}) ? STEP : ({carry, INSTRUCTION[35:28]} == {1'b0, JPC }) ? STEP : ({zero, INSTRUCTION[35:28]} == {1'b1, CLNZ}) ? STEP : ({zero, INSTRUCTION[35:28]} == {1'b0, CLZ }) ? STEP : ({carry, INSTRUCTION[35:28]} == {1'b1, CLNC}) ? STEP : ({carry, INSTRUCTION[35:28]} == {1'b0, CLC }) ? STEP : ({zero, INSTRUCTION[35:28]} == {1'b1, RTNZ}) ? STEP : ({zero, INSTRUCTION[35:28]} == {1'b0, RTZ }) ? STEP : ({carry, INSTRUCTION[35:28]} == {1'b1, RTNC}) ? STEP : ({carry, INSTRUCTION[35:28]} == {1'b0, RTC }) ? STEP : INSTRUCTION[35:28]; assign PORT_ID = (control[10:9] == 2'b01) ? portB : (control[10:9] == 2'b10) ? INSTRUCTION[15:0] : 16'h0000; assign OUT_PORT = (control[11] == 1'b1) ? portA : 16'h0000; assign WRITE_STROBE = control[29]; assign READ_STROBE = control[30]; assign stackm1 = stack - 1'b1; assign weA = control[26]; assign weB = control[27]; assign addrA = {1'b0, INSTRUCTION[25:16]}; assign portA = {portAup, portAdn}; assign portB = {portBup, portBdn}; assign dataA = (control[19:17] == 3'b001) ? portA : (control[19:17] == 3'b010) ? portB : (control[19:17] == 3'b011) ? wresult : (control[19:17] == 3'b100) ? IN_PORT : INSTRUCTION[15:0]; assign addrB = (control[21:20] == 2'b01) ? {control[28], stack[9:0]} : (control[21:20] == 2'b10) ? {control[28], portB[9:0]} : (control[21:20] == 2'b11) ? {control[28], stackm1[9:0]} : {control[28], INSTRUCTION[9:0]}; assign dataB = (control[23:22] == 2'b01) ? addrp1 : (control[23:22] == 2'b10) ? ADDRESS : portA; assign addrp1 = addr + 1'b1; assign ADDRESS = rst ? 16'h0000 : (control[4:2] == 3'b001) ? addrp1 : (control[4:2] == 3'b010) ? INSTRUCTION[15:0] : (control[4:2] == 3'b011) ? portA : (control[4:2] == 3'b100) ? {14'h0000,IRQload}: (control[4:2] == 3'b101) ? portB : addr; //ALU code begins here. assign zero = (result == 16'h0000) ? 1'b1 : 1'b0; assign inst = INSTRUCTION[15:0]; assign a = portA; assign b = portB; assign sel = control[16:12]; //OR a | b, a | inst wire orc; wire [15:0]orr; assign orc = 1'b0; assign orr = sel[0] ? (a | b) : (a | inst); //AND a & b, a & inst wire andc; wire [15:0]andr; assign andc = 1'b0; assign andr = sel[0] ? (a & b) : (a & inst); //XOR a ^ b, a ^ inst wire xorc; wire [15:0]xorr; assign xorc = 1'b0; assign xorr = sel[0] ? (a ^ b) : (a ^ inst); //ADD ADD a + b, ADDC a + b wire addbcarryin, addbcarryout; wire [15:0]addbresult; assign addbcarryin = sel[0] ? carry : 1'b0; assign {addbcarryout, addbresult} = a + b + addbcarryin; //SUB SUB a - b, SUBC a - b wire subbcarryin, subbcarryout; wire [15:0]subbresult; assign subbcarryin = sel[0] ? carry : 1'b0; assign {subbcarryout, subbresult} = a - b - subbcarryin; //ADD ADD a + inst, ADDC a + inst wire addicarryin, addicarryout; wire [15:0]addiresult; assign addicarryin = sel[0] ? carry : 1'b0; assign {addicarryout, addiresult} = a + inst + addicarryin; //SUB SUB a - inst, SUBC a - inst wire subicarryin, subicarryout; wire [15:0]subiresult; assign subicarryin = sel[0] ? carry : 1'b0; assign {subicarryout, subiresult} = a - inst - subicarryin; //TEST TEST a and b, TEST a and inst wire testc; wire [15:0]testr; assign testc = ^testr; assign testr = sel[0] ? (a & b) : (a & inst); //COMP COMP a to b, COMP a to inst wire tempc1, tempc2, compc; wire [15:0]compr; assign tempc1 = (a < inst) ? 1'b1 : 1'b0; assign tempc2 = (a < b) ? 1'b1 : 1'b0; assign compc = sel[0] ? tempc2 : tempc1; assign compr = sel[0] ? (a ^ b) : (a ^ inst); //LEFT ROL, ASL wire leftc; wire [15:0]leftr; assign leftc = a[15]; assign leftr = sel[0] ? {a[14:0], carry} : {a[14:0], 1'b0}; //RIGHT ROR, LSR wire rightc; wire [15:0]rightr; assign rightc = a[0]; assign rightr = sel[0] ? {carry, a[15:1]} : {1'b0, a[15:1]}; //CARRY SETC, CLRC wire carryc; wire [15:0]carryr; assign carryc = sel[0]; assign carryr = result; //LOAD LOAD carry and result with load, no change. wire loadc; wire [15:0]loadr; assign loadc = sel[0] ? load[1] : carry; assign loadr = sel[0] ? {15'h0000, load[0]} : result; //MUX results always @(*) case(sel[4:1]) 4'b0000 : wresult <= loadr; 4'b0001 : wresult <= orr; 4'b0010 : wresult <= andr; 4'b0011 : wresult <= xorr; 4'b0100 : wresult <= addbresult; 4'b0101 : wresult <= subbresult; 4'b0110 : wresult <= addiresult; 4'b0111 : wresult <= subiresult; 4'b1000 : wresult <= testr; 4'b1001 : wresult <= compr; 4'b1010 : wresult <= leftr; 4'b1011 : wresult <= rightr; 4'b1100 : wresult <= carryr; default : wresult <= loadr; endcase always @(*) case(sel[4:1]) 4'b0000 : wcarry <= loadc; 4'b0001 : wcarry <= orc; 4'b0010 : wcarry <= andc; 4'b0011 : wcarry <= xorc; 4'b0100 : wcarry <= addbcarryout; 4'b0101 : wcarry <= subbcarryout; 4'b0110 : wcarry <= addicarryout; 4'b0111 : wcarry <= subicarryout; 4'b1000 : wcarry <= testc; 4'b1001 : wcarry <= compc; 4'b1010 : wcarry <= leftc; 4'b1011 : wcarry <= rightc; 4'b1100 : wcarry <= carryc; default : wcarry <= loadc; endcase endmodule

VGA.v