一种基于片内数据处理的、可以低速数据传输的用于示波器显示控制的实现方式

背景技术

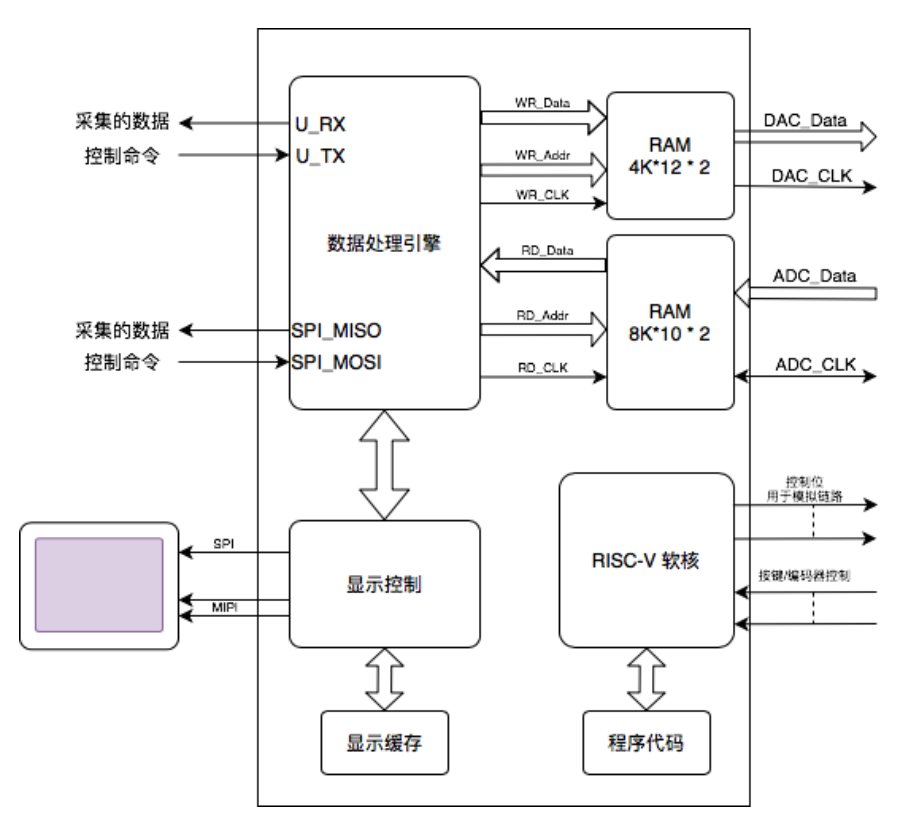

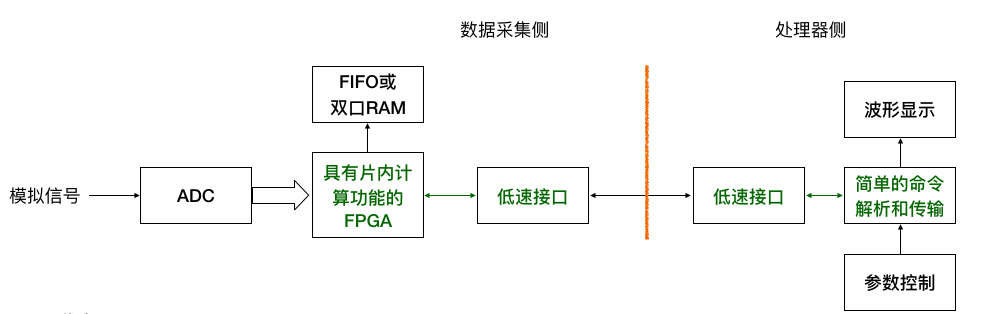

此发明使用FPGA(现场可编程逻辑门阵列)器件,通过移植RISC-V软核+片内数据计算+自适应缩放来对采集到的数据根据上位机(PC、工控机或移动终端)的指令对数据进行处理,只将需要在显示屏上显示的数据传输到上位机上,免去了上位机的数据处理,大大降低了同上位机之间的数据传输量,扩展了数据传输的方式,可以用低速的传输方式(串口、蓝牙等)应用在高速的数据采集、示波器中,另外在片内移植了RISC-V软核,实现对上位机指令的高效解析和执行。

1 现有技术情况

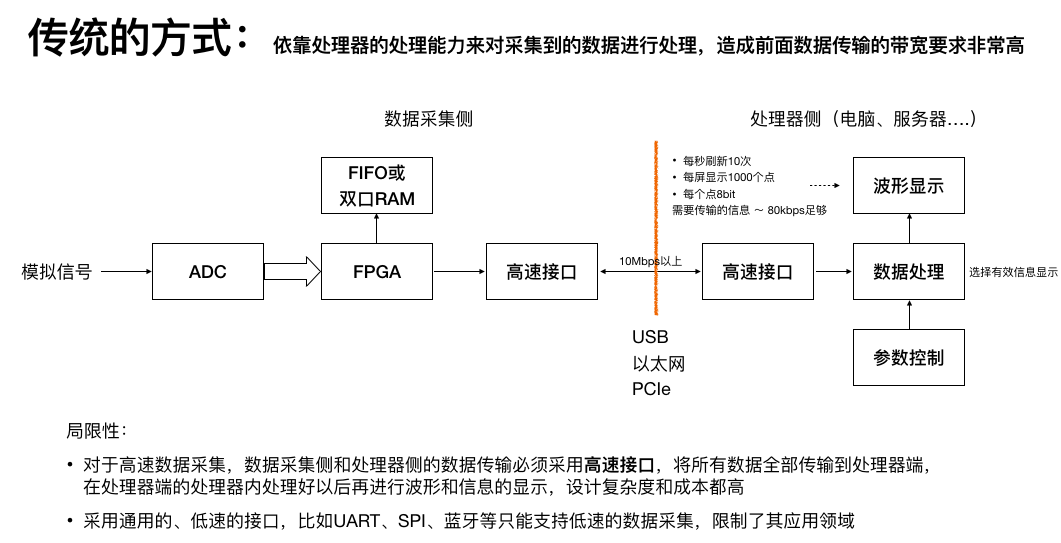

目前基于PC或移动终端显示的数据采集系统、虚拟示波器都是通过高速总线将ADC量化后的数据传输到电脑、服务器或手机、平板上,通过电脑、服务器或手机、平板的处理器对收到的数据进行处理以后,显示在电脑、服务器或手机、平板的屏幕上,数据采集端和上位机之间的数据传输一般都是通过高速的总线比如USB2.0,以太网等。

2 现有技术缺陷

有两个缺陷:

- 需要高速的数据总线来进行数据的传输,无法使用普遍使用的串口(UART)、蓝牙/BLE等低速总线,成本高,系统设计复杂;

- 上位机需要对接收到的数据进行处理以后再进行显示,消耗了上位机的处理器资源,程序编写复杂。

发明内容

1 发明内容/改进点

波形和数据显示的处理放置在FPGA中,通过FPGA中植入RISC-V软核来便捷地解析上位机发送来的指令,进而控制数据处理单元对采集到的数据进行数字信号处理,同时根据上位机传来的显示控制命令,对处理后的数据做自动显示处理,仅将在屏幕上显示的数据发送到上位机

2 该发明的创新之处

- FPGA内采用RISC-V软核对上位机的控制命令进行解析

- “采集数据”和“远程显示映射存储”双存储结构

- 采用“远程显示映射”协议和算法,自适应上位机屏幕显示的数据空间

3 该发明的有益效果

- 大大降低了数据采集单元和上位机之间的数据传数量,数据的传输可靠性得到提升

- 可以采用更通用的低速传输总线比如UART、蓝牙/BLE等来支持高速数据采集的显示

- 大大降低了上位机的处理器资源需求,简化了上位机的程序设计