**这是本文档旧的修订版!**

I2C Master

1.概述

I2C是一种简单的串行通讯总线,由飞利浦公司在1980年代为让主板、嵌入式系统或手机用以连接低速周边设备而发展。自2006年11月起,I2C协议是可以被免费使用的,但是芯片厂商仍需要付费以获得I2C从属设备的地址。 I2C只使用两条双向漏极开路(串行数据SDA与串行时钟SCL)并利用电阻进行上拉,I2C允许相当大的工作电压范围,但典型电压等级为+3.3V或者5V。其设备地址包含7bit长度与10bit长度。I2C传输速率有不同的模式:

- 标准模式:100Kbit/s

- 低速模式:10Kbit/s

- 快速模式:400Kbit/s

- 高速模式:3.4Mbit/s

本IP的设计旨在使用户能够高效进行开发,减少开发周期。支持7位设备地址与标准/快速/低速模式,暂不支持10位地址操作模式,若相关器件性能支持,该IP也可运行在3.4Mbit/s(所使用的FPGA IO建立时间需满足时序要求)。

![]() 注意,该IP仅限学习与交流使用。

注意,该IP仅限学习与交流使用。

2.I2C Master 特性

- 符合Philips I2C标准

- 支持主动挂起I2C总线进入等待状态

- 支持多种传输速率

- 支持重复读/写操作

- 支持非标准I2C设备(如无寄存器地址操作)

- 提供ACK触发信号

- 提供状态调试寄存器

3.IP结构

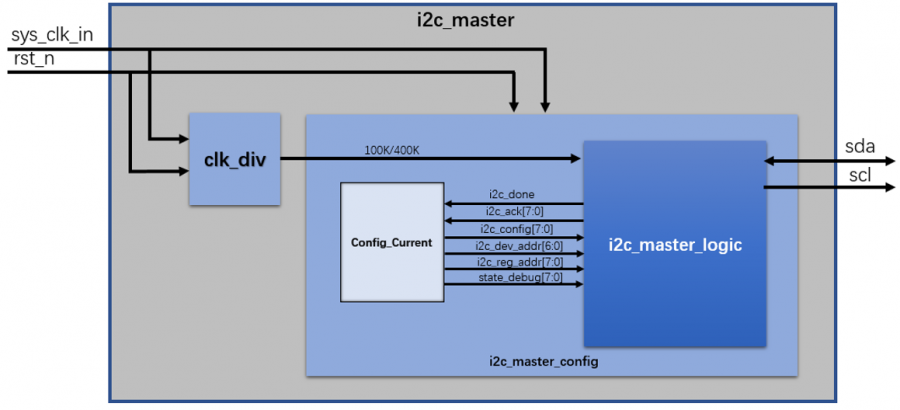

I2CMasterCore由4部分组成,分别为i2cmaster, i2cmasterconfig, i2cmasterlogic与clkdiv,功能分别如下:

- i2cmaster : 为内核的top module,调用所有module并建立连接。 * i2cmasterconfig : 为内核配置module, 用户可修改该module实现i2c通信。 * i2cmasterlogic : 为内部逻辑实现module,若预设操作模式没有涵盖到某种I2C设备,你可以自行修改该module中的内容,建立一种新的状态跳变模式。

* clkciv : 时钟分频module,可进行任意整数分频,点击详细了解。

4.Signal & I/O Ports

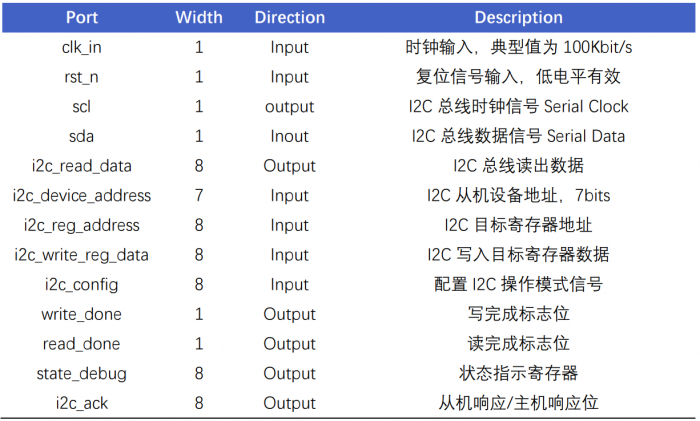

4.1 i2c_master_logic Module

i2cmasterlogic Module是I2C Master Core逻辑实现部分,所包含接口如下所示:

clkin :

clkin :

时钟输入信号,该信号直接影响I2C总线工作频率,典型输入频率为100Kbit/s,可使I2C总线工作在100K标准模式下,如果从机设备支持快速或高速模式,该时钟频率可响应输入更高频率,如400Kbit/s或者3.4Mbit/s。

rstn : 复位输入信号,该信号为被拉低时,电路进入复位状态。

scl&sda : I2C通讯总线,硬件电路需配置为上拉,管脚约束建议同样调整为为上拉。

i2creaddata : 该寄存器用于存储主机在从机中读取到的数据。

i2cdeviceaddress : 该信号为从机设备地址,暂只支持7位的设备地址。

i2cregaddress : 该信号为读/写操作目标寄存器的地址,由外部输入。

i2cwriteregdata : 该信号为I2C写入目标寄存器数据,由外部输入。

i2cconfig : 该信号为配置I2C工作模式的外部输入信号,本I2C Master IP核支持如下工作模式,分别对应输入信号为:

* i2cconfig = 8h00** : I2C挂起,进入等待模式(WAIT),等待状态下主机将SCL拉高并释放SDA总线。

* **i2c_config = 8h01 : I2C单次写入模式(I2CSingleWriteByte),标准1Byte数据写入模式。

* i2cconfig = 8h02** : I2C连续写入模式(I2C_Continuous_Write_Byte),主机对从机目标寄存器进行连续写入1Byte的数据,当主机发送到从机的1Byte数据并接受到ACK信号时,不会停止I2C总线,而是继续写入1Byte数据。该模式不会主动停止。

* **i2c_config = 8h03 : I2C直接写入状态(I2CWriteDirectly),主机直接对从机设备进行1Byte的数据写入,即成功访问到设备并接受到ACK信号之后,直接写入8bit的数据即可。

* i2cconfig = 8h04** : I2C单次读取状态(I2C_Single_Read_Byte),标准1Byte数据读取模式。

* **i2c_config = 8h05 : I2C连续读取状态(I2CContinuousReadByte),主机对从机目标寄存器进行连续的数据读取操作,即在通讯的过程中,主机成功读取从机目标寄存器数据后,不会发送NACK信号,而是发送ACK信号并再次读取从机目标寄存器的数据。

* i2cconfig= 8`h06** : I2C直接读取状态(I2CReadDirectly),主机对从机设备进行直接读取数据操作,即成功访问到设备并接受到ACK信号后,直接再次进行START模式,进行数据的读取。

statedebug:该信号为程序运行状态指示寄存器。

i2cack:该信号为响应指示信号,对应关系如下:

* i2cack[0] : 写入设备地址从机响应位

* i2cack[1] : 写入寄存器地址从机响应位

* i2cack[2] : 写入寄存器数据从机响应位

* i2cack[3] : 读取寄存器地址从机响应位

* i2cack[4] : 成功读取寄存数据后主机发送ACK

* i2cack[5] : 成功读取寄存器数据后主机发送NACK

* i2cack[4] : 预留,默认值为0

* i2c_ack[5] : 预留,默认值为0

4.2 i2cmasterconfig module

i2cmasterconfig module是主要功能为对I2C运行模式及寄存器地址、数据进行配置。相关寄存器与i2cmasterlogic module相同,在此不在赘述。

4.3 clkdiv module

本module为时钟分频模块,通过对系统时钟信号进行分频可生成I2C所需时钟,你可以点击此处了解该clkdiv module的详细说明。

===== 代码下载 =====

i2c_master_core.zip