**这是本文档旧的修订版!**

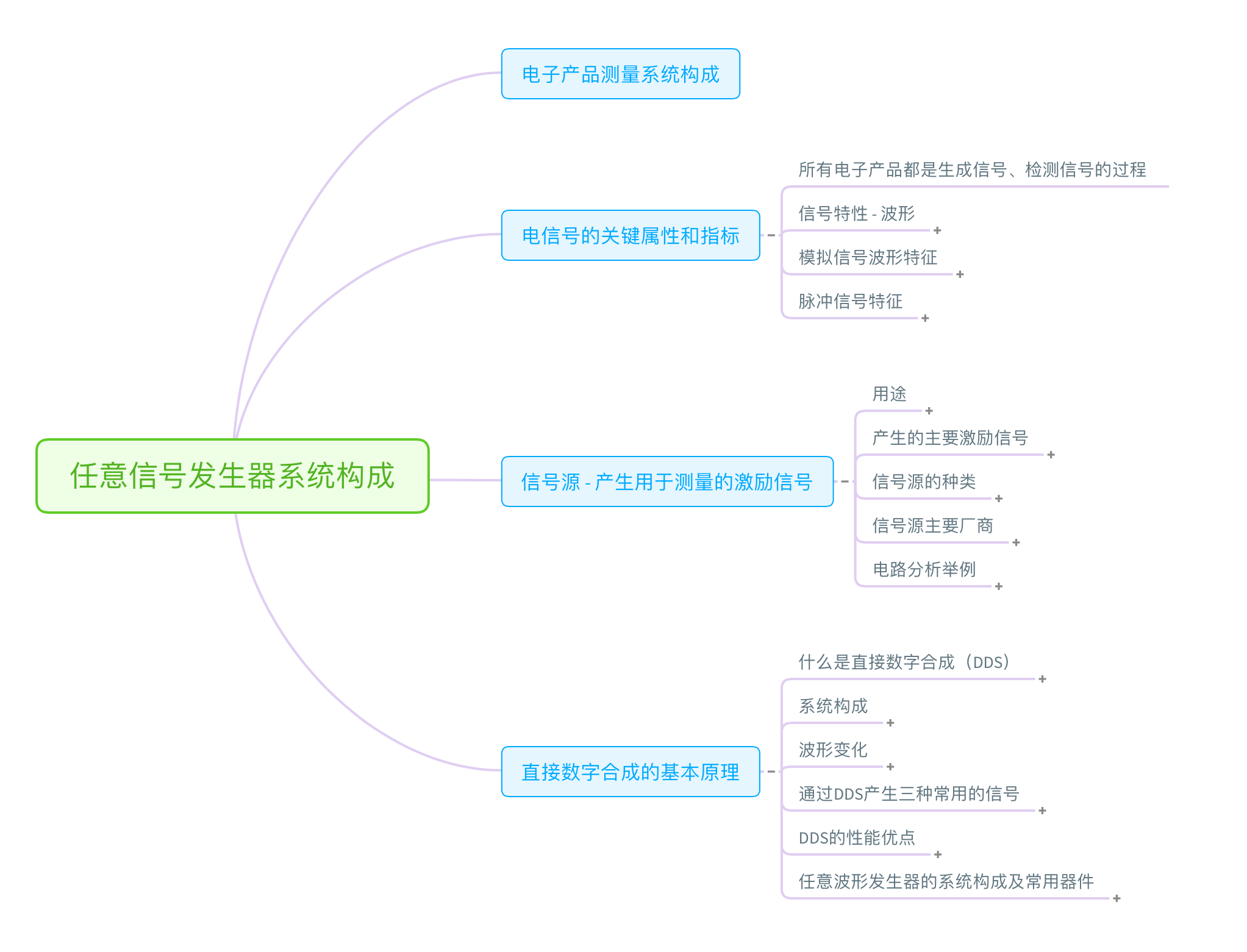

任意信号发生器系统构成

信号发生器类型比较多,在不同的场合可采用不同的信号发生器, 有函数发生器、射频微波信号发生器、任意波形发生器、数字模式发生器或频率发生器等,它们都是能够产生周期性或非周期型电信号(以模拟信号或数字信号的方式)的电子设备. 被广泛应用于设计、测试、调试以及维修等场合。

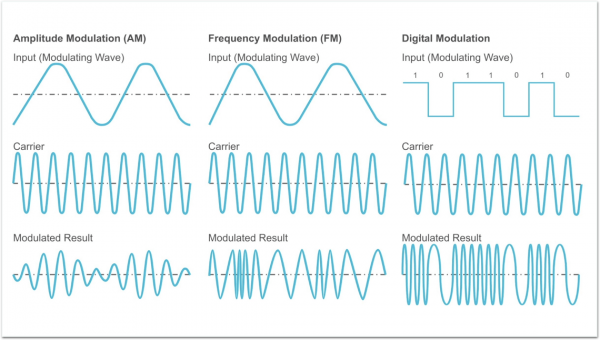

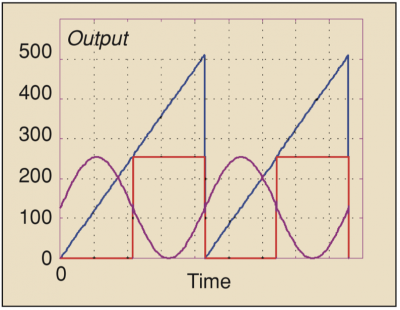

随着技术的发展,现在的信号发生器一般都是采用DDS合成技术的任意波形发生器,主要是采用FPGA或DSP器件在数字域来合成波形,再通过DAC产生模拟信号输出。最通常的波形是正弦波,但锯齿波、阶跃(脉冲)、方波、以及三角波这些波形可以非常方便地通过任意波形发生器来产生。如果振荡频率在音频的20KHz以上,发生器一般会包括一些调制功能,比如调幅(AM)、调频(FM)、调相(PM)以及第二个振荡器用以提供音频调制波形。

Rigol的任意信号发生器

本文的缩略架构

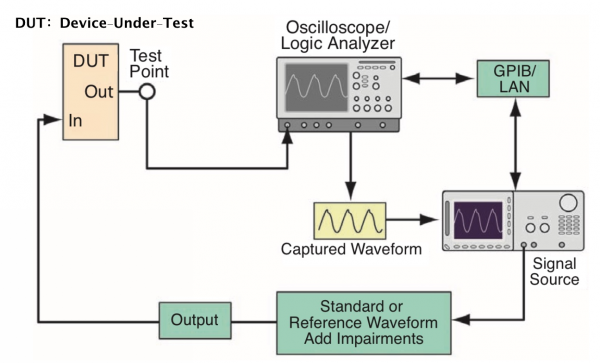

电子产品测量系统构成

电信号的关键属性和指标

所有电子产品都是生成信号、检测信号的过程

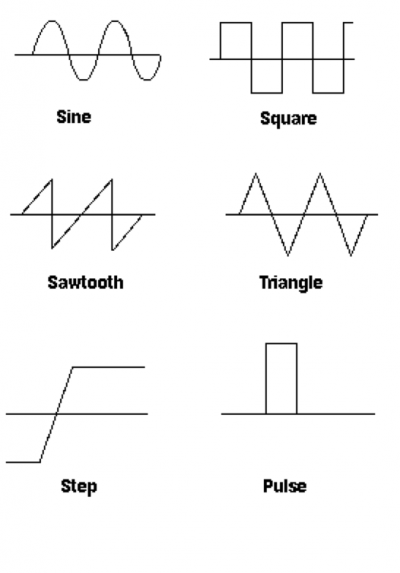

信号特性 - 波形

- 正弦波 - 是否存在失真、非线性、谐波?

- 方波 - 重复方波脉冲,用作时钟或测试运放的快速转换特性

- 锯齿波 - 缓慢上升、快速下降,用于控制模拟示波器或电视扫描

- 三角波 - 上升、下降时间相同

- 阶梯波 - 从一个电平快速变化到另一个电平

- 脉冲信号 - 快速上升时间、持续幅度、快速下降

- 任意波形 - 一般是包括无法用函数表示的其它波形

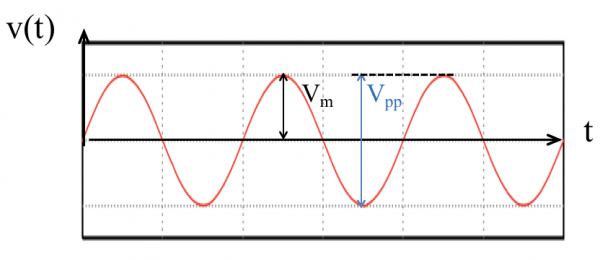

模拟信号波形特征

- 信号表达式 - V(t) = Vm sin(2πf t + φ) [V]

- 信号幅度特性

- 信号表达式 - V(t) = Vm sin(2πf t + φ) [V]

- 信号幅度特性

- 幅度 - 准确度、调节的分辨率

- 动态范围 - 从最小信号到最大信号的跨度(dB)

- 直流偏移 - 在交流信号上叠加的直流分量

- 输出阻抗 - 一般为50 Ohm

- 信号频域特性 - 频率

- 频率范围

- 频率准确度

- 频率稳定度

- 可调频率精度

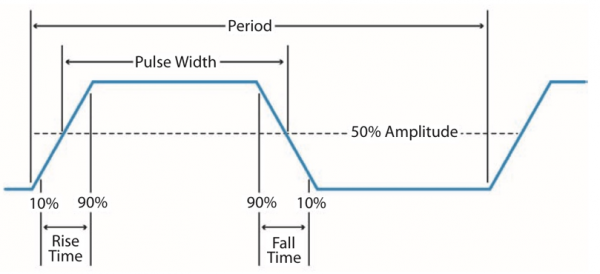

脉冲信号特征

信号源 - 产生用于测量的激励信号

用途

- 检查每一级电路的增益、频率响应,对接收端进行校准

- 信号源提供用于测试电路的各种波形,一般来讲都是低功率的

- 验证( Verification) - 分析数字调制

- 定标(Characterization) - 测试D/A和A/D转换器

- 压力/临界点 测试 - 通信接收机的压力测试

产生的主要激励信号

- 模拟波形

- 数字数据模式

- 调制信号

- 刻意产生的噪声,用以测试信道的特性

信号源的种类

- 函数发生器 - 输出标准的波形

- 模拟函数发生器 - 成本低、使用简单、频率无上限、精度低

- 数字函数发生器 - 用数字方式产生的标准波形

- 扫频函数发生器 - 输出信号的频率随时间周期变化

-

- 通用的任意波形发生器 - 通过DDS的方式产生

- 射频信号发生器 - 输出的模拟信号在射频频段

- 矢量信号发生器 - 用于通信系统的测试

- 音频信号发生器 - 用于音频信号的测试

- 逻辑信号源:输出脉冲或模式等数字模式

- 脉冲发生器 - 从小的输出数字驱动产生方波或脉冲串

- 模式发生器(数据发生器) - 可以产生很多通道的数字模式

- 模拟函数发生器 - 成本低、使用简单、频率无上限

- 单芯片模拟函数发生器MAX038

- 数字函数发生器 - DDS+DAC的方式,可调精度高

- 任意波形发生器 AWG

- 可以产生任意的波形

- 波形可以编辑

- 任意波形发生器产品举例 - Rigol

- 型号 - DG1022

- 输出:5种标准波形,并内建48种任意波形

- 调制:AM、FM、PM、FSK

- 提供:线性/对数扫频和Burst

- 正弦波:1μHz ~20MHz

- 方波: 1μHz ~ 5MHz

- 任意波形:1μHz ~ 5MHz

- 波形存储长度:1K个点

- 采样:100Msps/14bits

- 输出信号:2mVpp 到10Vpp (50Ω)

- 直流偏移:5V

-

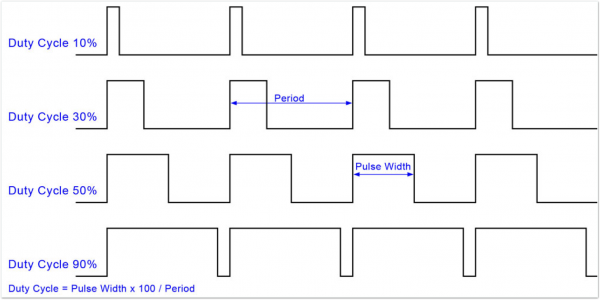

- 输出电平

- 周期、频率

- 脉宽、占空比

- 延时

- 单脉冲、重复脉冲

- 同步输出

- 信号发生器发展趋势

- 小型化/便携式

- 网络连接 - 以太网、WiFi、蓝牙

- 针对不同的应用 - 无线通信、工业物联网

信号源主要厂商

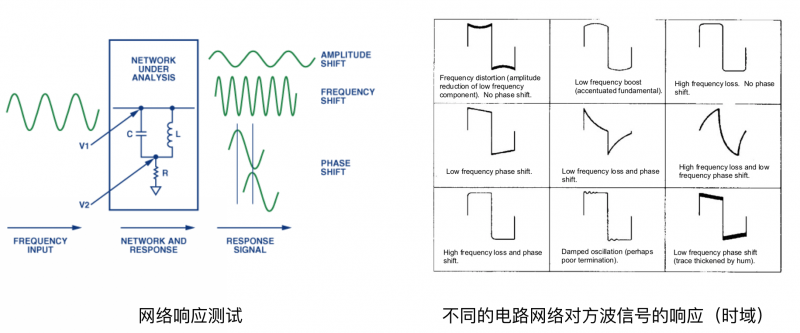

电路分析举例

- 网络响应测试 - 不同的电路网络对方波信号的响应(时域)

- 典型的频域谱线

- 连续波

- 网络响应测试 - 不同的电路网络对方波信号的响应(时域)

- 典型的频域谱线

- 连续波

- 产生单频、固定频率的正弦波

- 扫频

- 在一定频率范围内进行扫描

- 可能是相位连续的

- 信号发生器

- 添加了调制

- 产生“真实世界”的信号

- 信号频域特性 - 相位 - 单边信号 :差分信号 - 脉冲信号占空比/延时 - 复合信号

- 模拟调制、数字调制、脉宽调制、正交调制

- 数字模式和格式

- 伪随机数据流

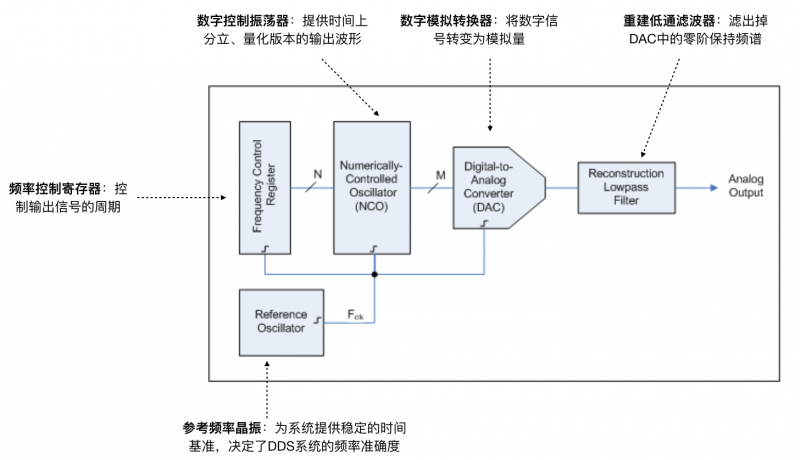

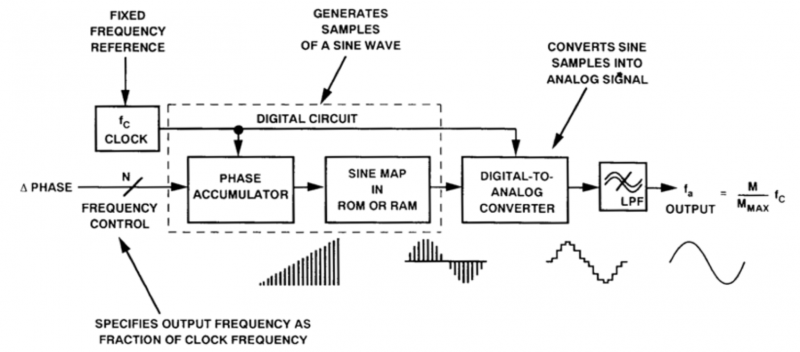

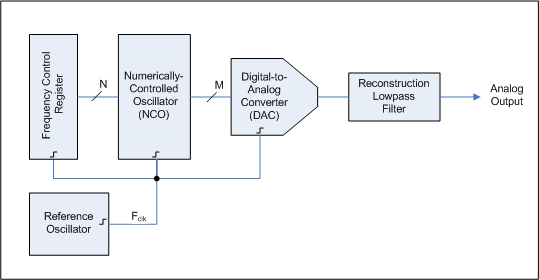

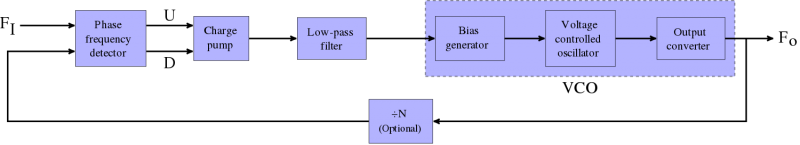

直接数字合成的基本原理

什么是直接数字合成(DDS)

- DDS - Director Digital Synthesis

- 是一种用于通过单个固定频率的参考时钟信号生成任意波形的频率合成器

- 很多现成的多通道、单芯片DDS,可以工作在3GHz的频率,输出DC-1000MHz的合成信号

- 频率和相位都可编程,不需要改变外围器件,全软件控制

- 应用于:

- 信号分析:信号发生器、函数发生器

- 通信系统:通信系统的本地振荡器、混频器、调制器

- 语音合成

- 数字锁相环 DPLL

- 生物医疗

系统构成

波形变化

通过DDS产生三种常用的信号

DDS的性能优点

- 优点:

- 更高的频率捷变性能

- 比参考源晶振相位噪声小的相位噪声

- 它是一个前馈系统,所以有很好的近载波相位噪声性能,DDS将参考时钟的相位噪声降低了Fclk/Fo

- 参考时钟的抖动直接影响了输出信号的抖动,此抖动相对于输出信号的周期比例很小

- DDS的最高输出频率为Fclk/2,输出信号的相位噪声永远会比参考时钟信号的相位噪声低至少6dB

- 在远离载波的频率区间,DDS的相位噪声本地为DAC量化噪声本底和参考时钟相位噪声本底的幂和

- 输出频率切换时可以保证精确的相位控制

- 可以工作在较宽的频率范围

- 精细的频率调整分辨率

- 缺点:

- NCO位数截断导致的杂波

- 相位截断导致杂散干扰

- 高阶奈奎斯特镜像导致的交互杂散

- DAC带来的在大的频率频率偏移情况下比较高的噪声底线

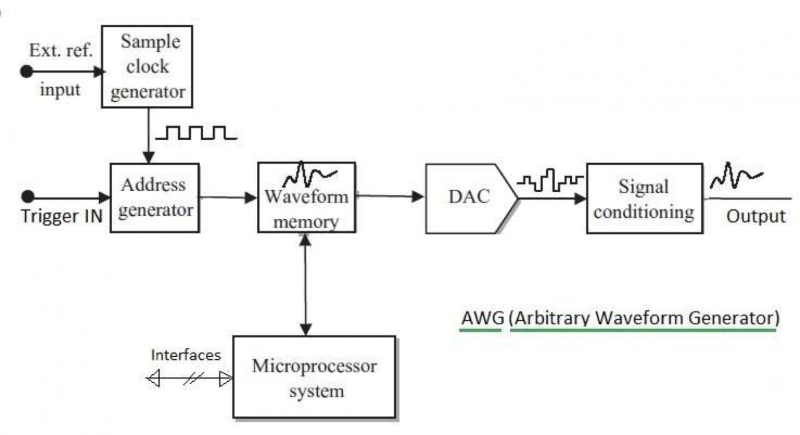

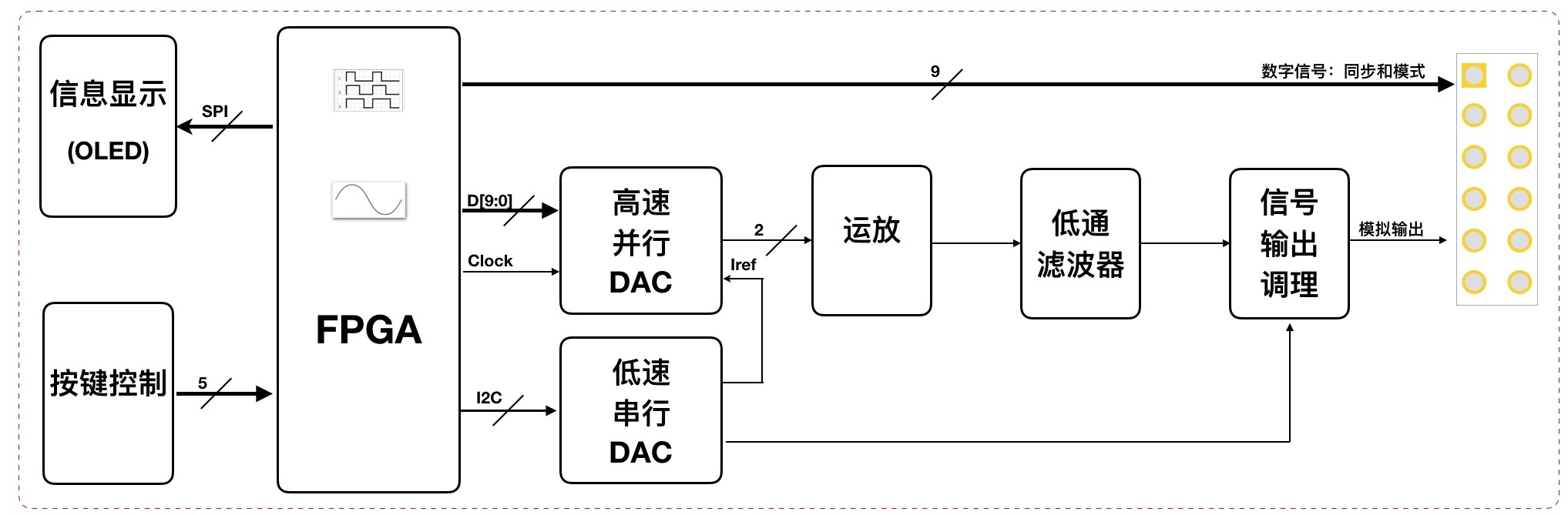

任意波形发生器的系统构成及常用器件

- 任意波形发生器两种构成方式

-

- 特点:

- 设计简单

- 价格便宜

- 性能好

- 波形固定

- 常用器件

- ADI DDS器件系列

- ADI DDS器件设计和仿真页面

- ADI经典的DDS器件AD9850 - CMOS, 125 MHz完整的DDS合成器

- 最高125 MHz 时钟速率

- 片上高性能DAC和高速比较器

- DAC SFDR > 50 dB @ 40 MHz AOUT

- 32-Bit 频率调整控制字

- 简单的控制接口:并行Byte 或串行加载格式

- 支持相位调制

- 3.3 V 或 5V单电源供电

- 低功耗: 380 mW @ 125 MHz (5 V),155 mW @ 100 MHz (3.3 V)

- AD9850的杂散信号强度

- AD9851: 180 MHz完整DDS频率合成器

- AD9852: CMOS 300MHz 全功能DDS芯片

- AD9854: 300MHz正交完备DDS芯片

- AD9102: 低功耗14位、180Msps DAC和波形发生器

-

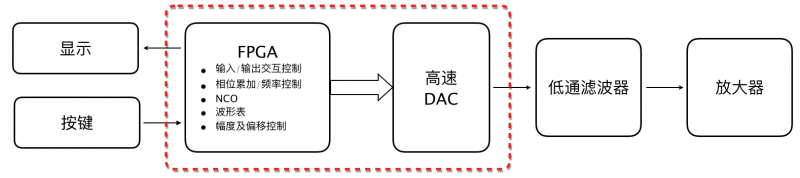

- 特点:

- 功能灵活

- 自定义波形

- 体验基本原理

- FPGA- 实现所有的数字逻辑及存储功能

- 实现相位累加器/查找表/波表ROM功能

- 产生DAC需要的取样时钟并满足并行数据传输到DAC所需要的时序

- 可以利用FPGA内部的Block RAM配置成存放波形的ROM表

- FPGA- 资源需求(举例)

- 波形表存储容量:1个周期:1024点 * 10bits ~ 10.24kbits (以10bits DAC为例)

- 4种波形 ~ 40.96kbits

- 逻辑资源 ~ 2KLEs

- 时钟频率100MHz,由内部PLL产生

- 高速DAC

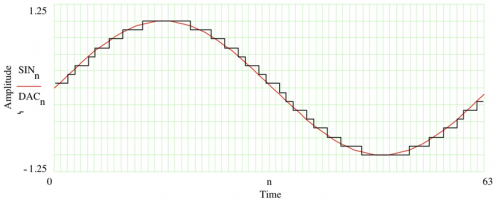

- 垂直(幅度)分辨率(转换精度):DAC的垂直分辨率决定了幅度准确度以及重生波形的失真

- 水平(时序)分辨率 - 产生的波形的最小的时间增量

- 量化误差/量化失真 - 由于DAC分辨率有限导致的两个取样间隔之间的输出信号和实际信号之间的误差

- DAC芯片举例 - AD974X - 210 MSPS TxDAC® D/A Converter: AD9748: 8bit,AD9740:10bits,AD9742: 12bits,AD9744:14bits

- 管脚都兼容的TxDAC 产品系列

- SFDR 到 Nyquist 在20 MHz 输出, 210 MSPS: 73 dBc

- 2的补码或直接二进制数据格式

- 功耗很低: 135mW @3.3 V (关电模式下仅15 mW)

- 具有片上1.20 V参考基准源

-

- 模拟信号域的处理

-

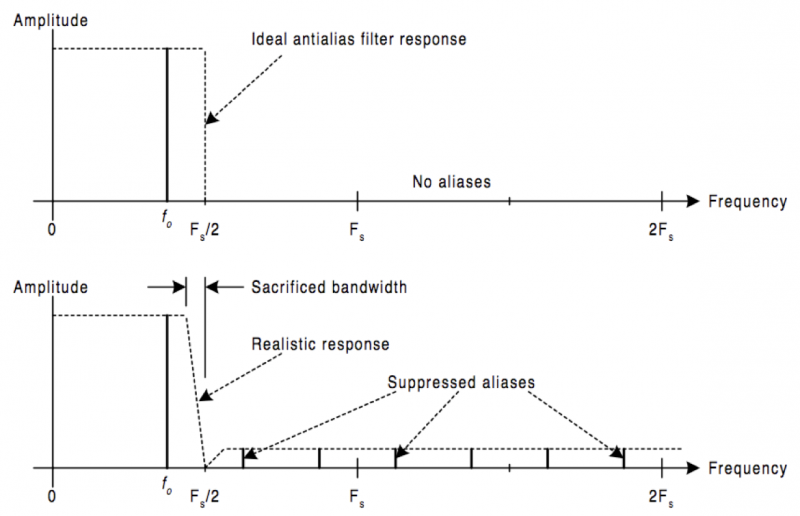

- 要求:

- 滤除掉DAC的零阶保持频谱

- 低通抗混叠滤波器

- 截止频率最高设定为Fclock的40%

- DDS输出频率的建立时间主要取决于重构滤波器的相位响应。理想的重构滤波器相位响应应该为线性,也即输出信号是输入信号的延时版本,这样就会在输出端有即时的频率响应,因为线性系统不会创造输入信号中没有的频率。

- 滤除带外的混叠和杂波干扰,带内幅频波动最小,相移为线性

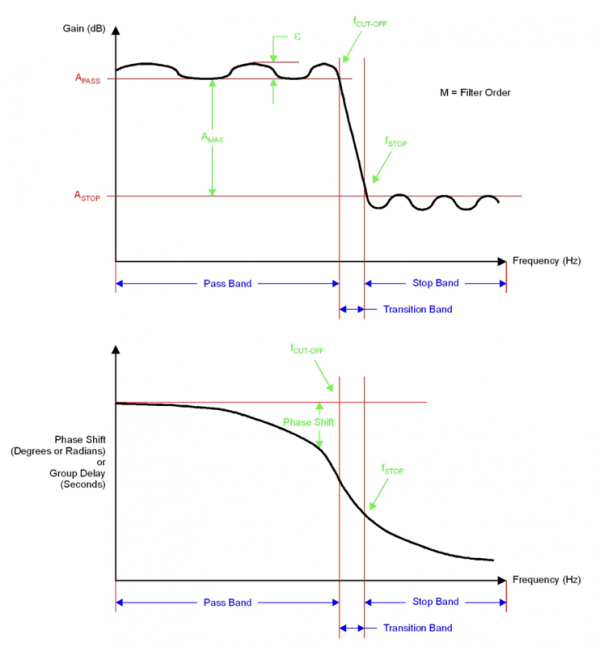

- 低通滤波器关键指标

-

- 带内衰减为零

- 带外抑制度最高

- 相移为线性

-

- 截止频率:DAC转换频率的40%

- 带外抑制度:尽可能高

- 带内平坦度:带内波动尽可能小

- 相位移动:线性

-

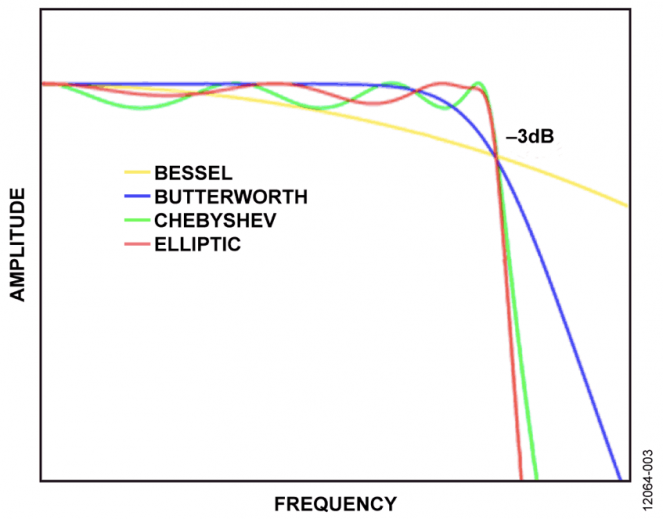

- 要综合考虑时域和频域的响应、群延时

-

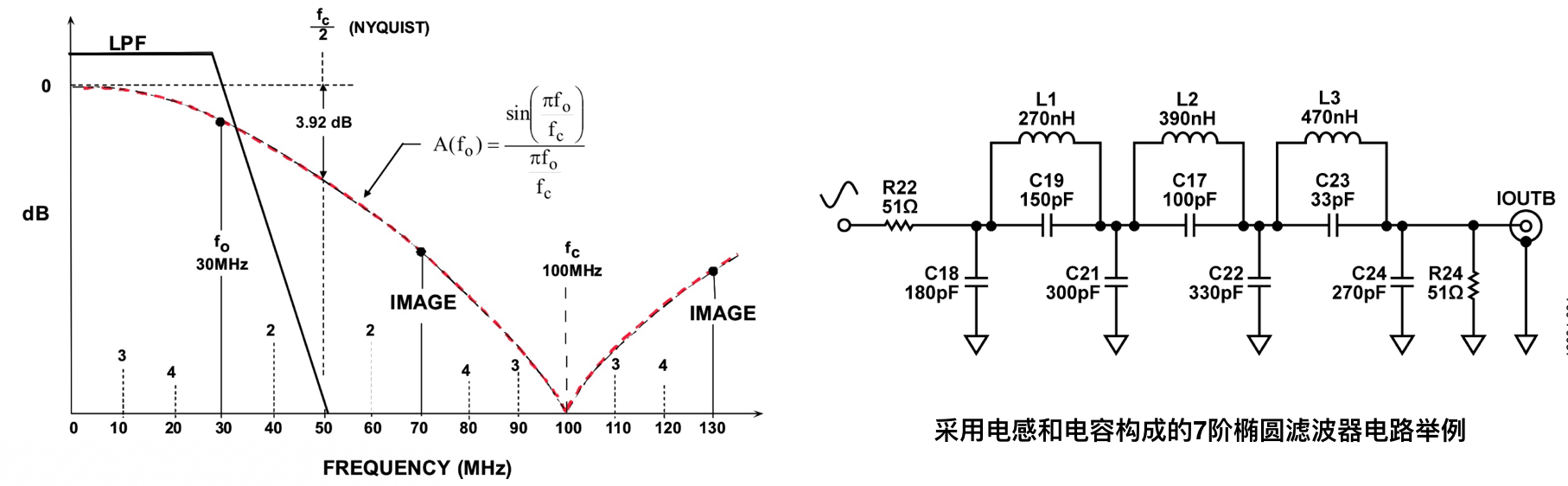

- DDS中为获得最大频率输出,一般设置截止频率:DAC转换频率的40%,采用椭圆滤波器能够达到最佳的带外抑制

- 在信号发生器中,为获得相对好的波形,至少一个周期有5个以上的采样点,设置最大输出频率为DAC转换频率的20%,采用巴特沃斯滤波器能够获得较好的带内平坦度

- 即便采用带内最为平坦的LPF,输出信号的幅度仍然受sinc函数的影响以及后续放大器的带宽限制,需要在数字域添加x/sinc(x)的补偿以及在LPF中添加在截止频率附近的高频补偿

-

- 滤波器设计及仿真工具

- Keysight ADS

- TI Webench

- Mathworks MATLAB

- NI MultiSim

-

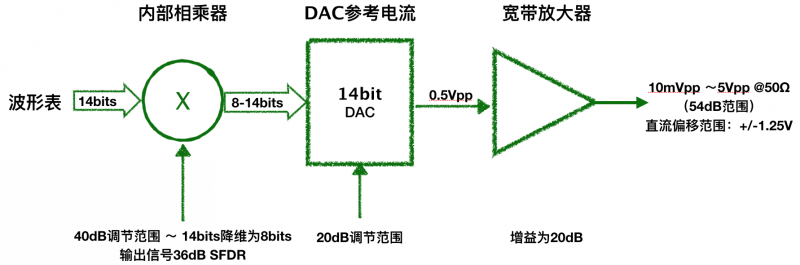

- 增益调整

- 内部相乘器

- DAC参考电流

- 宽带放大器

- 增益的调整以及响应速度的影响

- 直流偏移调整

-

-

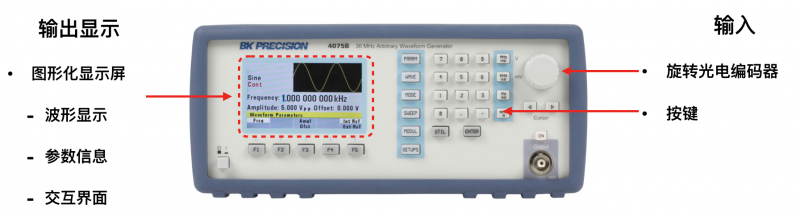

- 输入

- 旋转光电编码器

- 按键

- 输出显示

- 图形化显示屏

- 波形显示

- 参数信息

- 交互界面

文章、资料、应用指南

- MT-017: Oversampling Interpolating DACs (pdf)

- MT-014: Basic DAC Architectures I: String DACs and Thermometer (Fully Decoded) DACs (pdf)

- MT-015: Basic DAC Architectures II: Binary DACs (pdf)

- MT-016: Basic DAC Architectures III: Segmented DACs (pdf)

- MT-019: DAC Interface Fundamentals (pdf)

- AN-748 Set-Up and Hold Measurements in High Speed CMOS Input DACs (pdf)