**这是本文档旧的修订版!**

NIOS II系统入门实验

1. 实验内容

通过本实验熟悉SOPC Builder和NIOS IDE的开发环境及开发流程,了解NIOS II的基本结构,能够利用SOPC Builder和NIOS IDE实现简单的NIOS II系统和应用程序。

本实验要求利用SOPC Builder创建一个简单的NIOS II系统,这个简单的NIOSII 系统括NIOS核、片内SRAM及PIO口;利用NIOS II IDE创建一个简单应用程序,能够点亮核心板上的LED等。

2. 实验步骤

2.1 NiosⅡ硬件设置

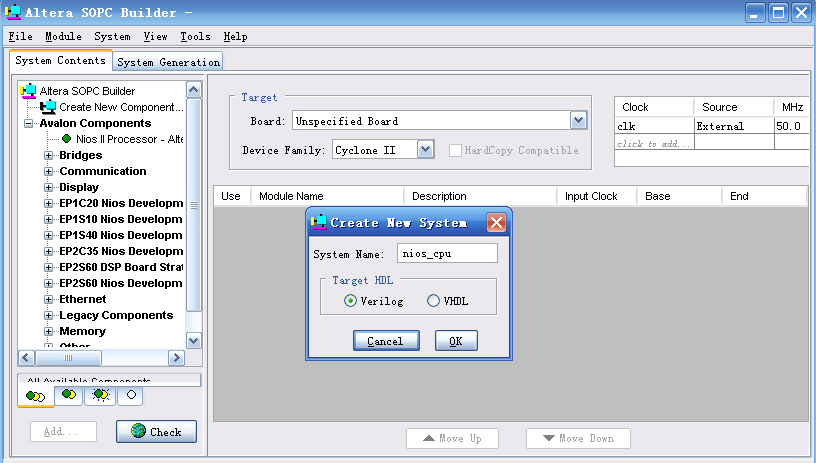

1. 工程建立:首先在Quartus II中新建一个名为nios的工程,点击 图标。出现SOPC Builder对话框。在System Name对话框里设置Nios系统名nios_cpu。HDL语言选择Verilog,如图21-1所示。

图标。出现SOPC Builder对话框。在System Name对话框里设置Nios系统名nios_cpu。HDL语言选择Verilog,如图21-1所示。

图21-1 SOPC Builder对话框

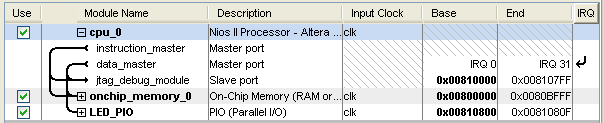

- SOPC组建添加:将Avalon Components中的选项中组建添加到自己的工程中,具体方法是将相关的组建拖进右边的对话框中,如图21 2所示。主要有Nios II Processor, Memory中的onchip_memory和Other里面的PIO。这里还需要会组建进行设置:

a) 双击Nios II Processor,选择Nios Ⅱ/e型,点击Finish。

b) 双击On-Chip Memory(RAM or ROM),Memory Type中选择RAM,Size中Memory Width选择32bits,Total Memory Size中选择48Kbytes,其余选项默认,点击Finish。

c) 双击PIO(Parall I/O),选项默认,点击Finish。

右键单击pio0选择Rename,改名为LEDPIO。

d) 点击System下拉菜单的Auto-Assign Base Addresses,已完成Nios Ⅱ中各个模块的基地址分配,以上步骤完成。

图21-2 nios系统配置

e) 点击System Generation,点击Generation,启动SOPC Builder生成你所选择的模块的HDL代码。

- 返回QUARTUS Ⅱ,新建nios.bdf文件,添加刚建的nios_cpu,并添加相应输入输出引脚,并为输入输出引脚分配相应的FPGA管脚,完成如图21 3,保存。编译通过BLASTER下载到FPGA内。

3. 程序设计

4. 仿真结果

5. 演示程序文件说明