# Analog Dialogue

A forum for the exchange of circuits, systems, and software for real-world signal processing

SINGLE-CHIP SURFACE-MICROMACHINED ACCELEROMETER (page 3)

Pulsewidth modulator increases laser-printer resolution (page 10)

High-performance ICs in single-supply analog circuits (page 15)

Complete contents on page 3

## Editor's Notes

The term "architecture" is classically defined as the art and science of designing and erecting buildings. Over time, it has come to connote the design and construction of practically anything, from ocean liners to written works, such as novels. In electronics, the term has come to mean the arrangement and

interconnection of the building blocks of computers and other circuits. The term encompasses both individual efforts (the Pantheon, the Pentagon, the Pentium) and classes of designs (houseboat, honeycomb, Harvard architecture).

In this issue we describe some new ICs with interesting circuit architectures—for example, an electronic circuit that involves tiny physical edifices; our cover story describes the complete-on-a-chip ADXL50 micromachined accelerometer circuit, which is designed with an eye to properties in both the electrical and mechanical realms. In the systems arena, we mention (p.23) a personal sound architecture (PSA).

Or consider the AD830 (page 8), a feedback amplifier with two additive differential inputs, termed officially a "high-speed video difference amplifier", because of its applicability as a video line receiver. However, its designer, Barrie Gilbert, points out that that name—based on one major application—may cause us to miss the boat for many other applications, because it doesn't suggest that the device has a new and unusual architecture. He points out that it could just as well be called a video summing amplifier, because it will take sums as well as differences.

More fundamentally, however, it could be called a voltagebalancing amplifier, since, with appropriate feedback, it implements the equation,

$$V_{X1} - V_{X2} = V_{Y2} - V_{Y1}$$

Well, that's the kind of name that might induce yawns among casual browsers through our catalog. The name that Barrie believes to be precisely right for this type of architecture is active feedback omplifier, because it achieves its function through the use of voltage feedback via an active voltage-to-current-converter stage; in so doing, it provides high-impedance differential signal-handling at both the input and feedback ports. We've tried to hint at this in our headline, which—with a twinkle—calls it an "uncommon-mode high-speed video feedback amplifier with a difference." Will Barrie ever forgive us?

Finally, we close with the architectural prediction that a future issue will feature a monolithic 3-volt fast floating-point processor bearing the toothy new class designation of SHARC: Super-Harvard-ARchitecture Computer.

## CORRECTION

The AD817 and AD818 op amps (Analog Dialogue 27-1, page 19) were designed at our Wilmington MA semiconductor facility by Moshe Gerstenhaber and Alex Gusinov. Michael Gianino was the product engineer.

Dan Sheingold

### THE AUTHORS

Bill Riedel (page 3) is Marketing Manager for accelerometers at the Wilmington, MA facility. Prior to joining the Transportation and Industrial Products Group, he spent several years in converter marketing. Before Analog Devices, he held sales and marketing positions with General Electric and Theta-J. He received his

BSEE from Brown University. His interests include automobile restoration, music, home brewing, bicycling and enjoying life.

Bill Schweber (page 10) is involved with press relations and marketing communications, and is Contributing Editor to Analog Dialogue. His photo and a biographical sketch appeared in Analog Dialogue 26-2.

Bill Slattery (page 12) is a Senior Product Marketing Engineer at our Limerick, Ireland facility (ADBV). Bill has marketing responsibility for video and computer graphics products including video RAM-DACs. Earlier, he worked in the ADBV Applications Group for six years, in support of video and computer graphics. Bill

gained his degree in Electrical Engineering at the University of Dublin (Trinity College). A licensed private pilot, he enjoys flying.

Walt Jung (page 15) is a Corporate Staff Applications Engineer, working out of Fallston, MD. His photo and a biographical sketch appeared in Analog Dialogue 26-2.

James Wong (page 15) is an Applications Engineering Manager at ADI's PMI Division in Santa Clara, CA, where he has worked for more than 7 years. He provides applications and design support to customers, publishes numerous technical articles and application notes, and is responsible for the SPICE model development

program for ADI. He holds a BSEE from San Jose State University and an MBA from Santa Clara University. He enjoys reading, golf, and discovering things with his children.

(More owhers on page 34)

Cover: The cover illustration was designed and executed by Shelley Miles, of Design Encounters, Hingham MA.

## Analog Dialogue

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Published by Analog Devices, Inc. and available at no charge to engineers and scientists who use or think about t.C. or discrete analog, conversion, data handling and DSP circuits and systems. Correspondence is welcome and should be addressed to Editor, Anolog Diologue, at the above address. Analog Devices, Inc., has representatives, sales offices, and distributors throughout the world. For information regarding our products and their applications, you are invited to use the enclosed Business Reply card, write to the above address, or phone 617-937-1428, 1-800-262-5643 (U.S.A. only), or fax 617-821-4273.

## A Surface-Micromachined, Monolithic Accelerometer

ADXL50: the first commercially available surface-micromachined device.

All signal-conditioning circuitry is on-chip by Bill Riedel

The ADXL50\* is a complete acceleration measurement system on a single monolithic chip. It's based on a differential capacitive, surface-micromachined polysilicon accelerometer integrated with signal conditioning circuitry, including a TTL-compatible self-test feature. The ADXL50 measures accelerations from 0 g to ±50 g with bandwidth from dc to 1 kHz, producing an output voltage proportional to the acceleration. This makes it the first commercially available monolithic device to successfully incorporate traditional electronic semiconductor circuits with micromachined structures.

The ADXL50 is fabricated on Analog Devices' conventional BiCMOS production line which has been used extensively in the company's high-performance mixed-signal products. A surface-micromachining process produces tiny, highly complex mechanical structures from silicon (see sidebar on page 5, "Silicon that moves"). Since it uses many of the processing steps ordinarily used to manufacture traditional linear circuits, surface-micromachining lends itself readily to producing devices which combine both micromachined (mechanical) and semiconductor (electronic) elements on the same die. The ADXL50, exploiting this attribute, includes all necessary signal-conditioning, excitation, and test circuitry. Three external capacitors and a +5-volt regulated power supply are all that is required to measure accelerations to ±50 g.

The micromachined sensor behaves electrically like a variable differential capacitor operating in a force-balance electronic control loop. The result is a measuring system that, unlike piezo-resistive micromachined devices, is inherently stable over wide temperature ranges and—because it balances electrostatic force against acceleration force—is relatively independent of the mechanical properties of silicon. This force-balanced design also produces a very linear response due to the resulting minimal physical excursion of the beam during a broad range of acceleration values; typical nonlinearity is <0.2%.

A unique capability of the ADXL50 is a digitally activated self-test function which allows the sensor beam to be electrostatically deflected at any time to verify the integrity of the sensor element. This tests its ability to respond to an acceleration force (and provide a warning in case of malfunction)—a "must" in applications such as airbag systems in automobiles.

## MEASURING ACCELERATION

Conventional techniques for detecting and measuring acceleration are all founded on principles first discovered by Newton and

\*Use the reply card for technical data. Circle 1

outlined in his *Principio* in 1687. Newton's classical view holds that acceleration of a constant mass implies a force (F - ma, where F is force, a is acceleration, and m is mass). Most accelerometers operate by detecting the restoring force exerted on a mass by an elastic restraint.

Consider a simple mechanical system consisting of fixed mass, m, attached to a spring with stiffness, k. If the mass is displaced a distance, x, due to acceleration, the restoring force of the spring is F = kx. Substituting into Newton's equation, we find that a = kx/m and can derive the magnitude of the acceleration by observing the displacement, x, of the restrained mass. This fundamental principle is used by even the most sophisticated and expensive electromechanical accelerometers; it is also how the micromachined ADXL50 works.

## SENSOR MECHANISM

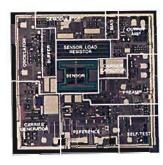

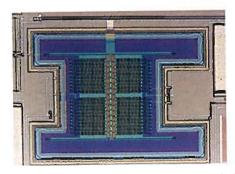

Figure 1 shows the layout of the ADXL50 chip. The heart of the chip is the surface-micromachined sensor located at the center of the die (Figure 2). Measuring only 500  $\mu$ m  $\times$  625  $\mu$ m (less than 1/2 mm²), the ADXL50 sensor resembles the letter "H" when viewed from above. The long, thin legs of the "H" are tethers that anchor the micromachined element to the substrate; they are the only electrical and mechanical contact between the sensor structure and the rest of the chip. The tethers form the spring system

## IN THIS ISSUE

Volume 27, Number 2, 1993, 36 Pages

| Editor's Notes, Authors                                                    |

|----------------------------------------------------------------------------|

| A starface-micromachined monolithic accelerometer (ADXL50)                 |

| "Uncommon-mode" high-speed video amplifier with a difference (AD\$30) 1    |

| CMOS 10-bit, 15-MHz, +5-V A/D converser for imaging apps. (AD875) 1        |

| Increase laser-printer resolution with pulse modulator (AD9560) 10         |

| Video RAM-DACs offer unprecedented resolution, true-color (ADV715x) 13     |

| Fast, accurate 10-bit 40-MSPS monolishic sampling ADC (AD9040A) 1-         |

| High-Performance ICs in single-supply analog circuits                      |

| New-Product Briefs:                                                        |

| What's new in DSP: 3-V DSP, MS processors, brief briefs 2                  |

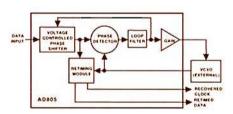

| Chips for communications: Ports, PLLs, Synthesizers                        |

| Sampling ADCs for size, power, channels, resolution                        |

| Single or multiple Op Amps for every reason                                |

| DACs, References, Color Encoder, and Much More                             |

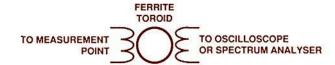

| Ask the Applications Engineer - 14: High-frequency signal consumination 21 |

| Ideas for Design                                                           |

| High-performance infinite sample-holds and peak followers 30               |

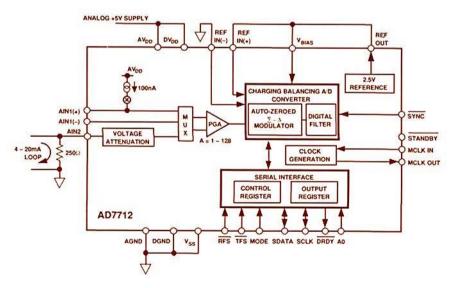

| Digitize 4-20-mA current signals with one chip                             |

| Digitize strain-gage bridge directly                                       |

| Three new ADI fellows: Mohammad Nasser, Brad Scharf, Jim Wilson 33         |

| Worth Reading, more authors                                                |

| Рогрошті                                                                   |

|                                                                            |

Figure 1. Layout scheme of the ADXL50 chip.

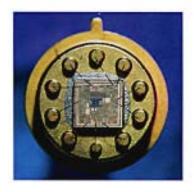

that suspends the central test (or proof) mass (the crossbar of the "H") in tension within a well in the substrate; the mass is free to move in a direction perpendicular to the tethers (along the axis of the "H" crossbar), in the same plane as the substrate surface. When the device is packaged in a TO-100 metal can, the package tab is aligned with the "H" crossbar, showing the direction of sensitivity (see photo on page 3).

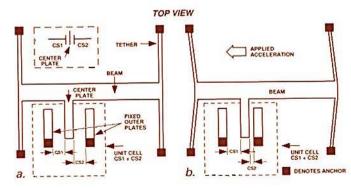

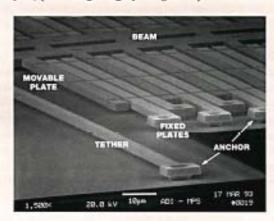

Projecting from the central proof mass is a series of regularly spaced filaments resembling the fingers of a comb (Figure 2). Each of these filaments is actually one plate of a series of parallel-plate variable capacitors; the other plates are attached to the chip substrate and interdigitate with the plates attached to the freely moving proof mass. Altogether, 42 moving capacitor plates (interdigitated with the fixed plates), attached to the sensor proof mass, are connected in parallel electrically for a total capacitance of only 0.1 pF. The plates anchored to the moving mass form the central plate of a three-plate differential capacitor structure. The plates anchored to the substrate and interdigitated with the moving plates are alternately connected in parallel; the effect is of two capacitors sharing a common plate, with capacitances of  $Cx_0/(x_0 + x)$  and  $Cx_0/(x_0 - x)$ , where  $x_0$  is the center position and x is the deflection caused by the acceleration (Figure 3).

Conceptually, the force exerted on the central proof mass by acceleration or deceleration in the direction of sensitivity causes it to move against the spring force of the tethers. This changes the relative spacing between the moving and fixed capacitor plates. The motion causes a fractional increase of capacitance on one side and a corresponding decrease on the other. The relative change in capacitance is proportional to the magnitude of acceleration, so acceleration can be determined by continually monitoring the electrical effects of capacitance changes.

Figure 2. The acceleration sensor. Acceleration axis is vertical.

In actuality, the sensor operates within a force-balance electronic control loop; the proof mass, when accelerated, is restrained from moving (i.e., nulled, in the same manner as the summing point of an inverting operational amplifier) by the application of an opposing electrostatic force, generated by applying an inverted

version of the output voltage to the capacitor plates. This feedback produces a system which behaves essentially like one with a much stiffer spring constant (less nonlinearity and good temperature stability).

The physical shape and layout of the ADXL50's capacitive sensor fulfills a requirement for simplicity. The sensor is formed from a single layer of polycrystalline silicon. Since capacitor density (the number of elements with a given capacitance that can be placed within an area) is proportional to 1/d, where d is the width and spacing of the plates, this feature is patterned using extremely fine lithographic fabrication and etching tools. Careful consideration of stresses in the polysilicon which forms the sensor allows these small structures to remain essentially level when suspended freely above the substrate. The sensor tethers—the finest structures—measure about 2 µm on a side and are about 200 µm long. The total physical mass of the measurement beam (proof mass) is less than 0.1 microgram. At rest, the spacing between adjacent capacitor plates is less than 2 µm.

At these dimensions, silicon is highly elastic, easily withstanding shock and vibration—making it an ideal material for constructing finely patterned mechanical structures. In fact, on this scale, silicon has mechanical properties similar to those exhibited by steel at larger dimensions. As a result, the ADXL50's sensor is able to withstand physical shocks of 2000 g in any direction without suffering damage or deterioration in performance.

### CIRCUIT TECHNOLOGY

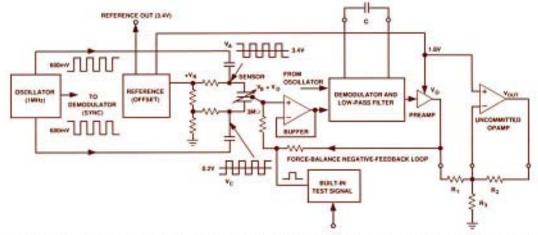

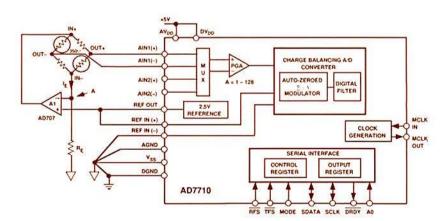

The complete chip measures approximately 9 mm<sup>2</sup> and is dominated by the signal-conditioning circuitry, which surrounds the centrally located (< 1-mm<sup>2</sup>) sensor. The circuitry includes a push-pull oscillator, carrier generator, reference, preamplifier, self-test circuit and an uncommitted output amplifier—providing a high level of system integration (Figure 4\*).

The sensor, described earlier, consists of a pair of differentially varying capacitors that respond to the displacement of the mass. Square waves,  $V_A$  and  $V_C$ , at 1 MHz—of equal amplitude but 180° out of phase with one another—are applied to opposite plates of the capacitor pairs. Within each pair of plates, one side is biased to 3.4 V, the other to 0.2 V. The voltage at the proof mass, their electrical node, represents the degree of unbalance. At 0 g of acceleration, the central, moving set of capacitor plates is equidistant from each of the substrate-connected outer plates; their capacitances are equal, and—as a result—the two antiphase signals are equally coupled to the central plate and cancel each other, producing a nominal output voltage of 1.8 V (the midpoint of the 0.2-V and 3.4-V biased plates).

Figure 3. Simplified detail of the acceleration sensor showing one element of the differential capacitor.

Figure 4. Simplified circuit details, showing the signal-conditioning circuitry and force-balance feedback loop of the ADXL50.

## SILICON THAT MOVES

Micromachining is a processing technique used to manufacture tiny mechanical structures from silicon. A silicon wafer of the type used to make semiconductors can be etched (or modified) to produce small beams, masses, gears, and other structures measuring only a few thousandths of an inch.

Micromachining comes in two varieties: surface and bulk. Prior to the ADXL50, all the available micromachined devices used bulk micromachining. It was discovered in the 1950s that acid solutions attack different planes of crystalline silicon at different rates, depending on the crystal orientation. By exposing an area of silicon with a specific crystalline structure to acid, cavities with precisely angled walls are created.

Bulk micromachined accelerometers have existed for several years. Typically they consist of a membrane or diaphragm of silicon, roughly 10 µm thick, that is vertically formed in the wafer by chemical etching. In the center of the membrane is a large mass of silicon. On the top surface of the device, near the edge of the membrane, thin-film piezo-resistors sensitive to strain and deformation are deposited. Most of the membrane is removed, leaving tethers with these resistors suspending the central mass. Vertical acceleration causes the test mass to move, deforming the diaphragm and changing the resistance of the piezo-resistors. Bulk micromachined devices are large by IC standards-about 20× the size of the surface-micromachined ADXL50. Large size, coupled with the fact that the process for manufacturing bulk micromachines is inconsistent with semiconductor-circuit fabrication techniques, requires that signalconditioning be off-chip. Bulk-piezo-resistive accelerometers are very sensitive to temperature effects and difficult to test fully.

When the sensor experiences acceleration along the axis of sensitivity, the separations between adjacent plates will become unequal; one capacitance will increase while the other decreases. The 0.1-pF total capacitance generated between the beams changes by ±0.01 pF for ±50-g accelerations. The sensor structure can actually resolve as small a change as 20 attofarads (20 × 10<sup>-18</sup> F), corresponding to a beam displacement of 0.2 Å. This resolution is a consequence of the precision of the associated signal-conditioning circuitry.

The output from the sensor array is a biased high-impedance square wave, V<sub>B</sub>. This output is buffered and presented to the \*Reprinted with permission from Electronic Design (Vol. 39, No. 15), August 8, 1991. Copyright 1991, Penton Publishing Inc.

Surface micromachining, a more sophisticated technique than bulk micromachining, creates much smaller, more-intricate and precisely patterned structures. It adapts manufacturing techniques perfected for making ICs to produce mechanical structures close to the surface of the silicon substrate. Chemical machining is accomplished by depositing, then etching, multiple thin films and layers of silicon and silicon-oxide to form complex mechanical structures. The feature dimensions of surface micromachined devices are typically 1 to 2 µm, similar to the feature dimensions of conventional electronic circuits. Most importantly, surface micromachining lends itself to the inclusion of conventional electronic circuitry on the same die. Thus, the surface-micromachined ADXL50 includes signal conditioning, resulting in a fully scaled, -referenced and -temperaturecompensated volt-level output. Surface-micromachining leverages the cost economies of standard IC wafer-processing techniques, producing a highly integrated product at low cost.

input of a phase-sensitive demodulator, which is synchronized with the 1-MHz carrier; it rectifies and low-pass filters the signal. The single-pole filter's cutoff frequency is established by a single external capacitor; for example, 25 nF for 1 kHz.

The synchronous demodulator drives a preamp, which is referenced to +1.8 volts. The output of the preamp is fed back to the sensor through a 3-M $\Omega$  isolation resistor. This feedback voltage, applied to the sensor plates as a bias, causes an electrostatic restoring force to oppose the sensor's motion. In effect, the force-balance control loop acts to keep the sensor from moving, holding it close to its at-rest position. The correction voltage required to hold the sensor's proof mass (or central plate)

in the 0-g position is a direct measure of the applied acceleration. This voltage is available to the user at the output of the preamp.

The ADXL50 chip also contains an uncommitted op amp. Without further conditioning, the output of the single-supply ADXL50's preamplifier is 1.8 V at 0-g acceleration, with a span of approximately  $\pm 1$  V for a  $\pm 50$ -g acceleration range (i.e., 19 mV/g). The uncommitted op amp can be used to alter the 0-g voltage and/or amplify and filter the acceleration signal. In Figure 4, the noninverting input of the op amp is connected to  $\pm 1.8$ -V signal, derived from an internal precision  $\pm 3.4$ -V reference source. The scaling factor in the diagram is given by the ratio,  $-R_2/R_1$ , (since the amplifier is in inverting mode). For independent adjustment, gain is adjusted with  $R_1$  and offset is adjusted with  $R_3$ . Therefore, if the span desired is  $\pm 2.25$  V for the complete  $\pm 50$  g range,  $R_2/R_1$  should be chosen such that:

$$\frac{R_2}{R_1} = \frac{V_{n \, spon}}{V_{pr \, span}} = \frac{2.25}{1.0}$$

where  $V_{pr,span}$  is the output from the preamplifier and  $V_{o,span}$  is the desired span of the uncommitted amplifier output. Thus:

$$R_2 = 2.25 \times R_1$$

$R_3$  can be found from the following standard equation:

$$R_3 = 1.8 \text{ V} \frac{R_2}{V_{60} - 1.8 \text{ V}}$$

where  $V_{\nu 0}$  is the 0-g output level. Stated otherwise,

$$V_{o0} = 1.8 V \left(1 + \frac{R_2}{R_3}\right)$$

With  $R_1 = 100 \text{ k}\Omega$ ,  $R_2 = 225 \text{ k}\Omega$ , and  $R_3 = 579 \text{ k}\Omega$ , the output analog signal range will be +0.25 to +4.75 V for  $\pm 50$  g, with +2.5 V at 0 g. With 25 nF, the output signal's -3-dB bandwidth is 1 kHz, using the single-pole, 1-kHz filtering of the preamp. More-sophisticated configurations can provide multi-pole filtering without the use of additional active components.

## **SELF-TEST**

Another unique attribute of the ADXL50 that sets it apart from alternative designs is the inherent ability to self-test the sensor and all associated on-chip signal-conditioning circuitry in place by applying a digital command. Most rudimentary sensors—particularly the commonly used electromechanical devices—cannot be adequately tested to ensure they are operating correctly. Even sophisticated sensors with accurate, continuous outputs can only be tested under controlled circumstances on precision vibration test-beds.

To self-test the ADXLSO, a CMOS- or TTL-level digital stimulus is applied to the self-test input. This produces a voltage pulse which is injected into the feedback signal to the sensor. The resulting electrostatic force causes a deflection of the proof thas against the tethers as though it were responding to a negative full-scale acceleration. Though always available, self-testing would generally be programmed to occur each time at power-up.

### **AUTOMOTIVE APPLICATIONS**

There are many on-board automotive systems that need a reliable, low cost way to measure acceleration. The most obvious and immediate application for the ADXLSO is in next-generation, single-point air-bag systems (see sidebar, "Air-bag Accelerometers"), where the ADXLSO's output provides acceleration

information for the "is-a-crash-occurring?" decision to initiate the explosive charge to deploy the air bag.

Another automotive application of accelerometers related to safety is in automatic door-lock-release mechanisms. In the event of a collision that results in significant structural damage to the vehicle, passengers are often trapped in the vehicle, unable to be rescued, because the doors remain locked. Automatic door-lock release on impact could, in many instances, have prevented this; an accelerometer incorporated in the door lock would detect the rapid deceleration that occurs on impact, releasing the door locks.

Airbag systems and automatic door-lock release systems are forms of "passive safety" which make the consequences of collisions less dangerous. In addition, automobile companies are developing "active safety" systems which attempt to avoid collisions. Such systems include ABS (antilock brake system), ASR (acceleration slip regulation), and sophisticated new suspension systems that monitor and react to varying road conditions; in addition to increasing the level of safety, these also provide a more comfortable ride through improved vehicle control. Active suspension systems continuously monitor road conditions and vehicle dynamics and compensate through the use of power hydraulics and actuators in the suspension to restore the vehicle to a neutral orientation (or even a biased orientation, "leaning" into a corner for improved control). A simplified version is known as an adaptive suspension system, which responds to road conditions and vehicle dynamics by altering the response of the suspension components through changing such parameters as shock absorber or strut valving; the difference is that it does not employ restorative power devices. Both active and adaptive systems rely on measuring shock and vibration through monitoring wheel- and body motions—functions requiring the use of accelerometers.

An advanced form of vehicle control, derived from ABS/ASR systems, is based on monitoring lateral acceleration; when it is combined with longitudinal acceleration and vehicle velocity values, suspension settings may be altered side-to-side or front-toback to make maximum use of the adhesion potential of the tires. Developments in this area include "yaw-rate" sensors, a special category of accelerometer which measures the rate of rotational velocity change. The resulting information may be used by the chassis control system to alter suspension settings as well as to more actively intervene in vehicle dynamics by selectively applying individual wheel braking (without driver input!). Selectively applying particular braking combinations applies yaw moments to counter undesired rotations of the vehicle. Various forms of such systems are already being used in racing applications such as "Indy" cars. As the cost of such systems is reduced, they will find use in vehicles for the general public.

The full-scale acceleration range of interest for suspension and "active-safety" applications is in the range of  $\pm 2 g$ , for which Analog Devices is developing future versions of the ADXL50.

### NON-AUTOMOTIVE APPLICATIONS

Acceleration is a fundamental physical quantity, manifested in many guises—gravity, vibration, and seismic activity are a few examples. Measuring acceleration continuously, accurately, and at low cost opens up numerous applications for the ADXL50 and future members of its family.

Manufacturers of portable computers continue to seek ways to make their products more rugged and reliable. The elements most prone to damage (and the catastrophic loss of stored information) are mass-storage devices, particularly hard-disc drives. The delicate mechanism that reads and writes information to the discs floats above them on a controlled flow of air; sudden movement can easily cause a problem, destroying data and drives alike. An accelerometer can detect the onset of potentially damaging shocks and institute "countermeasures" to prevent disc damage.

Many of us have had the disappointing experience of opening a large package to find the delicate contents damaged or destroyed due to mishandling. How did the damage occur, and who is to blame? If a package recorder—consisting of an accelerometer, a timer, and a data logger—were included with the consignment, these questions could be easily answered. Such recorders may soon be the norm for delicate, expensive items in transportation.

Military applications include smart detonation systems for missiles and bombs. Here an accelerometer forms part of the fuze system, detecting impact by the associated rapid deceleration. The continuously varying output of the ADXL50 would be quickly analyzed to establish the precise instant when the explosive charge should be detonated to produce maximum target damage.

The ADXL50 can also be used to monitor the health of machines. Rotating machines exhibit characteristic vibration signatures; as fatigue cracks or wear develop in portions of the machine, the signature changes. By continuously monitoring the machine's vibration, it is possible to be warned of imminent failure. Applications range from aircraft engines to heating, ventilation and air-conditioning (HVAC) systems.

## **FUTURE DEVELOPMENTS**

The ADXL50 is Analog Devices' first micromachined acceleration sensor. It is the first of a family which will include a more sensitive device with a full-scale range of ±2 g, a less-sensitive device for more-severe shock measurements, digital-output devices, and other formats. Also in development is a family of rate sensors. Future devices will also be available in a variety of packages.

Since the micromachined sensing element is so small, it is possible to incorporate several on a single chip, oriented to either the same or orthogonal axes. Thus monolithic dual-axis sensors can be constructed, allowing vector measurements of acceleration in the plane of the chip surface. Alternatively, two or more sensors can be aligned in the same plane, allowing for redundant sensing in fail-safe applications. In either instance, some sharing of the support circuitry (and perhaps even on-chip signal processing) will provide even greater economic value. Until multiple devices become available, the ADXL50's small size permits a high degree of compactness using separate devices.

The ADXL50 is available in a 10-pin T0-100 metal can with various grades, suitable for consumer, industrial, military, and automotive applications. DIP packaging is also in development. Pricing is \$38.50 in 100s, decreasing to <\$10 in large volumes.

The team that developed the ADXL50, headed by Dr. Richard Payne, includes Steve Sherman, Terry Core, Sarkis Ourfalian, Bob Tsang, Dave Quinn, Paul O'Brien, John Chang, Carl Roberts, Lew Long, and many others at ADI's manufacturing plant in Wilmington MA.

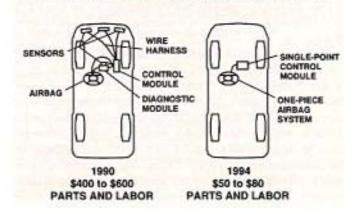

## AIR BAGS AND ACCELEROMETERS

Automotive air bags have dramatically reduced fatalities and severe injuries of vehicle occupants involved in head-on collisions. As a result, many car makers have engaged to outfit all cars with them within the next 3 years; and legislation in the USA and elsewhere will mandate some form of passive restraint in all cars and trucks by 1995. This has resulted in a huge demand for a low-cost, highly reliable air-bag system.

Within an airbag system, the electronic control module makes the decision when to fire the airbag. Currently, most airbag systems in production use several electromechanical crash sensors, acting as on-off electrical switches, mounted at the front of the car. Their output is sent to the control module, which combines their outputs with that of an electromechanical "safing" sensor and decides whether to fire the airbag. The safing sensor is used to reduce the chances for a false deployment, which would be likely if only the output of the crash sensors were considered; the crash sensors have a fairly low trip point and can be fooled by potholes, etc. To trigger the airbag, at least one crash sensor and the safing sensor must close. These distributed systems are expensive to install, and reliability is compromised by the number of interconnections and the inability to self-test the sensors.

The new approach in airbags is to use a "single-point sensing system," where a single accelerometer (such as the ADXL50) is mounted in the passenger compartment, doing away with the crash sensors mounted at the front of the car and the associated wiring harnesses. Also, the output of the accelerometer is continuous, rather than on-off, with voltage proportional to the acceleration. This enables the system to use a more-sophisticated decision-making algorithm in its microcontroller to distinguish between a crash condition and other events—rather than relying on a majority vote of several switches. "Smart" algorithms use signal-processing approaches similar to those used in speech recognition and predictive methods to perform the decision.

An 8-mph (12.8 km/h) head-on crash into a solid wall should not deploy; a  $\approx$ 12-mph (19.2-km/h) crash should deploy. In some situations, the decision to fire the airbag has to occur in <15 ms from the start of the crash. The system's goal is to fire the airbag by the time the occupant has moved 5 in (0.13 m).

Single-point sensing provides significant cost reductions and increased system reliability through elimination of the many components and connections associated with multi-point systems. Furthermore, the continuous and linear output of the ADXL50 enables the use of more sophisticated deployment algorithms by the airbag system controller, resulting in a more accurate system with fewer unnecessary airbag deployments.

# "Uncommon-Mode" High-Speed Video Feedback Amplifier with a Difference

AD830 has separate differential input and feedback circuits, combines wide bandwidth and high common-mode rejection

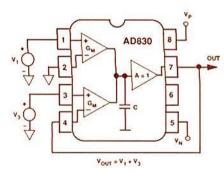

The AD830° is a wideband amplifier designed to reject high-frequency common-mode voltage and noise in differential line-receiver applications. It employs a powerful alternative topology, active feedback, with inherent advantages in handling differential signals and differing system grounds, level shifting, and low-distortion high-frequency amplification. With its ±50·mA minimum full-output-current drive capability, additional uses include buffering of ADCs and applications as a high-speed instrumentation amplifier and a high-speed level shifter.

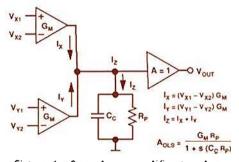

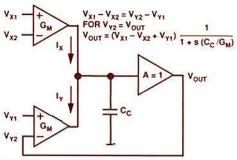

As the simplified model of Figure 1 shows, an internal capacitor integrates the sum of the currents from a matched pair of differential-input transconductance  $(G_m)$  stages. In typical applications, the differential input signal is applied to one of the  $G_m$  stages, and negative feedback from the output to the other input closes the loop, which seeks to maintain the net current in the capacitor essentially at zero in the steady state. This current-balancing capability is akin to that of op amps, but since the currents are derived from differential voltages via the  $G_m$  stages, there is dynamic isolation between input and output circuits.

Figure 1. Open-loop amplifier topology.

Figure 2 shows the device's simple connection as a unity-gain difference amplifier/line receiver. The input is connected between X1 and X2 in either polarity, and the output is fed back to Y2. Y1 may be grounded directly—or connected to a source of offsetting voltage for level shifting. The circuit responds only to the differential input and feedback voltages, so it has excellent common-mode rejection, 100 dB, dc to 100 kHz, and 60 dB (55 min) at 4 MHz. Other characteristics include 50-MHz large-signal bandwidth (1 V rms); 100-MHz small-signal bandwidth (100-mV rms), with 0.1-dB flatness to 15 MHz; 530-V/ps slew rate and 35-ns scitling time to 0.1% (4-V step); 0.05%/ 0.08° differential gain/ phase errors (0 to +0.7 V, 4.5 MHz); and -72-dB total harmonic distortion at 4 MHz. DC performance includes =3-mV max input offset voltage ( $\pm$ 5-mV max,  $T_{MIN}$  to  $T_{MAX}$ , J and A versions); ±13-μA max bias current and 1-μA max offset current over temperature.

Figure 2. AD830 as a unity-gain difference amplifier (line receiver). For higher gains, attenuate the feedback, for level shifting, add an offsetting voltage at Y1.

The AD830's advantages over subtractor connections of op amps in differential applications include high common-mode rejection ratio, high-impedance inputs, symmetrical circuit behavior for gain of either +1 or -1, low sensitivity to the value of source resistance, equal impedances at the + and - inputs, inherently excellent high-frequency CMR, and freedom from having to use highly matched resistor sets.

For gains greater than unity, the feedback signal may be attenuated, in the same way that noninverting gain is achieved in operational amplifier circuits—but the differential signal input permits either polarity of gain. It is also worth noting that—unlike op amp circuits—performance of AD830 circuits is the same for positive and negative gains.

From the point of view of operational flexibility in systems, the availability of 2 pairs of signal terminals makes possible some analog signal-processing operations that would be cumbersome with operational amplifiers. For example, Figure 3 shows a circuit for summing two voltages at high impedance without using summing resistors.

Figure 3. High-input-impedance summing amplifier without resistors.

The AD830 is characterized for performance with ±15-volt and ±5-volt supplies, but its offsetting capability means that it can also perform well with single supplies from +10 to +30 V. Performance/temperature grades include J and A for commercial and industrial temperature ranges, and S for -55 to +125°C. Packages include 8-pin plastic mini-DIP, Cerdip, and SOIC. A 16-page data sheet includes a variety of application suggestions and 28 families of performance curves. Prices start at \$2.42 (1000s).

The AD830 was designed by Analog Devices Fellow Barrie Gitbert at ADI's Northwest Labs, Beavenon, OR.

<sup>\*</sup>Use the reply card for technical data. Circle 2

## CMOS 10-Bit, 15-MHz A/D Converter for Imaging Applications

AD875 uses a single +5-volt supply and dissipates only 185 mW (<50 mW in standby)

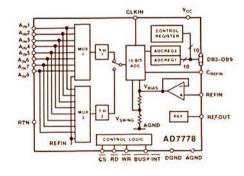

The AD875\* is a 10-bit, 15-MHz A/D converter designed to digitize high-speed stepped signals, such as the outputs of charge-coupled devices, infrared imagers, and multichannel data-acquisition systems. Implemented in CMOS, it has low power requirements—185 mW typical, 235 mW max, and even less (<50 mW) in the power-down standby mode—an important feature in portable battery-operated systems, such as camcorders and electronic still cameras.

The converter guarantees no missing codes over the full temperature range (0 to +70°C), is packaged in a tiny 48-pin flatpack, and can operate from a single +5-volt supply. Its digital I/O can interface with either +5-V or +3.3-V logic. The speed and precision of the AD875 are ideally suited for digitizing sampled video signals directly from charge-coupled devices (CCDs) in color scanners, digital copiers, and electronic still cameras.

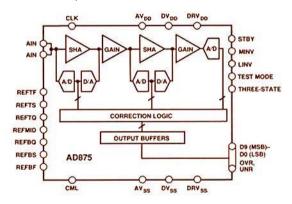

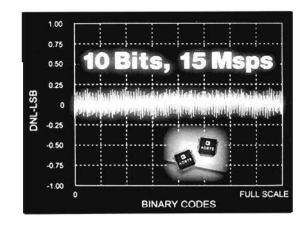

Using a multi-stage pipelined architecture (Pigure 1) with output error correction, the AD875 achieves differential nonlinearity of ±0.4-LSB (1.0 max) over the entire range of input and temperature, and small-signal differential nonlinearity (DNL) of 0.8 LSB max—an important advantage in imaging systems.

Figure 1. AD875 block diagram.

Besides power-down, additional functions to reduce system cost include 3-state outputs, underrange and overrange flags, and a flexible choice of output formats, including positive- and negative-true binary and twos complement. To minimize errors due to

series resistance. Force and Sense terminals are provided at the ends of the reference ladder so that it can be driven using Kelvin connections. The power-supply connections, with their associated grounds, are separated into three components—analog, digital, and digital I/O buffers, to permit a flexible choice of logic voltage and to optimize the AD875's performance.

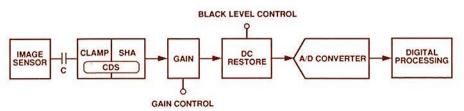

## **IMAGING SYSTEMS**

While the specifies of a particular system may vary, most imaging-system architectures will employ some or all of the building blocks shown in Figure 2. The image sensor, often a charge-coupled device (CCD), transforms light intensity to a sampled electrical output. The resulting stream of pixel values is conditioned by a clamp/sample-hold circuit, sometimes referred to as a correlated double sampler (CDS). A gain block sets signal levels to normalize the signal range to the A/D converter's optimum full-scale input range. DC restoration is used to remove any errors in the signal's de level due to ac coupling and de drift. Since the input to the converter is a rapidly stepped de voltage, a sample/hold is unnecessary (except for the internal SHAs used as part of the multistage pipelined conversion process). After conversion to digital, the signal is subjected to digital processing that depends on the application.

Depending on resolution and bandwidth requirements, color information may already exist in the sensor signal (camcorders), the RGB signals may be separately acquired and multiplexed ahead of the converter for color scanners, or three independent channels may be converted in parallel for high-resolution color video.

The AD875 is specified for the 0 to +70° commercial temperature range and is housed in a space-saving 48-pin thin quad flatpack (TQFP). An evaluation board is available. Price of the AD875 in 1000s is \$21.50.

The AD875 was designed by a team led by Mark Mottin and Chris Mangelsdorf at ADI's Wilmington facility.

\*Use the reply eard for technical data. Circle 3

Figure 2. Typical imaging system.

# Increase Laser Printer Resolution with Win-Win Chip—No Tradeoff Worries

Pulse-width modulator is superior to super-pixel technique for gray-scale and doesn't need a higher-resolution engine

by Bill Schweber

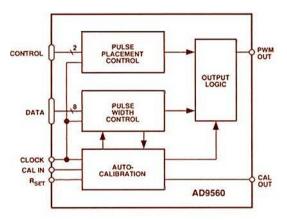

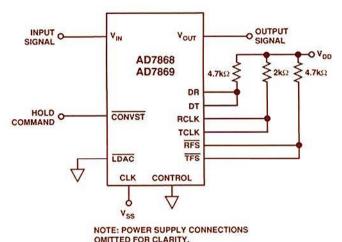

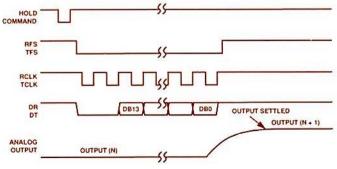

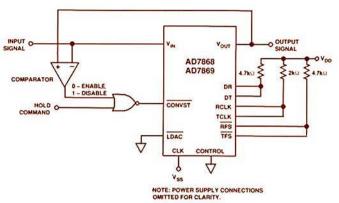

The AD9560\* pulse-width modulator (Figure 1), is a monolithic IC designed specifically to enable laser-printers to provide increased resolution and more realistic "gray-scale" images, even with a standard 300-dot-per-inch (dpi) "engine". It does this by setting the laser-diode's excitation pulse width and position, for each pixel, in proportion to a control word supplied by the printer controller. This permits control of both area and placement of toner for each final printed dot. The AD9560 can also be applied in color printers; in fact, it has already been designed into several prototype monochrome and color printer systems.

Figure 1. Block diagram of the AD9560.

The AD9560 uses a similar architecture to members of the AD9500 digitally programmable time-delay generator family (Analog Dialogue, Vol. 22-1). Like the AD9505, it is designed for pulse reprogramming on each cycle. Complete and self-contained, the AD9560 connects to the laser-diode driver circuitry in the printer, which would require a profusion of discrete circuitry—and at less power and expense for the same functionality. It

requires only a single external resistor to match its nominal fullscale range to that of the dot clock. An on-chip autocalibration circuit fine-tunes the range and compensates for lot-to-lot variations of the on-chip timing circuits.

With the AD9560, pulse width and pulse placement can be changed on every clock cycle at clock rates up to 50 MHz. Output pulsewidth is proportional to the value of a parallel 8-bit data input, while pulse placement (beginning, middle, or end of the clock period) is set by two control lines.

For mixed-mode printed images, which combine the variable tones of graphics with the black-or-white pixels of solid text, it is useful to disable the modulation and force full on/off operation during the text portions. This is easily achieved by entering a 00 or FF (hex) code, which sets the IC output to logic zero or logic one for the entire clock cycle.

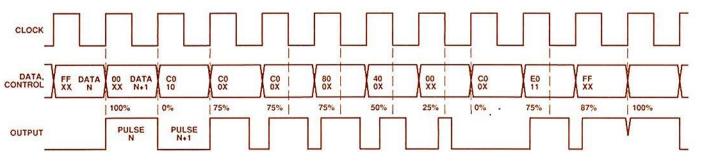

The relationship between the system dot clock, data, position control codes, and resulting output to the laser-diode driver is shown in Figure 2 for some data and control combinations. The figure is idealized in that it does not show internal propagation or buffer delays, which must of course be accommodated in the system design.

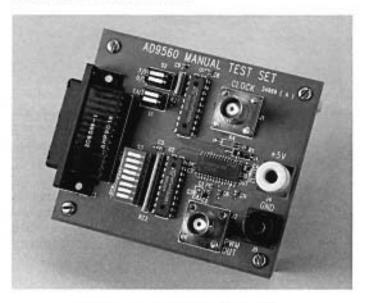

## **EVALUATION BOARD**

A complete and compact evaluation board  $(3.8 \times 3.2 \text{ inches}, 97 \times 84 \text{ mm})$  is available to examine the performance of the AD9560 (Figure 3). This board requires a +5-V supply, a pulse generator for the dot clock, and an oscilloscope for viewing the

Figure 2. Example of timing diagram.

output pulse. Output duty cycle and pulse position are usersettable manually via DIP switches on the evaluation board and dynamically via a 25-pin connector.

Figure 3. AD9560 evaluation board.

The AD9560 is available in 28-pin DIP and SOIC packages, for the 0° to +70°C temperature range. Price is \$15.30 (1000s) for the SOIC package.

The AD9560 was designed by Edward Jordan at Analog Devices'

Greensboro, NC facility.

## **GRAY-SCALE TECHNIQUES**

For video displays (CRTs), achieving gray scale images is relatively straightforward: just control the intensity of each displayed pixel. This is done by modulating the CRT electron beam intensity, through an all-analog circuit in conventional TV, or a DAC in a PC system. The brightness of the pixel is closely proportional to the intensity of the electron beam. This is equally true for monochrome and the red-green-blue beams of color displays.

For printed images, the situation is very different. Monochrome printing is done with inks—or toner, in the case of the laser printer—having a chosen intensity and hue, and there is no convenient way for the intensity signal to directly modulate the intensity of the medium itself. But the inherent averaging ability of the eye and brain for small parts within a larger whole offer a solution: vary the portion of the pixel area to which the medium is applied; the eye responds to the reduced proportion of black (or other single-color) area as though it were solidly printed with reduced intensity. [For a familiar example of this, look at the various shadings of a newspaper photo through a magnifying glass.]

The "sub-pixel" approach uses numerous small pixels to represent each data point and adjust the local number of black (on) dots relative to the unprinted white (off) area to provide the required intensity. The eye then integrates these into an equivalent gray-scale value. But this technique has a downside. The larger number of smaller dots required to give adequate gray-scale resolution without losing spatial resolution requires a faster clock for the pixel control circuitry to fit the increased number of dots into the time for one standard dot. It is somewhat costly because it requires, along with higher-speed digital components and special high-speed layout considerations, a high-quality printing process to achieve the spatial resolution.

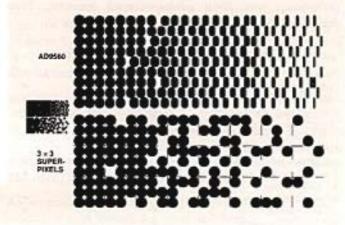

Gray-scale is often approximated on the present generation of printers, using full-size on-off pixels, with a "super-pixel" technique: as shown below, it computes the average intensity over a group of individual pixels (between 8 and 16) and then varies the number of "on" pixels to produce that intensity, averaged over the group. It is essentially similar to the approach described above, but with greatly reduced spatial resolution and provides only low gray-scale resolution (8 to 16 levels), equivalent to a newspaper photo.

In contrast, the pulse width and -position modulation of the AD9560 directly controls intensity by varying the size and incremental position of the ink deposited in each pixel in analog fashion without involving digital tricks, such as adding pixels or involving computations with adjacent pixels. Instead, it allows the duty cycle for each pixel to be varied between 0 and 100%, thus varying the energy absorbed by the photoconductive drum of the laser printer. In turn, more or less toner is attracted to each dot according to its energy level, and gray scale toning is achieved on a dot-by-dot basis. The resulting image quality is comparable to a "slick" magazine image.

In addition to pulsewidth, the AD9560 allows the pulse position within the clock period to be set to the leading edge, center, or trailing edge of the clock, an additional degree of freedom that can be used by the printer software to enhance the perceived appearance of the resulting image, as the above idealized example demonstrates, for a gradation from 100% down to 20% gray scale. Thus, with 8-bit control of the dot area (254 levels between all-on and all-off) and 3 positionalternatives, a pixel may be printed in any of 764 different ways, as determined by the processing of the digital image-intensity signal and the resulting 10-bit intensity-control word.

<sup>\*</sup>Use the reply card for technical data. Circle 4

## Video RAM-DACs Offer Unprecedented Resolution, True-Color Screen Images

ADV715x Series features triple 10-bit resolution, with speeds up to 220 MHz

by Bill Slattery

Combining three 10-bit video digital-to-analog converters and the associated color-palette RAM in a single package, the ADV7150 series\* of RAM-DACs is industry's first monolithic solution that provides true color and gamma correction. These software-compatible ICs—capable of displaying 16.8 million colors at one time, from a palette of over 1 billion colors, offer 24-bit true-color performance with 30-bit gamma-corrected operation. Three devices provide a choice of specialized features (Table 1).

Table 1. Features of the AD715x family

| Feature                        | ADV7150 | ADV7151 | ADV7152 |

|--------------------------------|---------|---------|---------|

| 24-bit "gamma" true color      | •       |         | •       |

| 24-bit "standard" true color   | •       |         | •       |

| 8-bit "gamma" pseudo color     | •       |         | •       |

| 24-bit "standard" pseudo color |         |         |         |

| 15-bit true color              | •       |         | •       |

| 220 MHz-true color             | •       |         | •       |

| 220 MHz-pscudo color           | •       | •       | •       |

| Triple 10-bit DACs             | •       |         | •       |

| 4:) multiplexing               | •       | •       |         |

| 2:1 multiplexing               | •       |         | •       |

| 1:1 multiplexing               | •       | •       | •       |

| 160-lead QFP package           | •       |         |         |

| 100-lead QFP package           |         | •       | •       |

The ADV7150/ADV7152 are the industry's first monolithic RAM-DACs capable of delivering 24-bit True-Color performance at rates up to and including 220 MHz. The AD715x series holds another industry first with its triple 10-bit RAMs and triple 10-bit DACs [For additional discussion of video DACs and color images, see Analog Dialogue, Vol. 24-3, pp. 3-6 and p. 7.]

Such high-resolution displays are used to show both fine detail (icons, menus, images) and subtle color shading, to captures the true image accurately. Generally, the standard triple 8-bit video display is not sufficient for applications such as full color pre-press (preparation for color printing). Although the average user will not be aware of differences between 8-bit and 10-bit color, the professional artist or color printer will appreciate the benefits.

Speed and Resolution: Increased screen resolution is the prime factor driving the increasing speed requirements of video RAM-DACs, since a high update rate is needed to avoid flicker (the de facto standard is 60 Hz, but this figure is destined to increase to between 70- and 80 Hz to minimize eyestrain caused by "peripheral flicker"). Table 2 shows the resolution values required for different graphics systems and the pixel clock rates needed to achieve them.

But the speed of the RAM-DAC determines only the X-Y (spatial) resolution of the graphics system, i.e., the number of pixels/frame

and frames per second. The DAC resolution, in bits, adds color depth to the displayed image. More DAC bits allow the system to provide more shades of each primary color, resulting in many more combined shades of color and much truer color definition.

The ADV7150 and ADV7152 are 24-bit true-color devices, with three 8-bit control inputs, one for each of the red, green, and blue channels. This provides 256<sup>3</sup> (nearly 17 million) addressable colors. The pseudo-color ADV7151 can display an image with the same number of pixels (resolution) but with a choice of only 256 colors per frame.

Applications requiring the same pixel resolution may have differing color-resolution needs. For example, the needs of engineering wire-frame modeling, IC circuit design, and black-and-white desktop publishing can be satisfied with 256 colors. However, volume visualization, 3-D solids modelling, and full color pre-press must have available the more than 16 million colors that the ADV7150 and ADV7152 offer. For example true display of the various shades of green and red give an apple's image depth and realistic image quality.

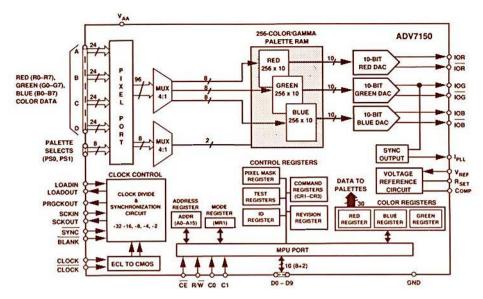

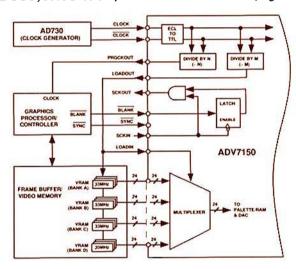

These workstation RAM-DACs differ in their architecture from industry-standard devices for PCs (the ADV47x series) by their on-board multiplexers (Figure 1). Internal multiplexers eliminate the need for multiplexing at the system level. Since the display needs a video rate of, for example, 160 MHz, but today's fastest video RAMs operate at speeds of up to 40 to 50 MHz, the graphics circuitry must include multiplexing to accommodate the difference between what a single video RAM can provide and the actual RAM-DAC (and screen) requirements.

Four 40-MHz video RAMs can be directly connected to the input of an ADV7150 or ADV7151 and multiplexed at 160 MHz to yield the required video bandwidth. The on-chip multiplexer does have a downside, the high pin count for these devices—since 24-bit true color requires 24 input pins. Thus, four multiplexed inputs require 96 pins, in addition to connections for control, power, and other functions. The ADV7150's pixel input ports can also be multiplexed at rates of 2:1, and 1:1.

The ADV715x series is also unique in that it has on-board clock control circuitry and does not require additional (and expensive) control ICs. The need for a separate pixel/load clock synchronizer

Table 2. RAM-DAC resolution, clock speed, and applications.

|                            | 40-02-03            | 없이 경에 교하다 하게 그 마시 있어요? 그 있어 없다 그리지 그리고 그리고 있다면 하다. |

|----------------------------|---------------------|----------------------------------------------------|

|                            | Pixel Clock         |                                                    |

| Screen Resolution (pixels) | Rate                | Application                                        |

| 1024 × 768 (76 Hz update)  | 80 MHz              | Super VGA                                          |

| 1152 × 870 (76 Hz update)  | 100 MHz             | Macintosh 21" screen                               |

| 1152 × 900 (76 Hz update)  | 106 MHz             | Sun SPARCStation                                   |

| 1280 × 1024 (76 Hz update) | 135 MHz             | DEC, HP, IBM workstation                           |

| 1600 × 1280 (60 Hz update) | 170 MH <sub>2</sub> | High-end workstation                               |

| 1600 × 1280 (76 Hz update) |                     | Imaging workstation                                |

|                            |                     |                                                    |

Figure 1. Block Diagram of the AD7150.

is eliminated by a divided-down, synchronized "loadout" clock. All necessary signals, including data-transfer signals, such as LOADOUT, PRGCKOUT, & SCKOUT are available (Figure 2).

Figure 2. Frame-buffer interface.

### GAMMA CORRECTION

While an increased number of DAC bits is important to more closely approximate the eye's ability to tesolve differences in the displayed image, it is not a complete solution. Unfortunately, the response of the CRT's color phosphors to the electron beam that impacts them is not linear. This non-linear response, which is seen by the eye as deviation from the intended color value, is called the gamma function, where  $\gamma$  is an exponent in the approximate relationship between the electrical intensity input and intensity of the light produced by the phosphor:

$$I_{CRT} = (I_{IN})^{\gamma}$$

2.0 <  $\gamma$  < 2.8

If the value of  $\gamma$  is known for each primary color (red, green, blue) the gamma error can be compensated for by using a  $1/\gamma$  factor to correct  $I_{1N}$ . (Note that conventional television has analog gamma correction circuit built into the camera to correct for this problem.

Also, it's worth noting that in TV the intensity modulation is produced by an analog signal with the "infinite" resolution of continuous response, rather than with a digital input and a DAC that responds with "bits of resolution"!

In digital systems with limited resolution, there is a conflict between the linear relationship of binary values and the requirements for more bits to implement gamma correction accurately at low values of intensity. The ADV715x series is inherently more suitable with its 10- instead of 8-bit resolution. The ADV715x chips contain lookup tables for y correction.

An interesting and prominent application of this 10-bit DAC technology is in systems for initial and periodic correction and calibration of CRT color monitors using feedback techniques. With a measuring device placed on the monitor screen, the system inputs known "signals" to the display under test, measures the resulting color image, and sends this information back to the system. A color matching calibration algorithm (gamma correction) then calculates correction factors, and the contents of the color palette in the system's RAM-DAC are modified accordingly. This approach benefits by the use of 10-bit display DACs because the measuring system should have higher resolution than that being measured.

The ADV715x series of RAM-DACs are fabricated in CMOS and require a single +5-V supply. Current consumption is <350 mA for the fastest ADV7150 (and less for slower grades). For all three devices, analog video outputs are RS-343A and RS-170 compatible. The ADV7150 is packaged in a 160-lead plastic quad flatpack (PQFP); the ADV7151 and ADV7152 are in 100-lead PQFPs. The ADV7150/51/52 are available in 85, 110, 135, 170 and 220-MHz speed grades. They range in price (1000 pieces) from \$71/\$51/\$69 for the 85-MHz grades to \$167/\$121/\$163 for the fastest (220-MHz) grades.

The ADV715X series was designed by a team led by Tim Commins of Analog Devices' Limerick, Ireland facility.

<sup>\*</sup>For technical data on these parts, use the reply card. Circle 5

## Fast, Accurate, Monolithic Sampling A/D Converter

## 10-Bit, 40-MSPS AD9040A has 54-dB SNR at 10 MHz. Evaluation board permits quick performance testing

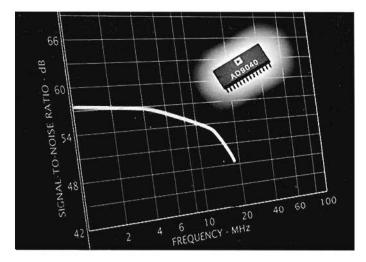

The AD9040A\* is a complete monolithic 10-bit sampling A/D converter with on-chip track-and-hold, voltage reference, and timing circuitry. Designed for low cost, high-performance, and relatively low-power dissipation (940 mW typical, 1.1 W max), it requires only an encode signal to achieve sampling rates as high as 40 MSPS. When sampling a 10.3-MHz analog input at 40 MSPS, its signal-to-noise ratio (including distortion) is typically 55 dB (8.8 ENOB), 51 minimum.

Typical applications include beamforming in ultrasound medical imaging (requiring low power, wide dynamic range, and low cost), professional video image processing (e.g., special effects and tape recorders), digital communications (wireless LANs and cellular base stations require wide dynamic range and bandwidth to pick out small signals of interest in the presence of potentially large interfering signals), digital oscilloscopes, and advanced television (MUSE) decoders.

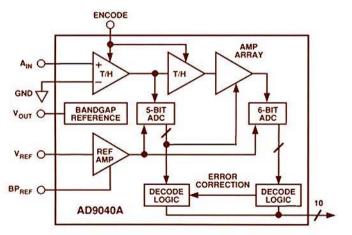

The AD9040A employs a two-step subranging architecture with digital error correction (Figure 1). The analog input is applied to a high-input-impedance track-hold, which holds the analog value when an Encode strobe is applied. The 2.5-volt precision on-chip bandgap reference can be used to avoid external references, allowing denser packing of ADCs for multichannel applications. The device requires power of +5 V at 89 mA (105 mA max over temperature) and -5 V at 87 mA (100 mA max).

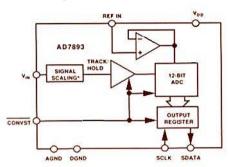

Figure 1. Block diagram of the AD9040A.

The high input impedance and full-scale input range of 2 V p-p eliminate the need for external buffers in many applications. The digital inputs and outputs are CMOS compatible, allowing direct interfacing with ASICs. An out-of-range output goes high when the analog input goes I LSB beyond the maximum or minimum end of the ADC's input range.

The AD9040A is designed to be sampled at rates from 2 to 40 MSPS, with a minimum specified range of 10 to 40 at 25°C. Typical sampling aperture delay is 1.9 ns, with jitter of 7 ps, rms. The output propagation delay is 14 ns max over temperature.

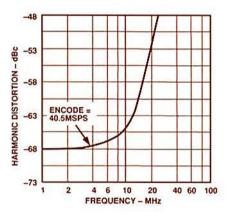

Dynamic specifications include maximum second- and third-harmonic distortion (Figure 2) of -56 and -58 dBc respectively, at 10.3 MHz, and typical two-tone (2.3 and 2.4 MHz) intermodulation distortion rejection of 62 dBc. In video applications, its maximum differential gain and phase errors are 1.0% and 0.5°.

Figure 2. Harmonic distortion as a function of frequency at 40.5 MSPS sampling rate

The analog input, with 5 pF input capacitance and 200-k $\Omega$  minimum resistance, accepts signals with bandwidth up to 48 MHz. Maximum offset voltage over temperature is  $\pm 30$  mV, and maximum bias current is 25  $\mu$ A.

Accuracy specs include no-missing-codes guaranteed over temperature, maximum differential and integral nonlinearity of 2.5 LSB over temperature, and maximum gain error of 2% of full scale over temperature.

An evaluation board is available—including a reconstruction DAC and latches. The AD9040A is available in 0 to +70°C (28-pin plastic-DIP and SOIC) and -25 to +85°C (ceramic-DIP and gull-wing surface-mount) versions. Prices start at \$50 in 100s; the evaluation board is priced at \$250.

The AD9040A was designed by a team led by Frank Mirden and Carl Moreland, of our Greensboro NC facility.

<sup>\*</sup>For technical data, use the reply card. Circle 6

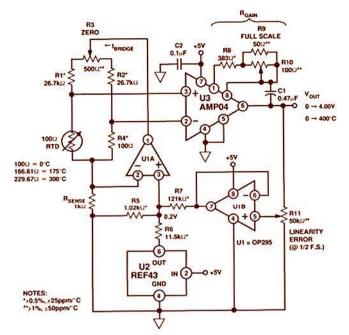

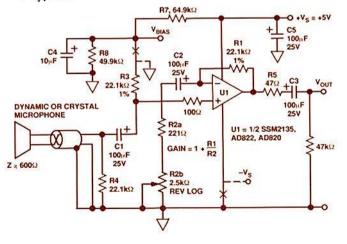

# High-Performance ICs in Single-Supply Analog Circuits— Design Issues and Application Examples

by Walt Jung and James Wong

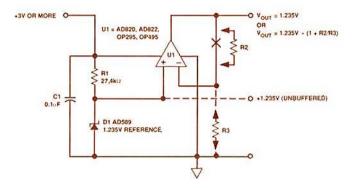

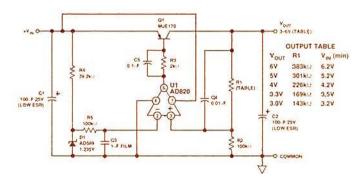

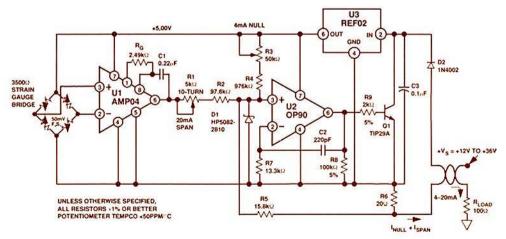

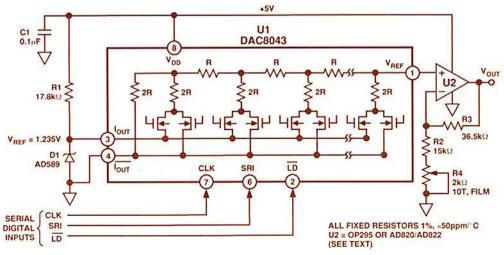

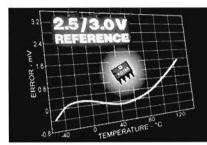

As system designers increasingly use single-supply power for both analog and digital circuits, they face challenges if they must obtain the kind of performance they are used to at higher voltages—and increased challenges if they seek to better it. This article examines some typical precision analog functions with op amps and other devices, using chips and application techniques designed to produce maximum benefit on single low-voltage (3-5-volt) supplies at low power. We first consider device limitations, then discuss examples of application circuits.

## **DESIGN ISSUES**

## Selecting Amplifiers

The choice of amplifier (or other analog chip) is a critical step toward a successful single-supply design. A source of helpful information, Table 1 lists typical specs of currently available Analog Devices on amps suitable for use on single supplies  $\geq 3 \text{ V}$ , in order of increasing power consumption per channel. Although most of these devices work over much wider voltage ranges, as well as on dual supplies, our emphasis is on their low-voltage single-supply behavior. Characteristics listed include single-supply voltage range and input- and output (grounded-load) commonmode ranges, for supply voltages ≤5 V. As the table indicates, many of the amplifiers are available as singles, duals, and even guads; and most come in both DIP and SOIC packages. Also listed are (5-V) quiescent currents per amplifier channel, output drive current, and basic do & ac specifications. The following detailed discussions will provide further insight into specific amplifier design features.

## Reduced Signal Range

Most op amps in use today are designed for traditional ±15-V supplies, which allows ample input common-mode (CM) voltage range, as well as a wide output range—typically ±10 V for both. Because power conservation is a major reason for using them, single-supply systems often have closely restricted supply voltage, for example, +12 V down to +5 V, as low as +3 V, and even in some cases +1.5 V. At these low voltages most standard dual-supply op amps cease to function at all, while some may still operate with degraded specifications. Until recently, low-voltage amplifier choices have been limited.

General purpose 741s & 1558s, and most FET-input amplifiers operate on supplies as low as ±5 V (10 V total). Precision amplifier families such as OP-07 or OP-27 types don't work below ±5 V. Types from some selected families may be used over regions of this voltage spectrum; for example the AD705 & OP-97 families are useful down to ±2.25 V (4.5 V), and the AD817 wideband op amp is spec'd for +5-V use. But in general, only amplifiers that are specifically designed for single-supply use will function without major limits in CM range and output swing below +10 V. Examples are the LM324/LM358 families as general-purpose modest-performance single-supply types, and the devices of Table 1 for precision uses.

## Watch Out for Input/Output Swing Limitations

Amplifiers designed for ±15-V operation typically need 2 to 5 V of headroom at input and output, with respect to both supply rails. Even more-flexible dual-supply designs, such as the AD705 & OP-97 families, approach only to within 1 V.

In low-voltage (3- to 5-V) single-supply applications, such headroom requirements become critical limitations to linear operation over even modest signal swings. For this reason, single-supply amplifier input stages are designed to remain fully linear, even when the input CM voltage is at the negative rail, or 0 V. Differential input-stage architectures allowing this involve PNP bipolars, CMOS (or PMOS) inputs, and N-channel JFET inputs. The various devices result in differing input bias currents, noise voltages/currents, and offset voltages/drifts. All the devices listed in Table 1 can operate with  $V_{IN}=0$  V; at the upper end of the CM range, some devices can go to within 1 V of the rail, while others may need 1.5 V.

Table 1. Op-Amp Chips Compatible with 3- and 5-Volt Single-Supply Systems

| Device/s             | Amplifier <sup>[1]</sup><br>Channels | Supply <sup>[2]</sup> Range (V) | V <sub>IN</sub><br>Range<br>0 to (V) | Vour<br>Range<br>(V) to (V) | Bandwidth<br>(kHz)           | Slew<br>Rate<br>(V/ms)   | Quiescent <sup>(3)</sup><br>Current<br>(µA) |                             | Offset<br>Voltage<br>(µV) | Bias<br>Current<br>(nA) |

|----------------------|--------------------------------------|---------------------------------|--------------------------------------|-----------------------------|------------------------------|--------------------------|---------------------------------------------|-----------------------------|---------------------------|-------------------------|

| OP-90/290/490        | 1/2/4                                | 1.6-36                          | $+V_s-1$                             | 0.6, 4.0(6)                 | 25                           | 10                       | 20                                          | <b>±</b> 5                  | 125                       | 4                       |

| OP-22                | 1                                    | 3.0-30                          | $+V_{s}-1.5$                         | 0.7, 4.1 <sup>(6)</sup>     | 200 @ 10 μA <sup>[4]</sup>   | 41Aلب 10 @80             | 10-10014)                                   | $\pm .02$ to $\pm 20^{[4]}$ | 400                       | 3(4)                    |

| OP-20/220/420        | 1/2/4                                | 5.0-30                          | $+V_{S}^{3}-1.5$                     | 0.7, 4.1 <sup>(6)</sup>     | 100                          | 50                       | 45                                          | <b>≃</b> 0.4                | 300                       | 16                      |

| OP-32 <sup>(3)</sup> | 1                                    | 3.0-30                          | $+V_{s} - 1.5$                       | 0.7, 4.1 <sup>(6)</sup>     | 1000 @ 100 µA <sup>[+]</sup> | 300@100µA <sup>(4)</sup> | 15-450(+1                                   | ± .02 to ±20[1]             | 400                       | 4.5[4)                  |

| OP-295/495           | 2/4                                  | 3.0-36                          | $+ v_s - 1$                          | $0, +V_s$                   | 75                           | 30                       | 150                                         | ±3.5                        | 300                       | 8                       |

| OP-80                | 1                                    | 5.0-16                          | $+V_{S} - 1.5$                       | 0, 3.7                      | 300                          | 400                      | <b>32</b> 5                                 | +40, -20                    | 400                       | 0.0006                  |

| AD820/822            | 1/2                                  | 3.0-36                          | $+V_s - 1$                           | 0, +V <sub>s</sub>          | 1900                         | 3000                     | 700                                         | ±15                         | 300                       | 0.002                   |

| OP-292/492           | 2/4                                  | 5.0-36                          | $+\mathbf{V_s} - 1$                  | $0. + V_s - 1.5$            | 4000                         | 300                      | 1000                                        | <b>±8</b>                   | 500                       | 350                     |

| OP-183/283           | 1/2                                  | 3.0-30                          | $+V_{s} - 1.1$                       | $0, +V_{s} - 1.1$           | 5000                         | 10000                    | 1200                                        | <b>±20</b>                  | 300                       | 400                     |

| OP-113/213/413       | 1/2/4                                | 4.0-36                          | $+V_{s} - 1$                         | $0, +V_{S} - 1$             | 3500                         | 1000                     | 1400                                        | <b>≈</b> 30                 | 100                       | 500                     |

| SSM-2135             | 2                                    | 4.0-36                          | $+V_{s} - 1$                         | $0, +V_{s} - 1$             | 3500                         | 1000                     | 1400                                        | ±30                         | 200                       | 300                     |

NOTES

Number of amplifiers on chip: 1-single amplifier, 2-dual, 4-quad.

<sup>&</sup>lt;sup>2</sup>Total supply voltage span, single or dual.

<sup>&</sup>lt;sup>3</sup>Per amplifier, using +5-volt supply.

Varies with Iser.

$<sup>^{5}</sup>A_{V(mia)} = 10$ .  $^{6}V_{OUT}$  range can be extended to include 0 volts, using pulldown resistor.

With the exception of parts specified with output swing of 0-to-+V<sub>s</sub> (or "rail-to-rail"), most op amps swing to within only 1-to-2 V of the positive rail. So, on supplies of 5 V or less, output swing is greatly reduced in relation to the supply. Even if the input noise floor were to remain constant (which it seldom does), signal-to-noise (SNR) and dynamic range suffer. The sidebar, "Single-Supply Amplifier Output Stages," covers some key factors in single-supply output stage design, and helps differentiate the devices of Table 1 architecturally.

## Quiescent Current Drain

Aside from basic cost factors, another fundamental reason for single-supply designs is to conserve power, since they are quite often used in battery-operated equipment. So not only are they designed to perform at very low voltage, but they must also have low quiescent current per channel  $(I_Q)$ . Unfortunately, low-current designs require basic tradeoffs; in general, sacrifices involve bandwidth, slew rate, and input noise voltage.

Standby current drain (no signal) per amplifier can often be used to qualify a device for critical system power conditions. In the absence of a standard industry definition, we call devices with  $I_Q$  of  $\leq 1$  mA/channel low power, and those with  $I_Q$  of  $\leq 100$   $\mu$ A/ channel micropower. Many of the devices shown in Table 1 meet one or more of these criteria.

## Noise Tradeoffs

Bandwidth versus noise is a highly likely tradeoff, as demonstrated by the following examples: the OP-295/OP-495 has input voltage noise of 51 nV/√Hz at 150 μA/channel, the AD820/AD822 has 12.5 nV/√Hz at 700 μA/channel, and the OP-113/213/413 family has noise of 4.7 nV/√Hz at 1.45 mA/channel. Lower noise can be attained at the price of increased current.

### Reduced Bandwidth

In a low-power design environment, engineers are forced to face not just generally slower speed in the op amps, but also higher circuit impedances, which themselves can set bandwidth restrictions.

Again, tradeoffs exist. For example the bipolar-input OP-295 has an attractively low current drain of 150 μA/channel, but the bandwidth is 75 kHz with SR of 0.03 V/μs. Where more speed is needed, a FET-input AD820 could be considered, with a 1.9-MHz bandwidth and 3-V/μs SR, at the cost of increased current, 700 μA/channel. Both of these dual devices have rail-to-rail output stages. The OP-183/283 achieve 5 MHz and 10 V/μs, but with current of 1.2 mA/channel.

### "Where Is Ground?"

This issue can become quite important in single-supply op amp ac-coupled circuits, since a circuit designer can arbitrarily choose any value for this "false" or pseudo-ground return level. The best choice depends on the application, but a flexible choice of amplifier circuits—and devices that can be used in them, helps make signal referencing easier, particularly in cases where substantial dynamic (i.e., ac) current is present.

Possible choices here range from a simple ac-bypassed resistive divider to fully buffered op amp follower stages that provide the lowest wideband dynamic impedance. A well bypassed noise-free divider is suitable for high-impedance loads, where the dynamic current is low. When dynamic currents are higher, the divider can be buffered with a follower-connected op amp.

## AMPLIFIER OUTPUT STAGES

While output swing can be very important in single-supply applications, not all single-supply amplifier outputs are designed to swing all the way to the negative rail (ground). Some may swing to within a diode drop (~ 0.6 V), others to within a few tens of mV. Only a few swing to within 1 mV of the negative rail—and a precious few swing nearly to both supply rails.

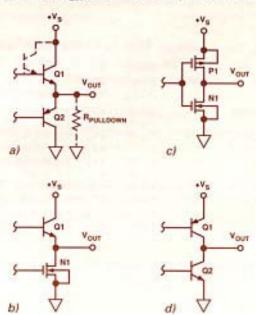

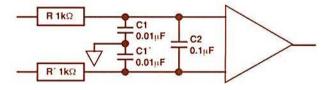

To understand which device types work best in applications for which output swing is critical, a designer needs to know about the design of the output stage. These vary widely in detail, so knowledge of their architecture can be critical to an informed selection. The figure illustrates a sampling of some output-stage topologies used in ADI single-supply amplifiers.

The complementary emitter-follower stage of (a), employing bipolar transistors (an NPN transistor for Q1 and a PNP for Q2), can swing to within a diode drop of each rail, at best. It cannot pull right to ground without outside help, such as by adding R<sub>PULLDOWN</sub>, as noted within Table 1 (Note 6). This optional external resistor (which can also include the op-amp's gain-set resistors) bypasses the lower PNP, with its saturation limitation. This technique allows output linearity to ground only when sourcing current; and it can also raise overall dissipation, which may be excessive for sustained high-level outputs. Amplifiers with this type of output have their uses, but should be carefully applied to minimize tradeoffs in single-supply applications. This stage is used in the OP-90/290/490 families, among others.

The output stage of (b) uses a bipolar emitter follower and NMOS common-source. Though inherently asymmetric in terms of voltage swing, it uses the NMOS pulldown to achieve very low saturation voltage to ground. However, saturation voltage to the positive rail is ≥1 V. This stage is used in the OP-113/213/413 families, as well as in the AMP-04 single-supply instrumentation amplifier.

The CMOS stage of (c) is fully complementary and offers a resistive connection to the supply rails for both high and low output, viz., a swing of 0 to  $+V_S$ , or "rail to rail." With appropriate low- $R_{ON}$  devices for PI/N1, the saturation drop to

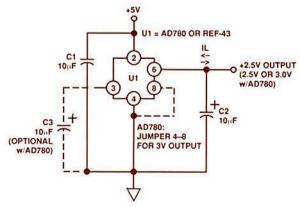

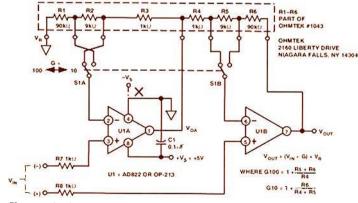

either rail can be ≤1 mV at low currents. Because this stage is inherently Class AB, the amplifier design must carefully control the static currents in PI-N1 to maintain low quiescent current. For output currents of a few milliamperes, this type of output stage is effective and quite versatile due to its wide swing. This stage is used in the OP-295/495 families and others.