相控功率发射项目

项目参与人员:

- 北京航空航天大学研究生 张天夫

- 南京航空航天大学研究生 刘旻

- 浙江大学研究生 施云峰

项目需求

功能要求

- 对频率相同,相位不同的两路信号INPUT1=sin(w1t+φ1)、INPUT2=sin(w1t+φ2)进行鉴相,得出其相位差φ1-φ2;

- 以同样相位差形成两路频率相同,相位与输入信号共轭的输出信号OUTPUT1=sin(w2t-φ1)、OUTPUT2=sin(w2t-φ2)。

性能要求

- 小信号中频:10.7MHz

- ADC:8-10bits/30Msps

- DAC:10bits/50Msps

- FPGA:Cyclone 10 SoC板

项目方案

方案综述

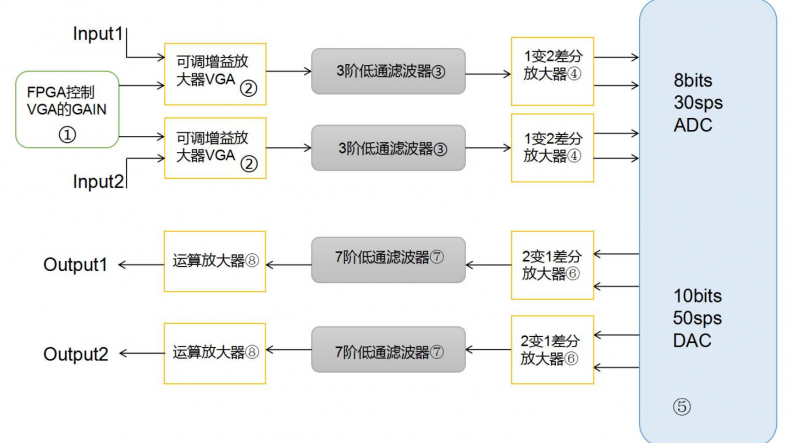

输入:

- 两通道输入小信号(频率为10.7MHz);

- 经可调增益放大器电压增加至 300mv 左右;

- 经过3阶低通滤波器滤除高频噪音;

- 信号经过低通滤波器后幅值有一定衰减,所以需要经过单端转双端差分放大器送至 ADC;

- 信号经 FPGA 内部数字鉴相器确定其相位差。

输出:

- FPGA 控制 DAC 输出共轭相位模拟信号,经双端转单端差分放大器变为两通道输出信号;

- 经7阶低通滤波器滤波;

- 将信号经过运算放大器输出功率信号。

算法说明

- 数字鉴相器

利用相关函数法进行鉴相的原理是,在初始时刻,两路频率相同的正弦信号之间的互相关值和它们相位差的余弦值具有线性关系。由于噪声信号与有效信号之间的相关性几乎为0,所以噪声信号对该方法测相的影响能被很好的抑制,具体原理框图如下:

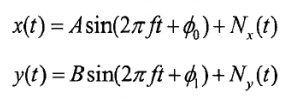

设输入两信号的数学模型分别如下:

设输入两信号的数学模型分别如下:

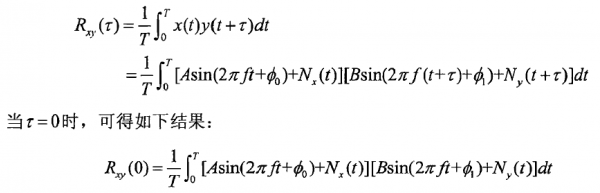

根据数学表达式很明显看出x(t)与y(t)是相关的,根据相关函数的定义,有以下互相关函数表达式:

根据数学表达式很明显看出x(t)与y(t)是相关的,根据相关函数的定义,有以下互相关函数表达式:

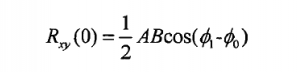

因为噪声信号和有用信号之间相关性几乎为0,而且噪声之间相关性为0,因此两信号的相关函数为:

因为噪声信号和有用信号之间相关性几乎为0,而且噪声之间相关性为0,因此两信号的相关函数为:

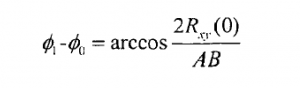

进行反余弦计算得出相位差值:

进行反余弦计算得出相位差值:

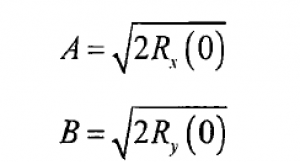

上式中两个信号的幅值系数可以表示为如下表达式:

上式中两个信号的幅值系数可以表示为如下表达式:

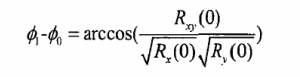

所以最终的相位差为:

所以最终的相位差为:

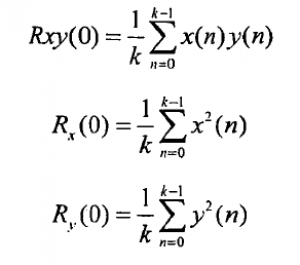

实际求取两信号相位差的计算中,参与计算的是连续信号按一定采样率进行采样后的离散信号序列,所以上述公式可以全部改写为如下离散计算公式:

实际求取两信号相位差的计算中,参与计算的是连续信号按一定采样率进行采样后的离散信号序列,所以上述公式可以全部改写为如下离散计算公式:

关键器件选择

电阻

- 25 0603封装 6个

- 50 0603封装 9个

- 4K 0805封装 3个

- 150 0603封装 5个

电容

- 22pF 0603封装 6个

- 0.1uF 0603封装 11个

- 0.33uF 0603封装 5个

- 220pF 0603封装 9个

- 180pF 0603封装 5个

- 100pF 0603封装 3个

- 10uF 0805封装 4个

- 2.2uF 0603封装 2个

- 47pF 0603封装 3个

- 0.01uF 0603封装 3个

- 270pF 0603封装 3个

电感

- 1uH 0603封装 3个

- 390nH 0603封装 3个

- 330nH 0603封装 3个

- 680nH 0603封装 3个

芯片

- U12 ADA4807-2ARMZ 2个 ada4807双转单放大器

- U11 AD8338ACPZ-R7 2个 ad8338_可调增益放大器

- U5 ADM660ARZ 1个 adm660_8660电荷泵变换器

- U10 MAX5866ETM+ 1个 max5866模拟前端芯片

- U3 OPA1678IDGKR 1个 opa1678运算放大器

- U9 LT6600IS8-20#PB 2个 lt6600差分放大器

- U1 LTC2644IMS-L10#PBF 1个ltc2644多通道电压输出DAC变换器

实施流程安排

* 第一周

第1~3天:根据设计框图讨论所需模块,包括:可控增益放大器模块(VGA)、3/7阶低通滤波器(LPF)、差分放大器模块(AMP)、双通道ADC/DAC模块、电源模块;

确定输入输出信号的频率、电压要求,查阅芯片手册选择合适的芯片。

第4~5天:绘制PCB原理图,通过阅读各芯片的数据手册进行外围电路搭建;

使用Multisim仿真软件进行电路仿真,确定滤波器电感、电容值以及确定各放大器所需电阻值。

* 第二周

第1~3天:完善PCB原理图,改变各芯片管脚顺序以便电路连接,增加原理图可读性;

进行项目review检查错误并完善。

第4~5天:进行PCB布局布线;

查阅文献,研究讨论FPGA鉴相器算法。

* 第三周

第1~2天:对PCB进行检查完善并完成投板;

分模块进行代码编写,包括:PWM控制VGA(GAIN值)、ADC/DAC单双路信号转换、鉴相器。

第3~5天:对电源模块进行硬件检测,完成±3.3V电压输出;

继续完成代码编写。

* 第四周

第1~2天:完成电路板硬件焊接;

根据实际情况合理调整代码。

PCB设计模块

项目报告

项目简要总结

- 电源模块:无负载时±3.3V电源电压可稳定输出,但有负载时,需要-3.3V供电的芯片共有4个,由于+5V转-5V芯片ADM660输出电流只有60mA,所以-3.3V电源带负载能力不足,最终只能输出-2.9V电源电压。

输入:

- 可控增益放大器VGA模块:AD8338芯片可通过调节GAIN控制电压控制其放大倍数,对于0.1 V至1.1 V之间的控制电压,额定增益范围从0dB至80dB。所以在之前利用LTC2644芯片输出两路PWM占空比可调信号给控制电压,LTC2644工作频率为25kHz,经三阶滤波后能够输出平滑正弦波。

- 单端转双端AMP模块:将输入的一路信号转为幅值分别为1.65±0.512V的;两路信号传送给ADC/DAC芯片。

输出:

- DDS输出两路频率相同,相位差为45°的正弦波,用示波器观察ADC/DAC输出信号毛刺较多但能看清信号为正弦信号,经过双端转单端放大器与滤波器后,信号毛刺依旧很大。在示波器中使用数字滤波器后,观察到波形很光滑。

- 鉴相算法仿真成果,具有较高的准确率,仿真图在word中。

项目出现的问题及改进方案

Q1:原本数字鉴相器的算法计划利用傅里叶变换法测相原理,在频域内鉴相,但通过阅读文献发现该方法需要对很多离散信号采样点进行傅里叶变换才能实现目标,而我们对于10.7Mhz信号的采样点只能达到6个,用此方法得到的结果误差较大,所以不能适用于我们的项目。 A1:选择相关函数法测相,该方法利用两路频率相同的正弦信号之间的互相关值和它们相位差的余弦值具有线性关系,符合项目的需求且能很好的抑制噪声。 Q2:调试电源模块时,+3.3V可以正常输出,-3.3V输出达到-4.6V。 A2:我们检查了电路图发现电源模块中ADM660芯片的LV管脚应为无连接,OSC管脚应接地,因为检查的疏漏导致这两个管脚连接错误,更改电路图及焊接调试过后输出依旧为-4.6V,于是在输出-3.3V的管脚之后并联了一个10uF的电容接地提高负电压带负载能力,电压输出变为-3.3V。 Q3:无负载调试电源模块时可以正确输出±3.3V电压,加上负载后+3.3v可以正常输出,而-3.3V只能达到-2.9V,在调试电路中发现ADC路单端转双端的差分放大器输出波形异常,而输入波形时正常正弦波。 A3:因为单端转双端差分放大器LT660需要用到±3.3V电压,所以直接考虑是否是负电压供电不足(只有-2.9V)导致该芯片无法正常工作。拆除电源模块后,直接用电源产生器为电路板提供±3.3V电压后,该差分放大器即可输出正常波形。 Q4:将输入端接上DDS输出的两路频率为10.7MHz、相位不同的两路信号之后,我们计划将相位差值通过8个LED灯显示以得知鉴相成功与否,但LED灯无亮灭。 A4:鉴相器算法中要求只要一通电,即刻采256个采样点值以供后续自相关、互相关以及反三角函数运算,此时采样值并不是真正的输入信号的值,考虑再加一个控制按键,当输入稳定时再进行采样。

未解决问题:

Q5:7阶滤波器无法工作。