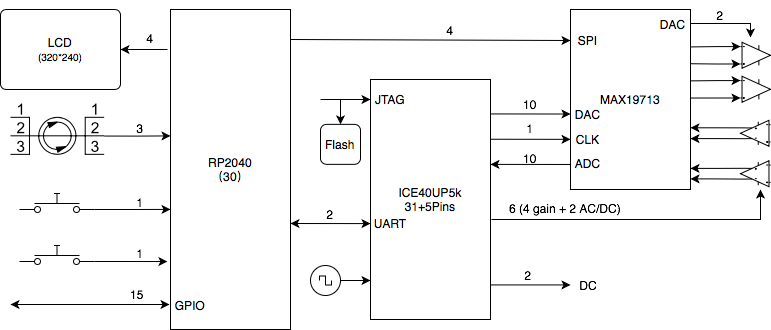

基于RP2040 + ICE40UP5k和MAX19713的数据收发系统

1. 系统构成

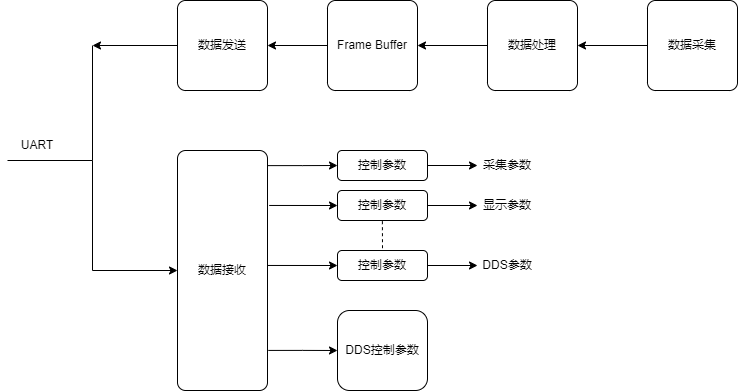

2. FPGA内部逻辑

3. 应用场景

- 高速DAC - 信号发生器

- 高速ADC - 数据采集、数字示波器

- 软件无线电 - 数据TX、RX,编解码

4. 测试步骤

- UART通信实现ADC和DAC的功能

- 通过上位机能够读取FPGA内处理好的数据,并将波形显示在上位机的图形化界面中,图形化界面可以在时间轴上缩放、前后移动,在幅度轴上能够调整刻度,能够自动适应

- 通过上位机可以将任意波形(函数计算 - 正弦波、方波、三角波、锯齿波、高斯脉冲、白噪声等,参考M2K内置波形)发送到FPGA中,通过DDS生成模拟波形

- 用RP2040/LVGL界面实现上述功能 - 采集数据进行双通道波形显示

- 通过MIPI接口连接MIPI的显示LCD显示屏,将波形显示在LCD上

- 通过RP2040配置ICE40的Flash