PCB布局布线

一旦完成了原理图的设计,通过ERC检查无误(没有Error、最好也没有Warning)、生成Netlist,就可以进入到下一步 - PCB Layout了,这个过程应该细分为元器件的Placement(布局)和信号线的Route(布线)两个环节,在实际的设计中Placement(布局)更重要,需要花费更多的时间,基于一系列的需求和规则对每个元器件在电路板上的位置进行认真的摆放,尤其是在大型的项目中,一定要待元器件的布局被相关的人确定以后,再开始信号线的连接,也就是布线的过程。布局和布线的过程基于信号完整性、电源完整性等方面的考虑不在本教程的探讨范围,在这里我们只看看KiCad这个工具如何实现布局和布线整个流程的。

我们将PCB Layout的过程也总结为按照顺序执行的10步:

- 按照项目的需求确定PCB板的物理大小、关键器件的位置、板子的层数并定义各层的功能

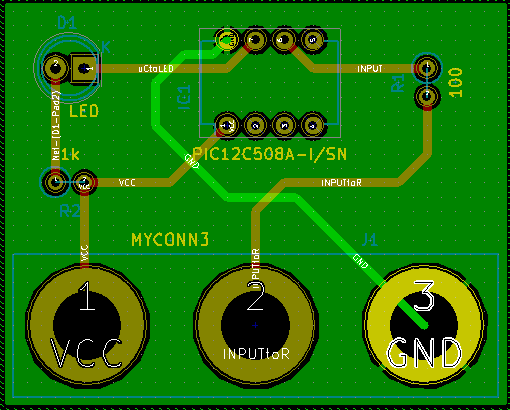

- 加载原理图生成的Netlist(网表),根据一系列的规则进行元器件的布局,可以通过3D视图查看板子的布局结构是否合理

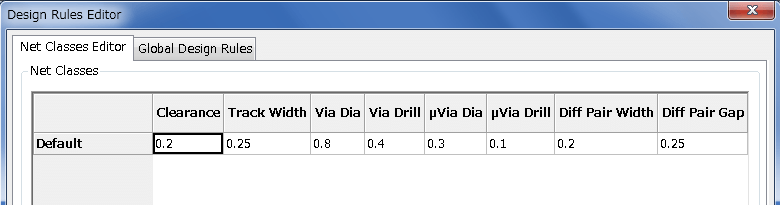

- 根据PCB加工厂商的制造规范设定PCB的布线规则 - 线宽、线间距、过孔大小、丝印字体及大小等等

- 关键信号线走线 - 电源 、时钟、差分信号、敏感的模拟信号….

- 其它信号线走线

- 铺地/电源

- DRC检查

- 对照原理图上的连线逐线高亮检查

- 调整丝印

- 生成给PCB加工厂需要的Gerber文件

接下来我们来看看KiCad中的Pcbnew是如何执行这些过程的。

1. Pcbnew的使用

1. 执行程序 - 从KiCad项目管理处,单击Pcb layout editor(PCB布局编辑器)图标 启动Pcbnew窗口。

启动Pcbnew窗口。

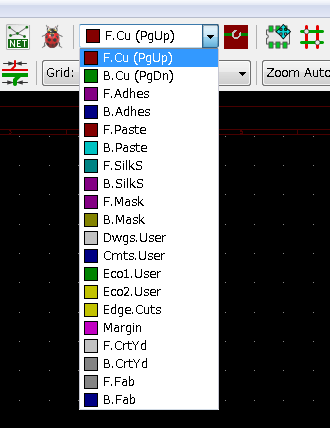

- 布线 - 一般来讲我们都会在电路板上通过大面积铺设地平面的方式将所有GND进行连接,因此在布线的时候可以先不用考虑GND这个网络上的连线。电路板的外表面有两层 - F.Cu(顶层,我们也称为Top Layer)和B.Cu(底层,我们也称为Bottom Layer),两层板一般选择在B.Cu层铺设大面积的地平面,因为F.Cu层主要用于放置元器件。如果设计中需要用到4层板,可以转到设置→图层设置将铜图层改为4. 你可以在图层表中设置需要的图层并对它们的用途做设定。

布线的时候我们先从F.Cu开始,在顶部工具栏的下拉菜单中选择F.Cu(PgUp),如图:

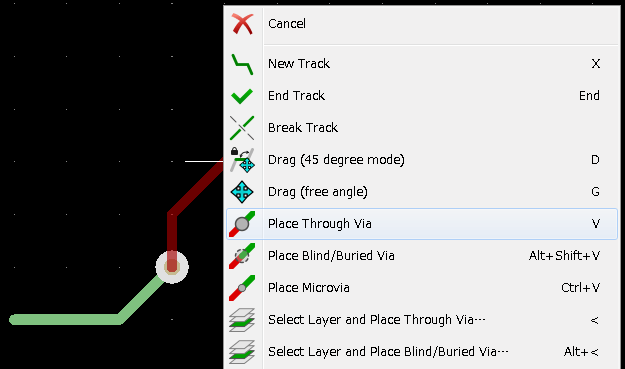

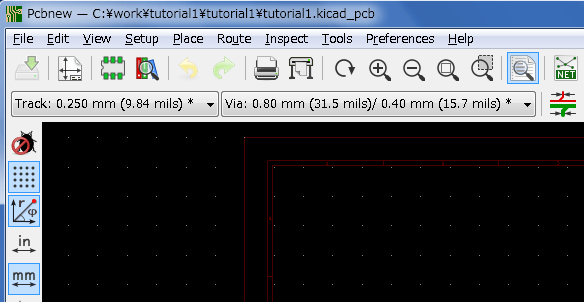

单击右侧工具栏上的Route tracks(布线)图标 。 单击J1的第1个引脚连线到R2的焊盘,双击鼠标结束连线。 此走线的宽度将默认为0.250mm,你也可以从顶部工具栏的下拉菜单中更改走线的宽度。 默认只有一个走线宽度。

。 单击J1的第1个引脚连线到R2的焊盘,双击鼠标结束连线。 此走线的宽度将默认为0.250mm,你也可以从顶部工具栏的下拉菜单中更改走线的宽度。 默认只有一个走线宽度。

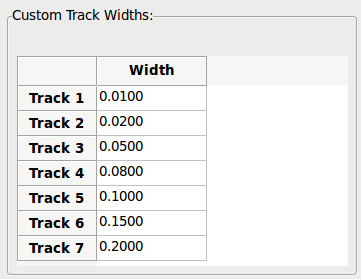

如果要添加更多走线宽度,可以通过设置→设计规则→全局设计规则选项卡,在此窗口的右下角添加任何其它你需要的宽度,这样在后面布线的时候你可以根据需要随时从下拉菜单中选择走线的宽度。 请参见下面的示例(单位为英寸)。

如果要添加更多走线宽度,可以通过设置→设计规则→全局设计规则选项卡,在此窗口的右下角添加任何其它你需要的宽度,这样在后面布线的时候你可以根据需要随时从下拉菜单中选择走线的宽度。 请参见下面的示例(单位为英寸)。

你也可以通过添加一个Net Class来设定一组选项。 转到设置→设计规则→网络类别编辑器,添加一个名为power的新类别。 将走线的宽度从8mil(表示为0.0080)改为24mil(表示为0.0240)。 接下来将除GND之外的所有网络都添加到Power类别(在左侧选择默认值,在右侧选择电源并使用箭头)。

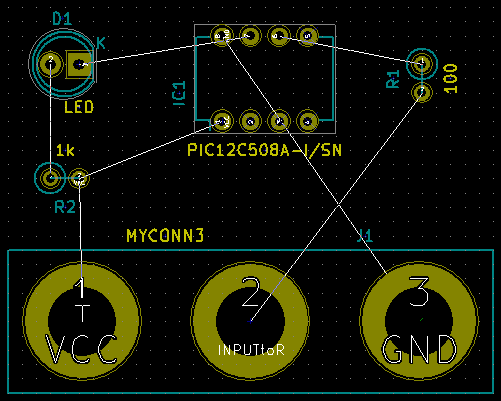

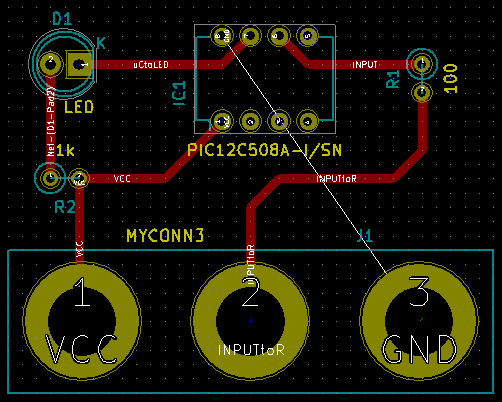

重复此过程,直到连接除J1的引脚3之外的所有连线。 电路板应如下所示。

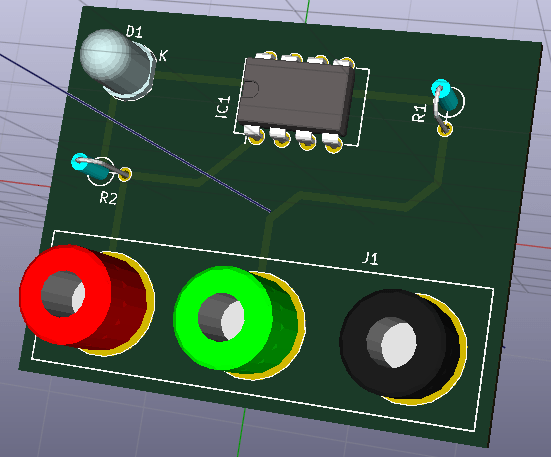

- 3D查看 - 3D查看是非常重要的一个功能,能够帮助你对自己设计的板子有个空间的概念,有些问题只有通过3D查看才能发现,比如装配方面的冲突等,具体的操作很简单 - 单击View →3D Viewer。

2. 生成和查看Gerber文件

一旦PCB设计完成,就可以为每一层生成Gerber文件,并将它们发给你要打板的PCB制板厂。

从KiCad中打开Pcbnew电路板编辑器,点击File(文件) → Plot(光绘). 光绘的格式选择Gerber,并选定你要输出的所有Gerber文件的文件夹,点击Plot(光绘)按钮。

要生成drill file(钻孔文件), 从Pcbnew里再执行一次File(文件) → Plot(光绘)选项. 按照首选的设置即可.

对于2层板,你需要选定如下的一些层的:

| 层 | KiCad层的名字 | 首选的Gerber扩展名 | 打开“用Protel文件扩展名” |

|---|---|---|---|

| Bottom Layer | B.Cu | .GBR | .GBL |

| Top Layer | F.Cu | .GBR | .GTL |

| Top Overlay | F.SilkS | .GBR | .GTO |

| Bottom Solder Resist | B.Mask | .GBR | .GBS |

| Top Solder Resist | F.Mask | .GBR | .GTS |

| Edges | Edge.Cuts | .GBR | .GM1 |

要查看所有Gerber文件,可以使用KiCad工程管理器中的GerbView功能。 在下拉菜单或图层管理器中,选择图层1. 单击File(文件)→ Open Gerber Files(打开Gerber文件)或单击图标 。 选择并打开所有生成的Gerber文件。 注意它们如何一个在另一个上面显示。

。 选择并打开所有生成的Gerber文件。 注意它们如何一个在另一个上面显示。

使用File→Open Excellon Drill File打开钻孔文件。

使用右侧的图层管理器选择/取消选择要显示的图层。 在发送到制板厂之前,要仔细检查每一层是否正确。

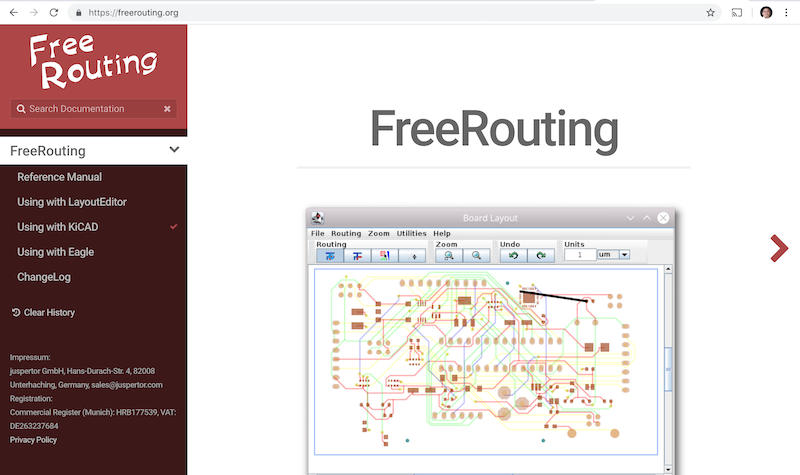

3. 使用FreeRouting自动布线

手工布线既快速又有趣,但对于具有大量器件的电路板,您可能希望使用自动布线器。请记住,您应首先手动对关键的信号布线,然后剩余的非关键但比较无聊的信号线可以让机器自动布线。它只会对还没有布线的信号进行自动连接。在这里可以使用的自动布线器是FreeRouting。

注:FreeRouting是一个开源的Java应用程序。目前FreeRouting有多种不同的版本,你可以在网上搜索“freerouting”,就会找到源代码或已经编译好的Java包,根据你自己的情况选择合适的格式使用。

- 从Pcbnew单击 File(文件)→ Export(导出)→ Specctra DSN, 保存文件到本地目录。启动FreeRouter并单击Open Your Own Design(打开你自己的设计)按钮,浏览dsn文件并加载它。

- FreeRouter具有KiCad目前不具备的一些功能,包括手动布线和自动布线。 FreeRouter主要有两个步骤:首先,对电路板进行布线,然后对其进行优化。完全优化可能需要很长时间,你可以随时停止它。

- 您可以通过单击顶部栏上的Autorouter(自动布线器)按钮来启动自动布线。底栏显示正在进行的布线过程。如果下面的“通过计数”已经超过30,意味使用自动布线很难步通你的板子,你可以调整板子上的器件位置,给出更多的布线空间再试一下。

- 左键单击鼠标可以停止自动布线并自动启动优化过程,再一次左键单击将停止优化过程。除非你真的需要停下来,最好让FreeRouter完成整个的自动布线过程。

- 单击File(文件)→导出 Specctra Session File菜单,并使用.ses扩展名保存电路板文件。FreeRouter规则文件没有必要保存。

- 回到Pcbnew。单击File(文件)→Import(导入)→ Specctra Session,选择.ses文件进行导入。

如果你对自动布线生成的任何连线不满意,可以删除掉再对其布线。

4. KiCad中的前向标注 - 对已经完成的设计进行修改

完成电路原理图设计、封装分配、电路板布局、布线并生成了Gerber文件,就可以将所需的文件发送给PCB制造商将设计变成实际的电路板了。

通常这种工作流程并非一直是单向的。有时在你已经完成所有设计流程以后,出于种种原因,你不得不再修改或扩展你的设计 - 比如调整器件的位置、替换某些器件、更改占用空间等等。这个修改过程你当然不想全部重新来过,例如你想在完成了原理图和PCB布局布线的工程设计中用CON2替换连接器CON1。比较合理的方法如下:

- 保存工程 - 返回原理图编辑器,单击File(文件) → Save Whole Schematic Project(保存整个原理图工程)保存项目,关闭原理图编辑器。

- 调整新器件的布局 - 此时,你应该看到先前布线好的器件以及左上角还未布线的器件,在我们的例子中也就是是CON2。用鼠标选择CON2,将该器件移动到电路板中间。

- 更新布线并保存 - 摆放好CON2并对其布线。完成布线后保存文件并生成新的Gerber文件。

这个“前向标注”的过程可以根据需要重复去做。还有另一种称为后向标注的方法允许工程师从Pcbnew修改已经布线好的PCB,进而在原理图和网表文件中更新这些修改。但Backward Annotation(后向标注)的方法不是太常用,在这里也就不再介绍了。