always语句总是循环执行,或者说此语句重复执行。

只有寄存器类型数据能够在这种语句中被赋值。寄存器类型数据在被赋新值前保持原有值不变。所有的初始化语句和always语句在0时刻并发执行。

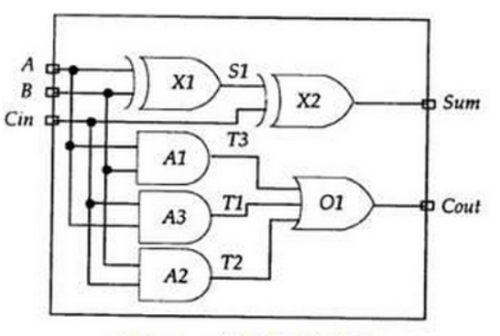

一位全加器电路

下例为always语句对1位全加器电路建模的示例

module FA_Seq(A,B,Cin,Sum,Cout); input A,B,Cin; output Sum,Cout; reg Sum,Cout; reg T1,T2,T3; always @(A or B or Cin) begin Sum = (A^B)^Cin; T1 = A & Cin; T2 = B & Cin; T3 = A & B; Cout=(T1 | T2) | T3; end endmodule

模块FA_Seq有三个输入和两个输出。由于Sum、Cout、T1、T2和T3在always语句中被赋值,它们被说明为reg类型(reg是寄存器数据类型的一种)。

always语句中有一个与事件控制(紧跟在字符@后面的表达式)。相关联的顺序过程(begin-end对)。这意味着只要A、B或Cin上发生事件,即A、B或Cin之一的值发生变化,顺序过程就执行。在顺序过程中的语句顺序执行,并且在顺序过程执行结束后被挂起。顺序过程执行完成后,always语句再次等待A、B或Cin上发生的事件。

在顺序过程中出现的语句是过程赋值模块化的实例。模块化过程赋值在下一条语句执行前完成执行。过程赋值可以有一个可选的时延。

时延可以细分为两种类型:

- 语句间时延:这是时延语句执行的时延。

- 语句内时延:这是右边表达式数值计算与左边表达式赋值间的时延。

下面是语句间时延的示例:

Sum=(A^B)^Cin; #4T1=A&Cin;

在第二条语句中的时延规定赋值延迟4个时间单位执行。就是说,在第一条语句执行后等待4个时间单位,然后执行第二条语句。下面是语句内时延的示例。

Sum=#3(A^B)^Cin;

这个赋值中的时延意味着首先计算右边表达式的值,等待3个时间单位,然后赋值给Sum。