基于旋转编码器的调节系统设计

实验任务

- 任务:基于 STEP-MAX10M08核心板 和 STEP BaseBoard V3.0底板 完成旋转调节系统设计并观察调试结果

- 要求:转动底板上的旋转编码器,调整核心板数码管数值在0~99之间变化,右旋增加,左旋减小。

- 解析:通过FPGA编程驱动旋转编码器获取操作信息,根据操作信息控制变量增加或减小,最后驱动独立式数码管将变量显示出来。

实验目的

在基础数字电路实验部分我们已经掌握了FPGA驱动独立显示数码管的原理及方法,本实验主要学习旋转编码器的驱动原理,最后完成旋转调节系统总体设计。

- 熟悉独立显示数码管驱动模块的应用

- 掌握旋转编码器的工作原理及驱动方法

- 完成旋转调节系统总体设计

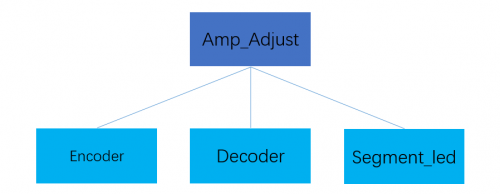

设计框图

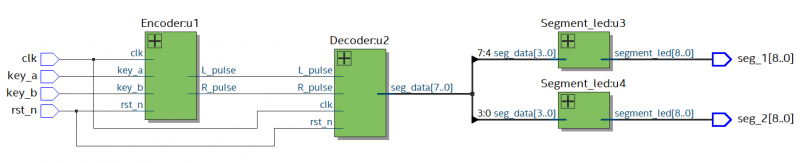

根据前面的实验解析我们可以得知,该设计可以拆分成三个功能模块实现,

- Encoder:通过驱动旋转编码器获取操作信息数据。

- Decoder:根据旋转编码器操作信息控制变量在0~99范围内加减变化。

- Segment_led:通过驱动核心板独立数码管将变量数据显示在数码管上。

顶层模块Amp_Adjust通过实例化三个子模块并将对应的信号连接,最终实现旋转调节系统的总体设计。

实验原理

旋转编码器介绍

旋转编码器(rotary encoder)也称为轴编码器,是将旋转位置或旋转量转换成模拟或数字信号的机电设备。旋转编码器用在许多需要精确旋转位置及速度的场合,如工业控制、机器人技术、专用镜头、电脑输入设备(如鼠标及轨迹球)等。 旋转编码器以码盘刻孔方式不同分为:绝对式和增量式两类。

- 绝对式编码器:具有多个不同二进制权重的代码环,每个不同角度产生一个独特的数字代码,表示编码器的绝对位置

- 增量式编码器:旋转过程中提供周期性输出,不能定位绝对位置,只能用于感知运动方向和增量

STEP BaseBoard V3.0底板上集成的旋转编码器就是机械增量式的。

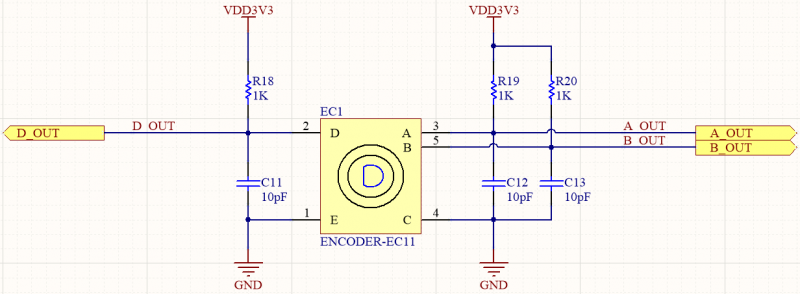

旋转编码器连接

STEP BaseBoard V3.0底板上旋转编码器的电路图如下:

我们使用的旋转编码器为EC11系列的,支持按动开关,共有5个管脚,

- 1、2管脚支持按动开关,就像我们之前用到的独立按键连接方式,

- 3、4、5管脚支持旋转编码,4脚为公共端,3、5管脚分别为旋转编码器的A、B相输出,如上图所示,我们给4脚接地,3、5管脚则需要接上拉电阻,同时为了降低输出脉冲信号的抖动干扰,我们有增加了电容到地做硬件去抖。

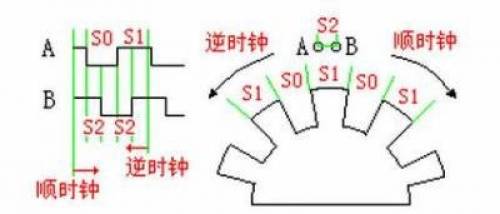

旋转编码器驱动设计

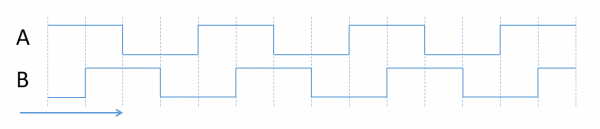

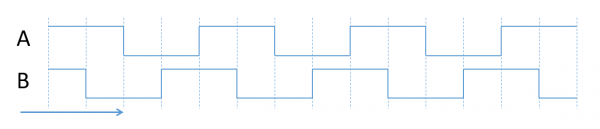

上图是机械增量式旋转编码器的原理示意图,中间圆形齿轮连接到旋转编码器的公共端4管脚,STEP BaseBoard V3.0底板上我们将之接地处理,A、B两个触点连接到旋转编码器的A、B相输出端3、5管脚,当进行旋转操作时,A、B触点会先后接触和错开圆形齿轮,从而导致A、B相输出信号产生相位不同的脉冲信号:

- 顺时针旋转时,A触点超前于B触点接触和错开圆形齿轮,A信号脉冲相位超前

- 逆时针旋转时,B触点超前于A触点接触和错开圆形齿轮,B信号脉冲相位超前

根据时序图可以看出旋转编码器顺时针或逆时针旋转时,A相信号超前或滞后B相信号,FPGA接收到旋转编码器的A、B信号时,可以根据A、B的状态组合判定编码器的旋转方向。 程序设计中我们可以对A、B信号检测,检测A信号的边沿及B信号的状态,

- 当A信号上升沿时B信号为低电平,或当A信号下降沿时B信号为高电平,证明当前编码器为顺时针转动

- 当A信号上升沿时B信号为高电平,或当A信号下降沿时B信号为低电平,证明当前编码器为逆时针转动

以上就是我们旋转编码器驱动设计的总体思路,下面我们就通过编程来实现它。

前面电路连接部分我们使用了两个电容对A、B信号作去抖处理,可以起到一定的效果,为了驱动更加稳定,我们在程序中再简单处理一下,先对系统时钟分频得到2KHz的时钟,然后在2KHz时钟的节拍下对A、B信号采样,三级锁存消除亚稳态

对A信号采样程序实现如下(对B信号一样):

reg key_a_r,key_a_r1,key_a_r2; //消除亚稳态 always@(posedge clk_500us) begin key_a_r <= key_a; key_a_r1 <= key_a_r; key_a_r2 <= key_a_r1; end

然后简单去抖处理程序实现如下(对B信号一样):

reg A_state; //简单去抖动处理 always@(key_a_r1 or key_a_r2) begin case({key_a_r1,key_a_r2}) 2'b11: A_state <= 1'b1; 2'b00: A_state <= 1'b0; default: A_state <= A_state; endcase end

检测A信号的边沿程序实现如下:

reg A_state_r,A_state_r1; //对A_state信号进行边沿检测 always@(posedge clk) begin A_state_r <= A_state; A_state_r1 <= A_state_r; end wire A_pos = (!A_state_r1) && A_state_r; wire A_neg = A_state_r1 && (!A_state_r);

最后根据A信号边沿与B信号的状态组合判定旋转的信息,

逆时针旋转脉冲输出程序实现如下:

//当A的上升沿伴随B的高电平或当A的下降沿伴随B的低电平 为向左旋转 always@(posedge clk or negedge rst_n) begin if(!rst_n) L_pulse <= 1'b0; else if((A_pos&&B_state)||(A_neg&&(!B_state))) L_pulse <= 1'b1; else L_pulse <= 1'b0; end //当A的上升沿伴随B的低电平或当A的下降沿伴随B的高电平 为向右旋转 always@(posedge clk or negedge rst_n) begin if(!rst_n) R_pulse <= 1'b0; else if((A_pos&&(!B_state))||(A_neg&&B_state)) R_pulse <= 1'b1; else R_pulse <= 1'b0; end

所以通过上面程序最终实现了左旋右旋的脉冲输出,脉冲的脉宽等于系统时钟的周期。

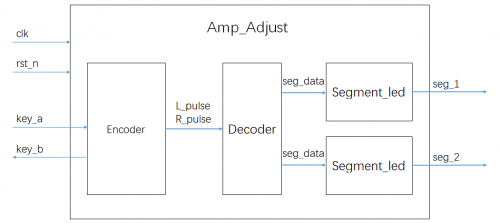

系统总体实现

回顾旋转调节系统设计框架,刚刚我们已经学习完成了旋转编码器的驱动设计,在基础数字电路实验部分我们已经掌握了FPGA驱动独立显示数码管的原理及方法, 模块通过一个4位的输入传递要显示的数值,通过9位的输出控制数码管显示该数值,这里我们不再重复,还需要设计一个模块,通过旋转编码器模块脉冲输出控制变量在0~99范围内加减变化。

关于BCD码在基础数字电路实验部分已经接触过,BCD码(Binarycoded Decimal),是用4位二进制码的组合代表十进制数的码制方法,这样显示更符合人的阅读习惯,所以BCD数值变化要求满9进1。

脉冲控制变量在0~99范围变化,左旋减,右旋加,程序实现如下

//key_pulse transfer to seg_data always@(posedge clk or negedge rst_n) begin if(!rst_n) begin seg_data <= 8'h50; end else begin if(L_pulse) begin if(seg_data[3:0]==4'd0) begin seg_data[3:0] <= 4'd9; if(seg_data[7:4]==4'd0) seg_data[7:4] <= 4'd9; else seg_data[7:4] <= seg_data[7:4] - 1'b1; end else seg_data[3:0] <= seg_data[3:0] - 1'b1; end else if(R_pulse) begin if(seg_data[3:0]==4'd9) begin seg_data[3:0] <= 4'd0; if(seg_data[7:4]==4'd9) seg_data[7:4] <= 4'd0; else seg_data[7:4] <= seg_data[7:4] + 1'b1; end else seg_data[3:0] <= seg_data[3:0] + 1'b1; end else begin seg_data <= seg_data; end end end

综合后的设计框图如下:

实验步骤

- 双击打开Quartus Prime工具软件;

- 新建工程:File → New Project Wizard(工程命名,工程目录选择,设备型号选择,EDA工具选择);

- 新建文件:File → New → Verilog HDL File,键入设计代码并保存;

- 设计综合:双击Tasks窗口页面下的Analysis & Synthesis对代码进行综合;

- 管脚约束:Assignments → Assignment Editor,根据项目需求分配管脚;

- 设计编译:双击Tasks窗口页面下的Compile Design对设计进行整体编译并生成配置文件;

- 程序烧录:点击Tools → Programmer打开配置工具,Program进行下载;

- 观察设计运行结果。

实验现象

将程序下载到实验平台,核心板数码管显示50,旋转编码器左旋(逆时针)数值减小,旋转编码器右旋(顺时针)数值增加,旋转编码器旋转时有顿挫感,每次顿挫数值变化1。