内容介绍

内容介绍

持续更新中,敬请关注。。。。

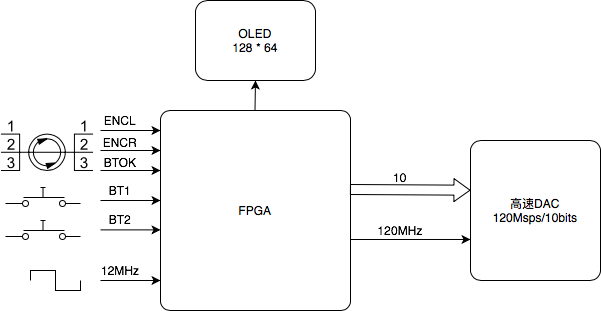

在电赛综合训练板上实现高速DDS信号发生器的功能:

- 1个旋转编码器和2个按键控制参数的输入

- 通过128 * 64的OLED显示参数信息以及菜单

- FPGA连接10bit/120Msps的高速DAC模块

系统构成:

功能框图

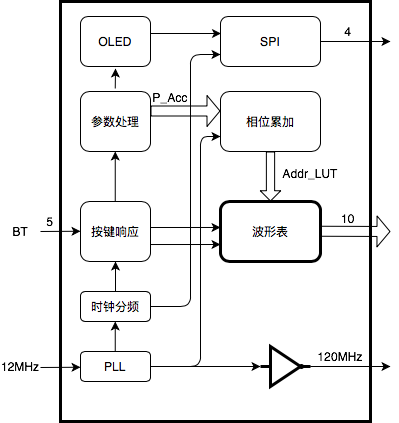

以基于Lattice XO2-4000HC小脚丫的FPGA为例

FPGA内部逻辑

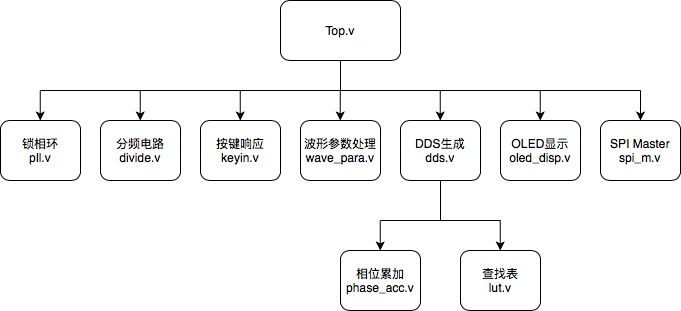

主要Verilog模块:

主要的Verilog模块

按键响应:

按键刚闭合的时候,会产生机械抖动,关于按键抖动的机制以及消抖的方法可以参见文章: Switch Bounce and How to Deal with It

在FPGA逻辑中处理按键消抖的基本原理:将键检测信号bt_pushed作为计数器的清零型号,当没有键按下的时候,bt_pushed为高电平,计数器一直处于清零状态,当按键按下的时候,bt_pushed变为低电平,计数器在时钟信号bt_check_clock作用下进行计数,代码如下:

module bt_debounce(bt_check_clk, bt_pushed, bt_out);

input bt_check_clk, bt_pushed;

output bt_out;

reg [4:0] q;

always @(posedge bt_check_clk)

begin

if(bt_pushed == 1)

begin q <= 5'b0000;

end

else if(q == 16)

begin q <= 5'b1000;

end

else

begin q <= q+ 1'b1;

end

end

assign bt_out = ~q[4];

endmodule分频模块

消抖电路需要频率约为1KHz的时钟信号,需要分频电路将锁相环输出的120MHz的时钟信号频率降到1KHz左右,可以通过17位的计数器来实现,217= 128*1024,经过17位计数器分频后得到的频率接近1KHz。Verilog代码如下:

module freq_bt_clk(main_clk, bt_check_clk)

input main_clk;

outout bt_check_clk;

reg [16:0]q;

wire bt_check_clk;

always @(posdge main_clk) q <= q + 1'b1;

assign bt_check_clk = q[16];

endmodule

十进制计数器

查表电路

DDS生成模块

DDS生成的机制详细介绍以及响应的代码可以参考DDS生成任意波形的方法及Verilog代码实例

OLED显示模块

参考文章:

软硬件

元器件

团队介绍

苏州硬禾信息科技有限公司

团队成员

硬禾发布

评论

0 / 100

查看更多

猜你喜欢

硬禾学堂STM32+FPGA核心板+电赛综合训练板完成的DDS正弦信号发生器本作品采用硬禾学堂的STM32G032 + ICE40UP5K FPGA核心板+电赛综合训练板套装,以单片机为控制核心,以SPI总线与FPGA通信,用Verilog HDL语言实现DDS产生0Hz~10MHz最小频率步进100Hz的正弦波。

新西国触手催更仙贝

5723

用基于小脚丫FPGA的电赛训练板制作DDS信号发生器本项目使用硬禾学堂2022寒假一起练电赛训练板完成制作DDS信号发生器,通过该项目可以理解DDS运行原理,学会应用DDS产生模拟信号;了解OLED的显示逻辑,学会调用OLED屏幕

森派陈醋

3039

基于小脚丫FPGA的电赛训练平台的DDS任意波形发生器使用小脚丫FPGA的电赛训练平台完成了2022寒假在家一起练活动的项目三—— DDS任意波形发生器/本地控制

。

NekoPrinter

2730