项目介绍

本项目使用STEP Baseboard4.0底板+STEP MXO2 LPC核心板,采用WebIDE图形化编程与Verilog硬件描述语言相结合的方式,使用图形化编程构建一套智能交通灯控制系统。使用Verilog语言实现环境感知与自动化控制功能,实现以下核心模块:

- 交通灯计时显示模块:通过图形化编程驱动数码管,实时显示红绿灯倒计时,图形化编程里内置的SN74HC192模块来实现数字的倒计时,使用自己编写的48译码器模块来完成BCD-七段码转换

- 蜂鸣器报警模块:当时间剩余不足4秒时,蜂鸣器会触发警报,以提示行人快速通过。

- 检测人员走进模块:采用Verilog实现接近传感器信号处理,当检测到行人靠近时,数码管显示人员走进程度,走的越近,则数码管显示数值越大

- 环境光感知模块:采用Verilog编写光强阈值比较器,比较阈值强度,若光强小于预设阈值则自动控制核心板的首尾LED点亮

硬件介绍

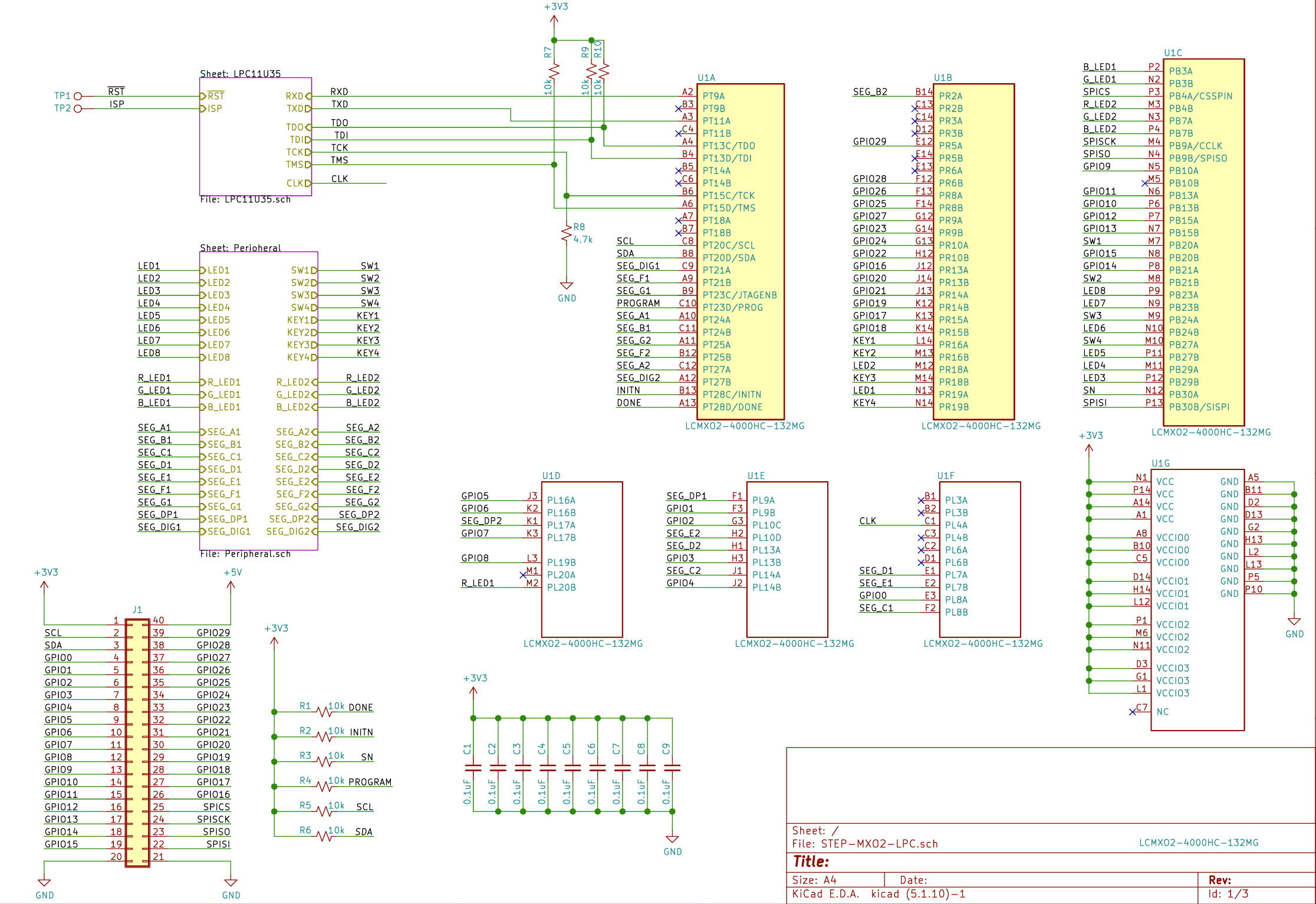

STEP MXO2 LPC 核心板

STEP MXO2 LPC 核心板基于Lattice LCMXO2-4000HC-4MG132 FPGA芯片设计,集成4320个LUT逻辑单元、96Kbit用户闪存及92Kbit RAM资源,内置2+2路PLL/DLL时钟管理模块,支持DDR/DDR2/LPDDR存储器扩展,具备瞬时启动能力(<1ms)。其嵌入式硬核包含1路SPI、1路定时器和2路I2C接口,可高效驱动外设。板载资源丰富,集成Type-C通信接口、2位七段数码管、2个RGB三色LED、4路拨码开关、4路按键及8路用户LED。

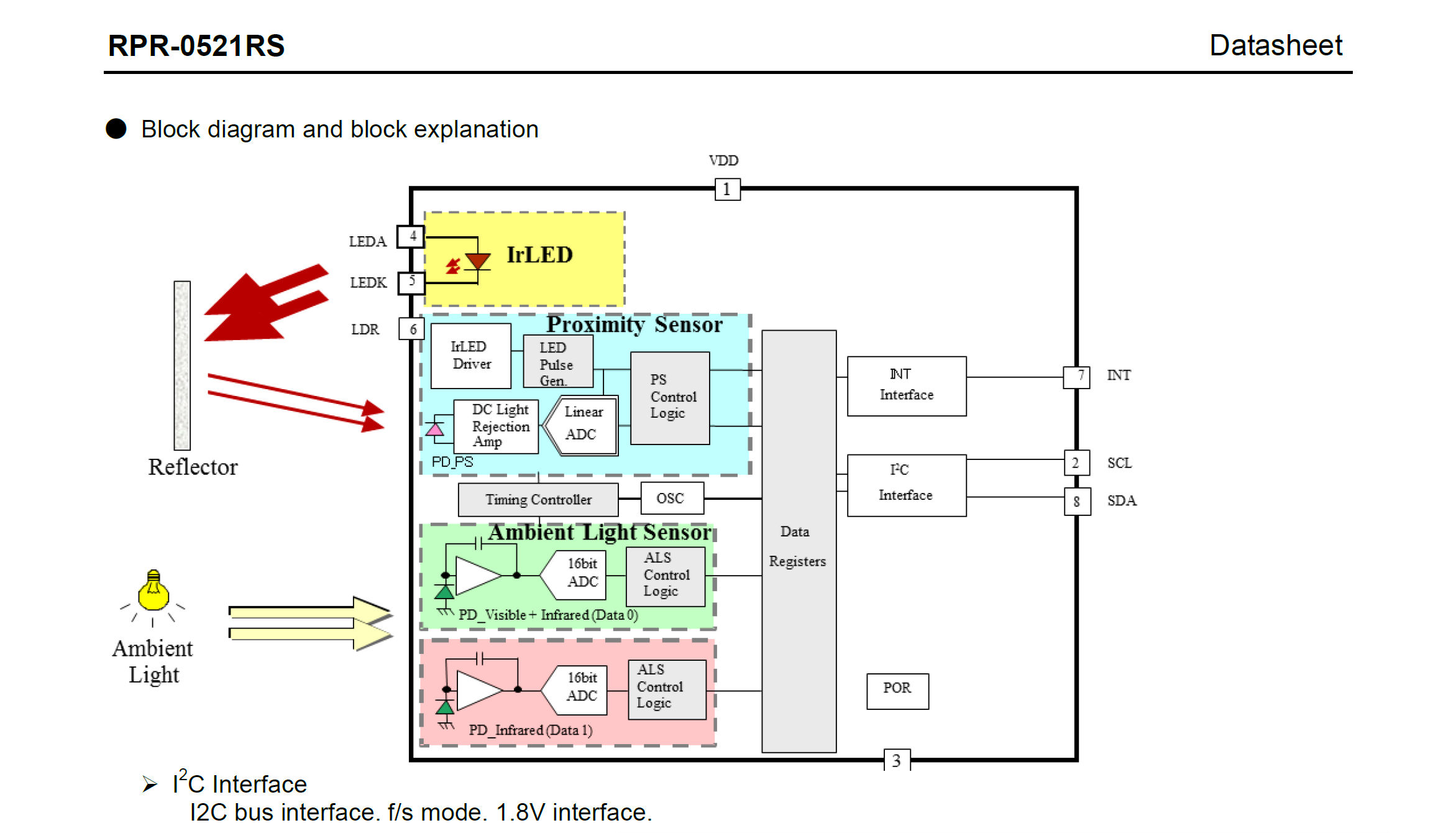

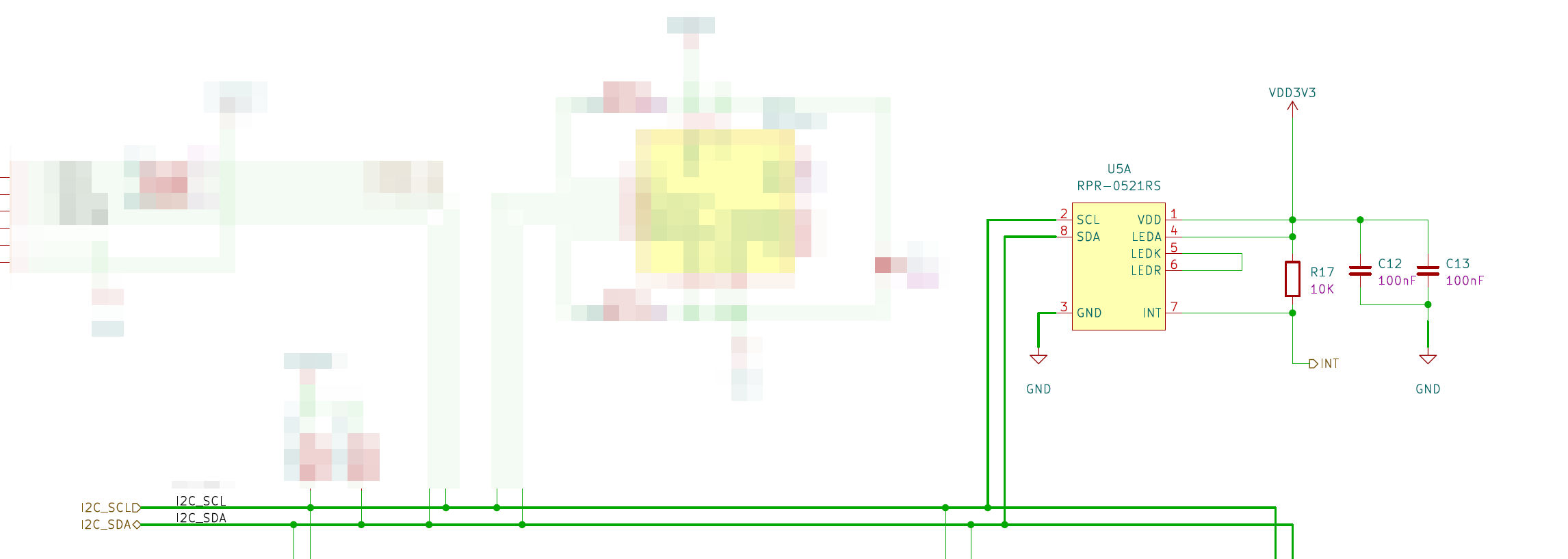

环境光感知与接近传感器

RPR0521RS传感器是ROHM公司研发的集成式光感与接近检测模块,具备环境光强度检测(0-43000lx)和红外接近传感(0-10cm)双功能。其通过I²C接口与主控设备通信,支持3.3V供电及低功耗模式,可精准感知人员接近并实时监测环境光变化,适用于智能照明、非接触交互等场景。本项目中用于检测行人靠近触发蜂鸣器报警,并根据环境光强度自动控制LED路灯亮度。

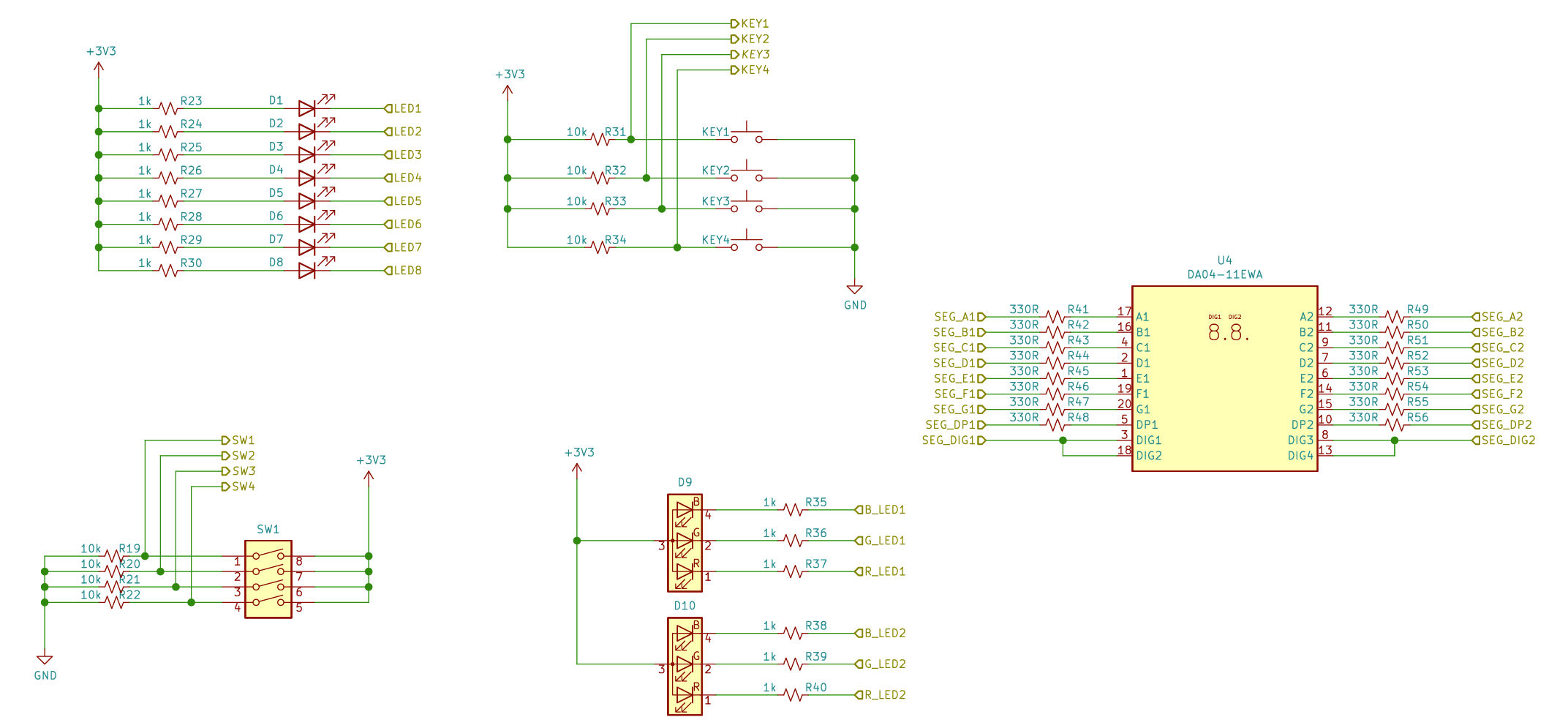

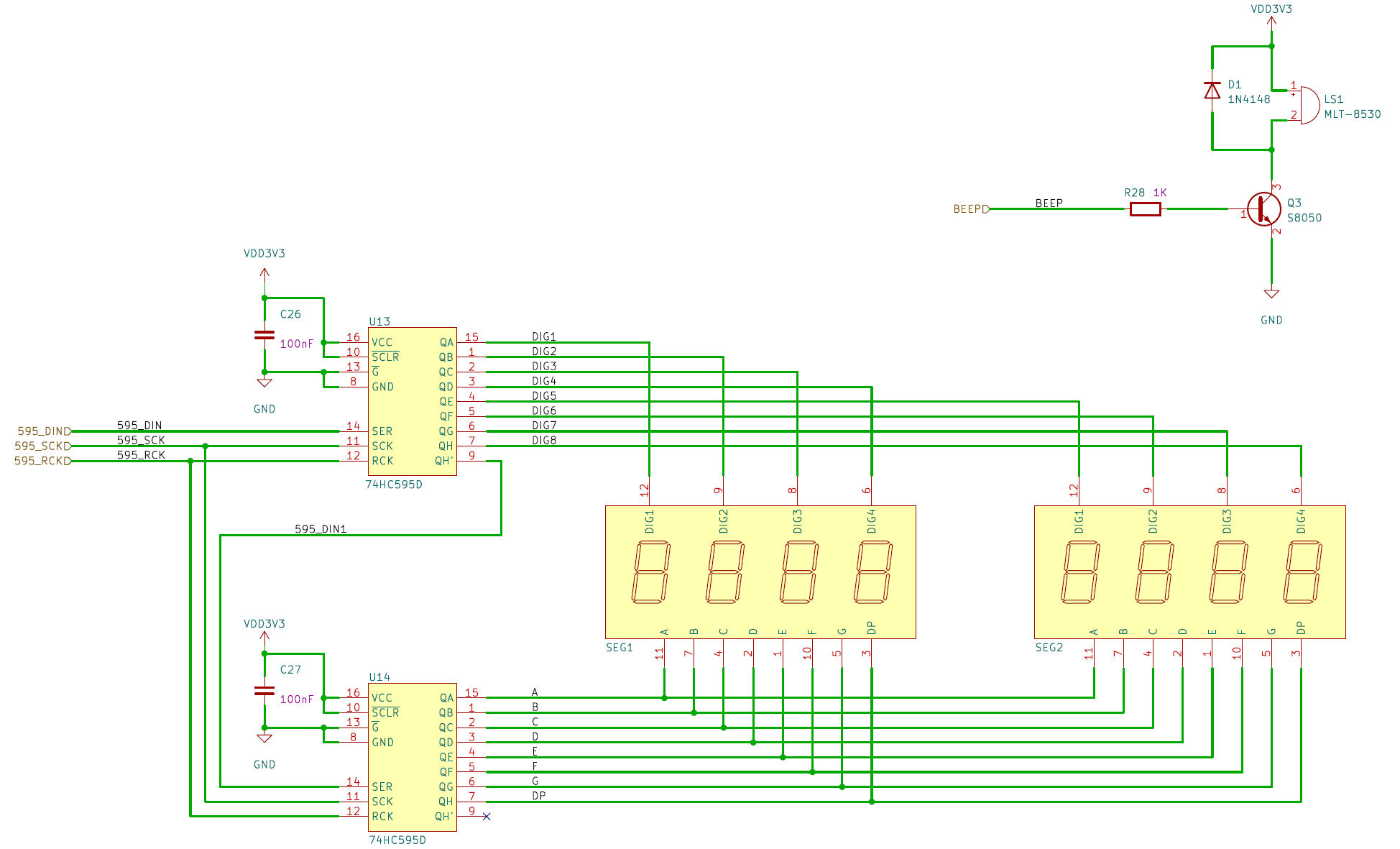

底板数码管及蜂鸣器

本模块通过两片74HC595级联实现数码管驱动,其中一片输出段码信号(控制各段LED亮灭),另一片输出位码信号(选择当前驱动的数码管位),采用动态扫描方式循环刷新显示。

蜂鸣器驱动电路基于NPN三极管设计,当FPGA输出高电平且伴随PWM方波信号时,三极管导通驱动无源蜂鸣器发声。

方案框图和项目设计思路

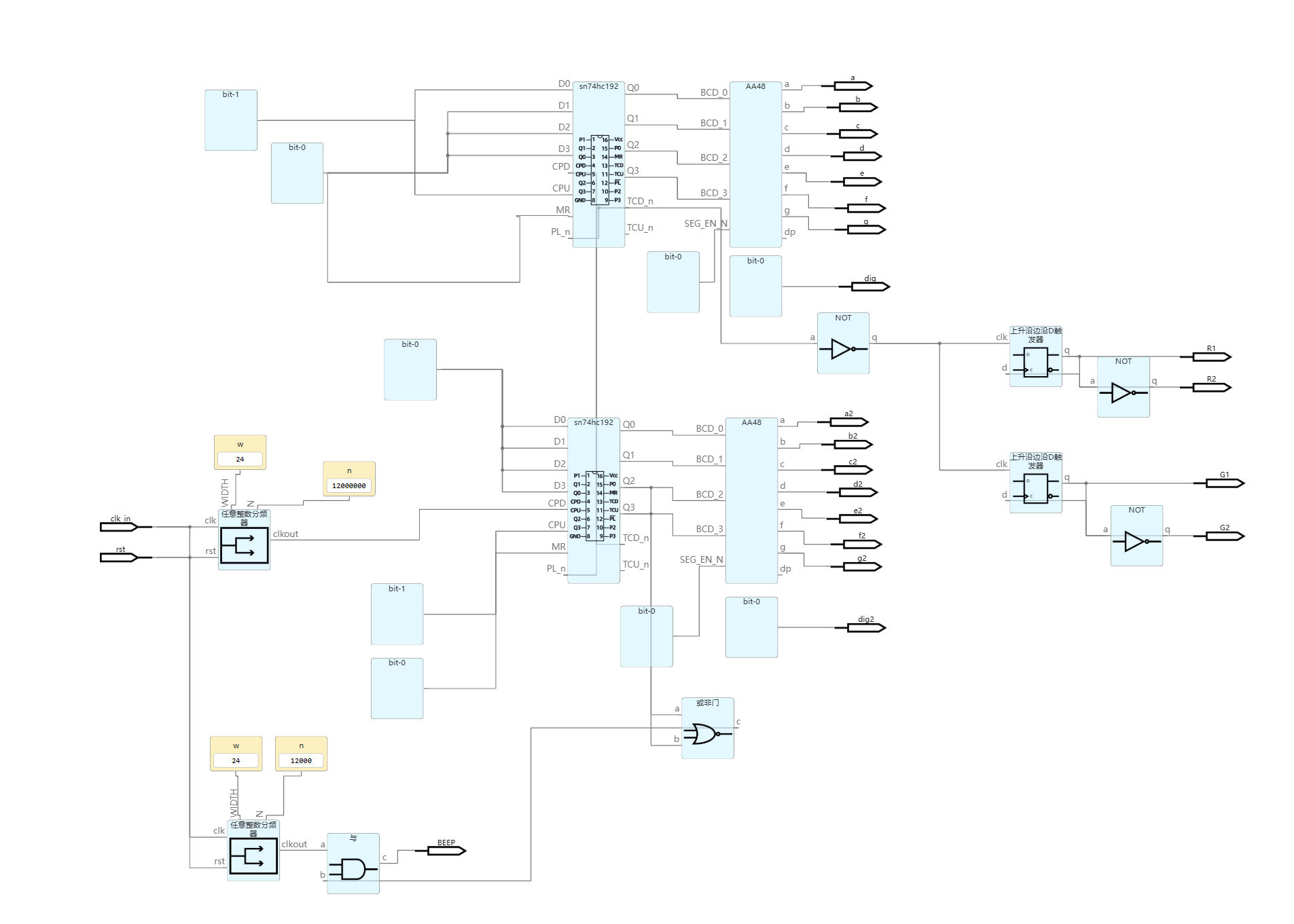

一、图形化编写部分

计时与蜂鸣器报警功能

- 倒计时芯片选择

在交通灯计时设计中,倒计时功能更符合人们的日常认知。经资料查阅,选用 74HC192 芯片来实现倒计时功能。该芯片具有诸多优势,例如它能够进行可逆计数,这对于倒计时场景极为适用。同时,74HC192 芯片支持级联操作,这意味着无论需要实现多长时间的倒计时,理论上都能够通过级联多个芯片达成。鉴于本设计旨在实现两位数的倒计时,所以选用两片 74HC192 芯片进行级联。当倒计时结束时,芯片能够发送信号至触发器,以此触发信号灯进行颜色切换。

- 数码管显示设计

为将倒计时时间准确显示在数码管上,考虑到 74HC192 芯片输出的是 BCD 码格式。通常情况下,可使用 74HC48 芯片来驱动数码管。然而,由于图形化内置模块中缺乏 48 译码器,所以需自行设计一个 48 模块。此自定义设计的 48 模块将负责接收 74HC192 输出的 BCD 码,并将其转换为能够驱动数码管正确显示数字的信号,从而实现倒计时时间在数码管上的清晰呈现。

- 蜂鸣器报警设计

该电路通过对时钟信号进行分频处理,获取 1kHz 的频率,该频率用于驱动蜂鸣器发声。并且,利用逻辑门对蜂鸣器进行控制,当倒计时时间小于设定的特定时间时,逻辑门导通,蜂鸣器开始报警,以提醒行人或驾驶员交通灯状态即将发生变化。

该部分设计框图如下:

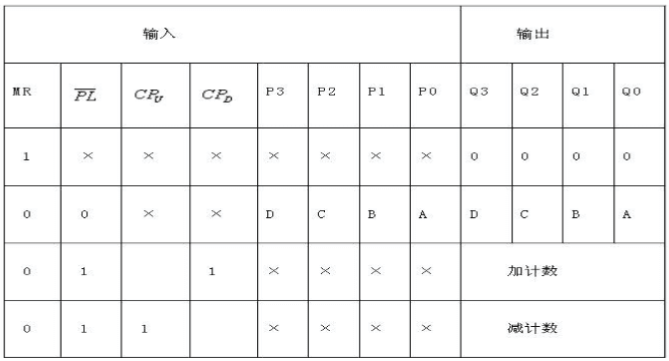

74HC192真值表:

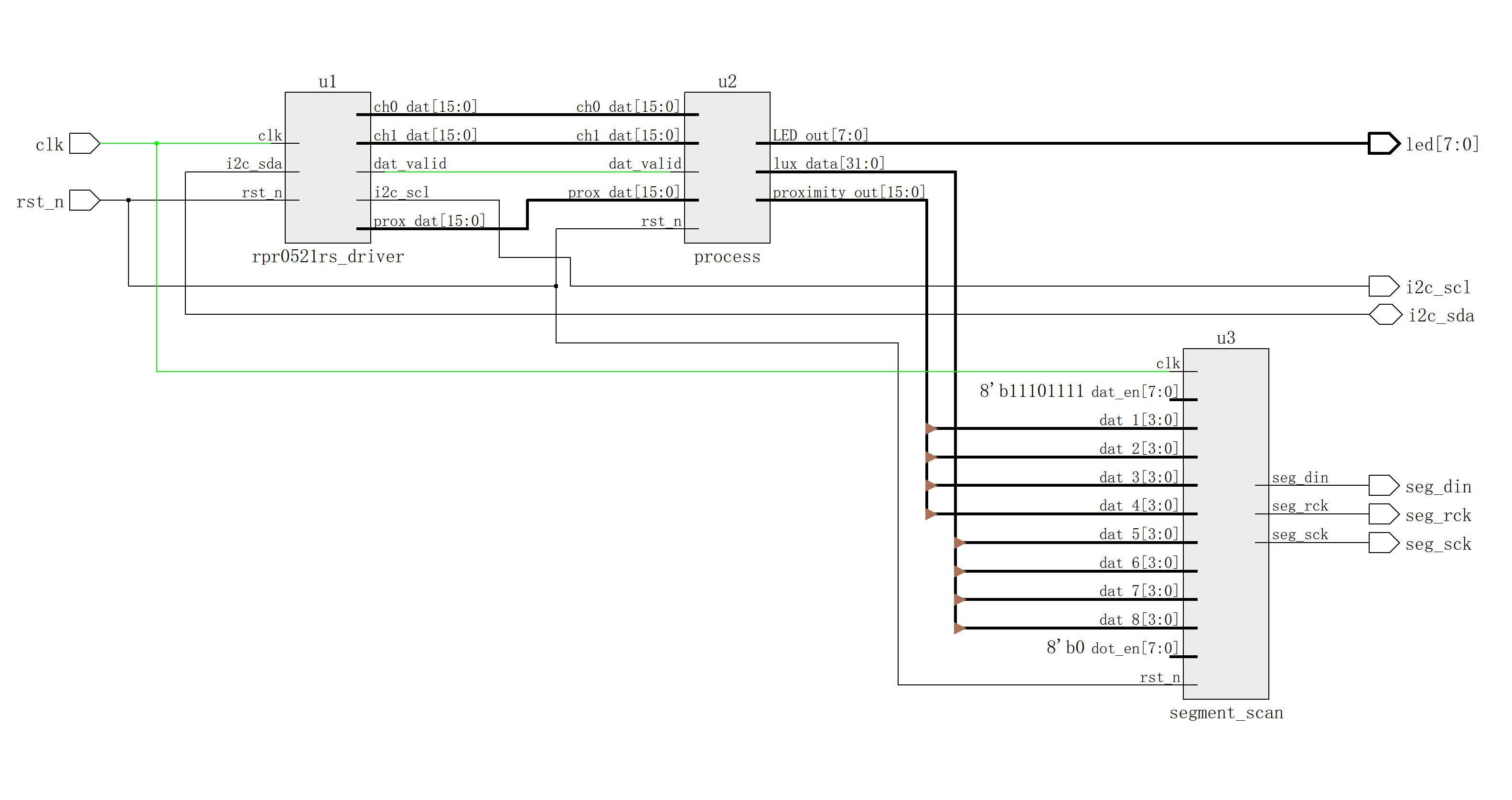

二、Verilog 代码编写部分

检测人员接近与环境光控制

该功能使用 RPR0521RS 传感器采集人员接近信息与光照强度数据。

- 人员接近信息方面,通过 FPGA 将接近传感器获取的值转换为 BCD 码,再由数码管显示,数值大小与人员接近程度正相关;

- 环境光控制部分,采集光照传感器数值并与预设阈值比较,若小于预设值则判定环境光过暗,开启 LED,反之则关闭 LED。

该部分设计框图如下:

关键代码介绍

图形化部分的代码

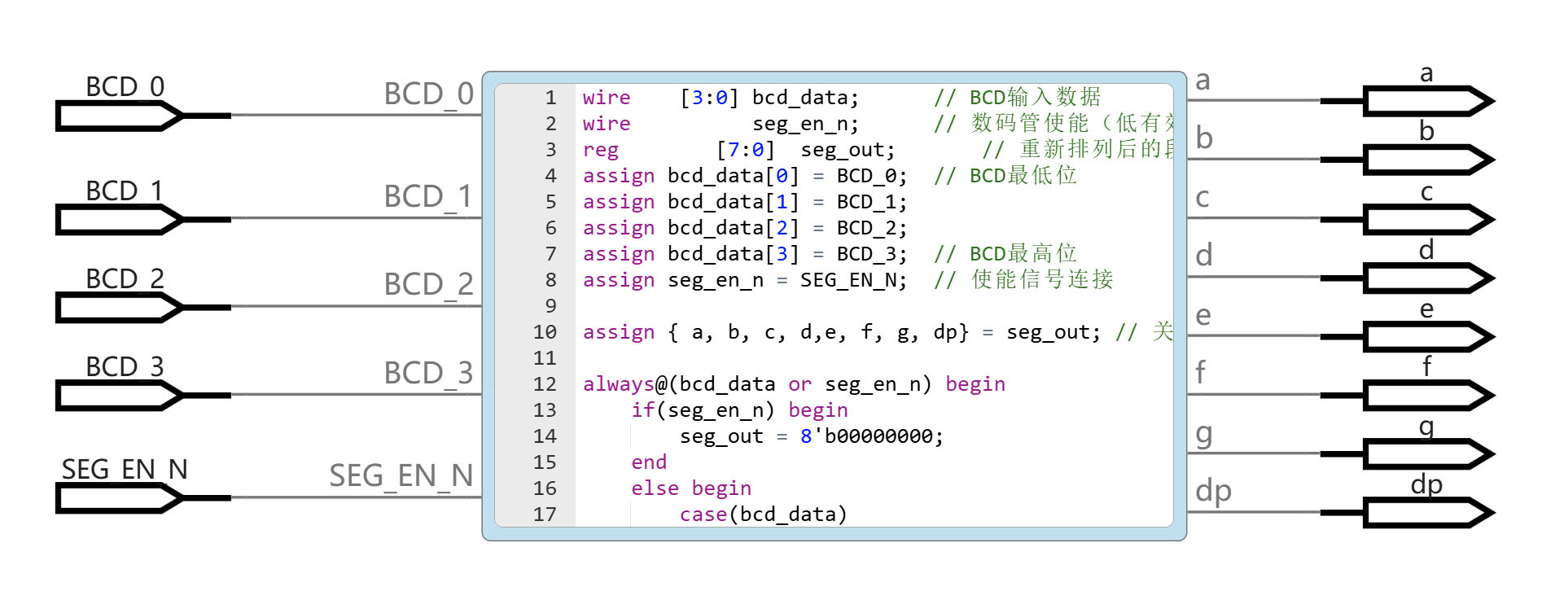

由于图形化的内置库中没有74HC48,因此该模块需要自行编写,该模块具有5个输入,8个输出,其中4个输入为BCD码输入,一个为使能端

模块代码如下:

wire [3:0] bcd_data; // BCD输入数据

wire seg_en_n; // 数码管使能(低有效)

reg [7:0] seg_out;

assign bcd_data[0] = BCD_0; // BCD最低位

assign bcd_data[1] = BCD_1;

assign bcd_data[2] = BCD_2;

assign bcd_data[3] = BCD_3; // BCD最高位

assign seg_en_n = SEG_EN_N; // 使能信号连接

assign { a, b, c, d,e, f, g, dp} = seg_out;

always@(bcd_data or seg_en_n) begin

if(seg_en_n) begin

seg_out = 8'b00000000;

end

else begin

case(bcd_data)

4'h0: seg_out = 8'b11111100; // 0

4'h1: seg_out = 8'b01100000; // 1

4'h2: seg_out = 8'b11011010; // 2

4'h3: seg_out = 8'b11110010; // 3

4'h4: seg_out = 8'b01100110; // 4

4'h5: seg_out = 8'b10110110; // 5

4'h6: seg_out = 8'b10111110; // 6

4'h7: seg_out = 8'b11100000; // 7

4'h8: seg_out = 8'b11111110; // 8

4'h9: seg_out = 8'b11110110; // 9

4'hA: seg_out = 8'b11101110; // A

4'hB: seg_out = 8'b00111110; // B

4'hC: seg_out = 8'b10010010; // C

4'hD: seg_out = 8'b01111010; // D

4'hE: seg_out = 8'b10011110; // E

4'hF: seg_out = 8'b10001110; // F

default: seg_out = 8'b00000000;

endcase

end

end

Verilog 部分的代码

人员接近部分实现:将接近传感器获取的数值转换为BCD码显示到数码上,使用双加三算法来实现BCD码的转换

reg [15:0] bcd_out;

reg [3:0] bcd[3:0]; // 4个4位BCD码

reg [11:0] temp_data;

// 双加三算法实现BCD码转换

integer i;

always@(*) begin

// 初始化

temp_data = prox_dat2[11:0];

for (i = 0; i < 4; i = i + 1) begin

bcd[i] = 4'b0000;

end

// 双加三算法

for (i = 0; i < 12; i = i + 1) begin

if (bcd[3] >= 4'd5) bcd[3] = bcd[3] + 4'd3;

if (bcd[2] >= 4'd5) bcd[2] = bcd[2] + 4'd3;

if (bcd[1] >= 4'd5) bcd[1] = bcd[1] + 4'd3;

if (bcd[0] >= 4'd5) bcd[0] = bcd[0] + 4'd3;

// 移位

bcd[3] = {bcd[3][2:0], bcd[2][3]};

bcd[2] = {bcd[2][2:0], bcd[1][3]};

bcd[1] = {bcd[1][2:0], bcd[0][3]};

bcd[0] = {bcd[0][2:0], temp_data[11]};

temp_data = {temp_data[10:0], 1'b0};

end

// 将BCD码存储到16位输出中

bcd_out = {bcd[3], bcd[2], bcd[1], bcd[0]};

proximity_out = bcd_out;

end

环境光控制LED部分,通过比较光强度转换为BCD码后的数值,若小于预设的数值,则电路LED,否则则关闭LED,该部分代码如下:

always@(T_data_bcd)

if(T_data_bcd[19:16] <4'b0001 && T_data_bcd[23:20] == 4'b0000)

LED_out = 8'b01111110; //点亮首尾的灯

else LED_out = 8'b11111111; //全部关闭

数码管显示的部分代码如下,8位数码管,最高三位显示人员接近程度,第四位熄灭作为分割,后四位显示光照强度:

process u2(

.rst_n (rst_n),

.dat_valid (dat_valid ),

.ch0_dat (ch0_dat ),

.ch1_dat (ch1_dat ),

.prox_dat (prox_dat ),

.lux_data (lux_data ),

.LED_out (led ),

.proximity_out(proximity_out)

);

segment_scan u4(

.clk(clk), //系统时钟 12MHz

.rst_n(rst_n), //系统复位 低有效

.dat_4(proximity_out[15:12]),

.dat_1(proximity_out[11:08] ),

.dat_2(proximity_out[07:04] ),

.dat_3(proximity_out[03:00] ),

.dat_5(lux_data[23:20] ),

.dat_6(lux_data[19:16] ),

.dat_7(lux_data[15:12] ),

.dat_8(lux_data[11:08] ),

.dat_en(8'b1110_1111 ), //数码管数据位显示使能,[MSB~LSB]=[SEG1~SEG8]

.dot_en(8'b0000_0000 ), //数码管小数点位显示使能,[MSB~LSB]=[SEG1~SEG8]

.seg_rck(seg_rck ), //74HC595的RCK管脚

.seg_sck(seg_sck ), //74HC595的SCK管脚

.seg_din(seg_din ) //74HC595的SER管脚

);

项目链接:交通灯计时及蜂鸣器报警部分

功能展示图

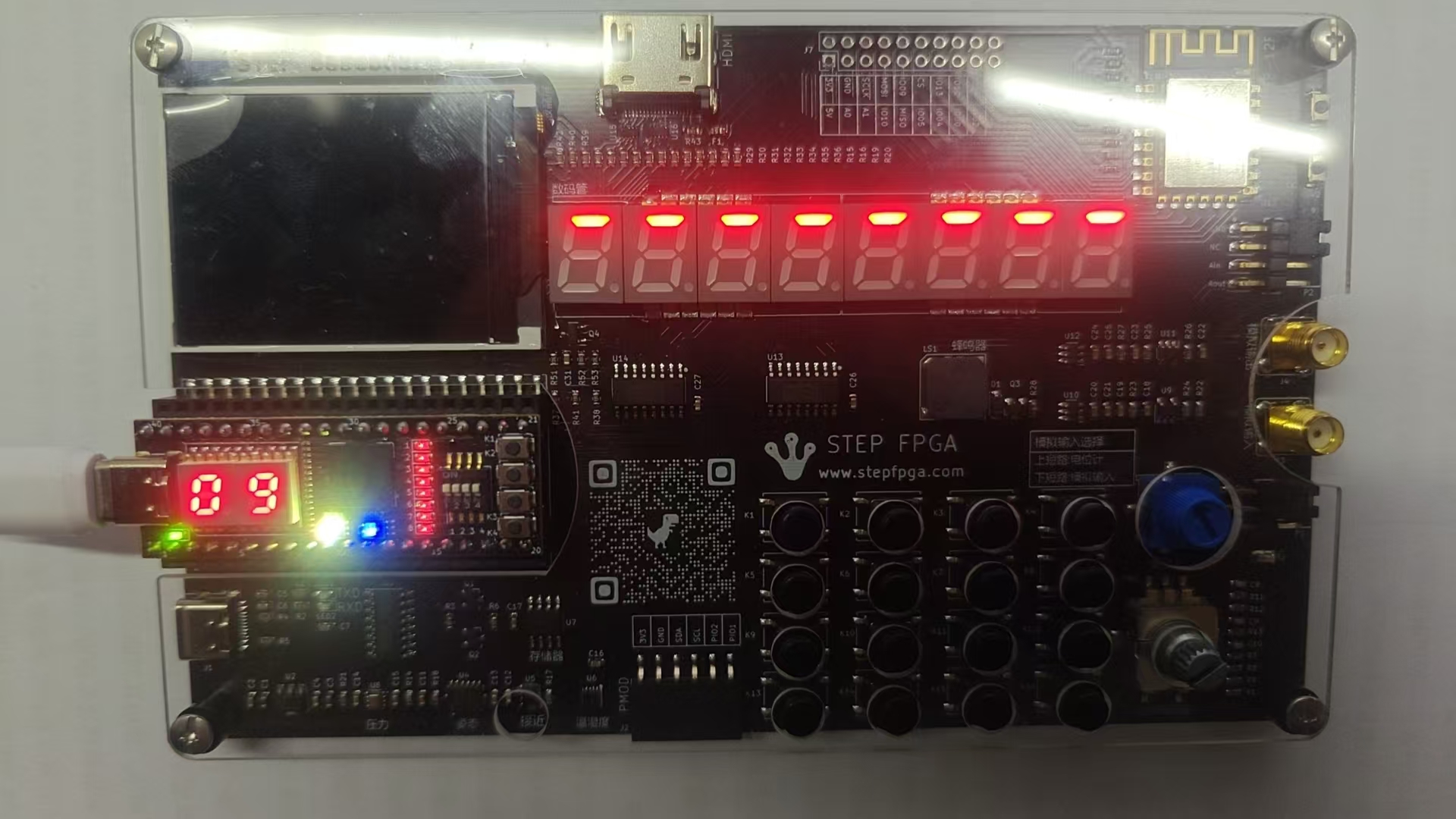

计时及蜂鸣器报警展示:

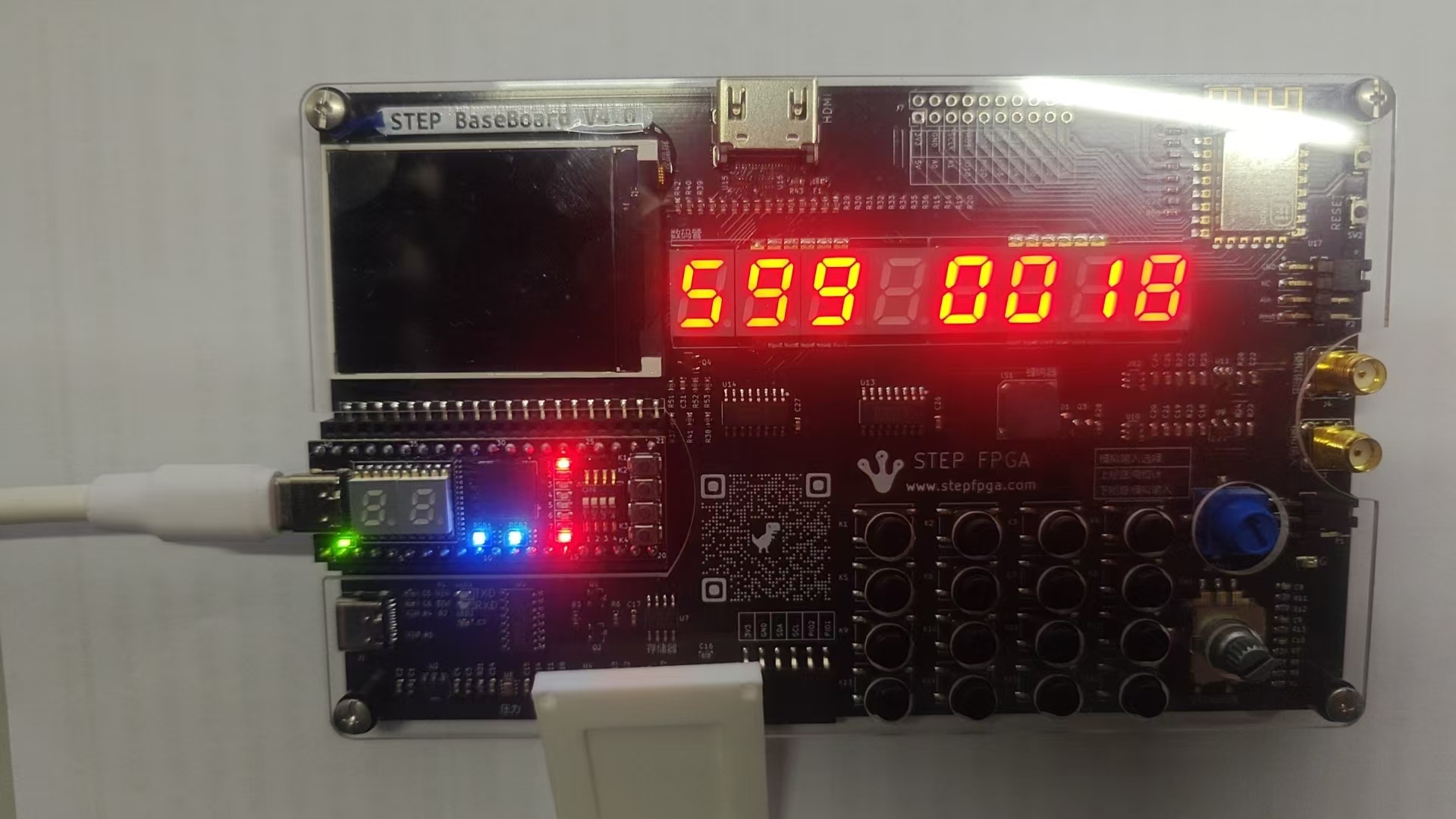

接近及光照检测展示:

FPAG资源使用情况

图形化部分资源使用情况:

Design Summary:

Number of registers: 92 out of 4635 (2%)

PFU registers: 92 out of 4320 (2%)

PIO registers: 0 out of 315 (0%)

Number of SLICEs: 108 out of 2160 (5%)

SLICEs as Logic/ROM: 108 out of 2160 (5%)

SLICEs as RAM: 0 out of 1620 (0%)

SLICEs as Carry: 77 out of 2160 (4%)

Number of LUT4s: 216 out of 4320 (5%)

Number used as logic LUTs: 62

Number used as distributed RAM: 0

Number used as ripple logic: 154

Number used as shift registers: 0

Number of PIO sites used: 23 + 4(JTAG) out of 105 (26%)

Number of block RAMs: 0 out of 10 (0%)

Number of GSRs: 1 out of 1 (100%)

EFB used : No

JTAG used : No

Readback used : No

Oscillator used : No

Startup used : No

POR : On

Bandgap : On

Number of Power Controller: 0 out of 1 (0%)

Number of Dynamic Bank Controller (BCINRD): 0 out of 6 (0%)

Number of Dynamic Bank Controller (BCLVDSO): 0 out of 1 (0%)

Number of DCCA: 0 out of 8 (0%)

Number of DCMA: 0 out of 2 (0%)

Number of PLLs: 0 out of 2 (0%)

Number of DQSDLLs: 0 out of 2 (0%)

Number of CLKDIVC: 0 out of 4 (0%)

Number of ECLKSYNCA: 0 out of 4 (0%)

Number of ECLKBRIDGECS: 0 out of 2 (0%)

Verilog 部分资源使用情况:

Design Summary

Number of registers: 399 out of 4635 (9%)

PFU registers: 394 out of 4320 (9%)

PIO registers: 5 out of 315 (2%)

Number of SLICEs: 1229 out of 2160 (57%)

SLICEs as Logic/ROM: 1229 out of 2160 (57%)

SLICEs as RAM: 0 out of 1620 (0%)

SLICEs as Carry: 500 out of 2160 (23%)

Number of LUT4s: 2457 out of 4320 (57%)

Number used as logic LUTs: 1457

Number used as distributed RAM: 0

Number used as ripple logic: 1000

Number used as shift registers: 0

Number of PIO sites used: 15 + 4(JTAG) out of 105 (18%)

Number of block RAMs: 0 out of 10 (0%)

Number of GSRs: 1 out of 1 (100%)

EFB used : No

JTAG used : No

Readback used : No

Oscillator used : No

Startup used : No

POR : On

Bandgap : On

Number of Power Controller: 0 out of 1 (0%)

Number of Dynamic Bank Controller (BCINRD): 0 out of 6 (0%)

Number of Dynamic Bank Controller (BCLVDSO): 0 out of 1 (0%)

Number of DCCA: 0 out of 8 (0%)

Number of DCMA: 0 out of 2 (0%)

Number of PLLs: 0 out of 2 (0%)

Number of DQSDLLs: 0 out of 2 (0%)

Number of CLKDIVC: 0 out of 4 (0%)

Number of ECLKSYNCA: 0 out of 4 (0%)

Number of ECLKBRIDGECS: 0 out of 2 (0%)

遇到的难题及解决办法

这次需要使用74逻辑电路进行搭建交通灯电路,更考验逻辑思维的能力,之前都是使用代码编写,缺少对逻辑思维的训练,因此感到一定的难度,通过上网查找资料以及观看视频,渐渐熟悉了这种设计思路,同时使用其他的电路仿真软件先进行搭建,然后再到fpga上进行验证,效率也有很大的提升。

心得体会

之前都是使用单片机进行编写程序,这次是第一次尝试接触FPGA的设计,从代码编写,引脚分配,以及模块化的思想在FPGA上有了更好的体现,学到了一种新的处理问题的思路。

建议:建议硬禾继续完善一下webIDE,感觉使用上仍有很大的提升空间,希望国产软件越来越好。