Github:Simple stm32 oscilloscope

介绍

过去,我曾承担过涉及带有高速 ADC 的便携式示波器(如 RPScope 中所示)的项目。 然而,在这一努力中,我致力于最大限度地简化电子设备,并仅利用 STM32 平台固有的功能。

STM32G4系列具有多种模拟外设,包括4个ADC、2个DAC、集成OPAMP 等,这些外设有助于最大限度地减少物料清单 (BOM)。 唯一使用的外部部件是两个 OPAMP IC,主要用于保护 MCU 免受输入通道过压的影响。 供电方面也进行了简化; 与此类项目中经常采用的传统对称电源配置不同,我专门采用了单端电源,进一步简化了电路。 尽管存在这种偏差,但仍然可以通过在输入级引入偏移来支持对负电压信号的采集。

该示波器拥有480x320 分辨率显示屏,通过16位总线连接并映射到STM32的内存,提供快速数据传输并实现超过50FPS的令人印象深刻的帧速率,但我刻意限制为20 FPS以确保CPU能够流畅地支持其它并发任务。 图形用户界面是通过 Nuklear 库的端口实现的,最初用于 PC 游戏,采用 ANSI-C 编写,采用模块化设计,可在微控制器内无缝执行。

硬件制造委托给嘉立创,PCB为4层,遵循其规定的 0.1毫米线间距和宽度以及0.35毫米通孔直径的最小设计限制。 虽然对于这个设计来说并不是绝对必要的,但我很想评估结果,事实证明这是完美的。 尽管是间接的,人工智能也融入到了该项目(中途)中,体现在 PCB 丝印层中融入了“Mechwarrior”机器人绘图,赋予了独特的视觉风格。

在软件方面,我最初的意图是集成 MicroPython,这一雄心促使 Nuklear 移植到 MicroPython 生态系统。 但由于RAM资源有限,我选择使用C语言进行开发,并辅以FreeRTOS操作系统框架。

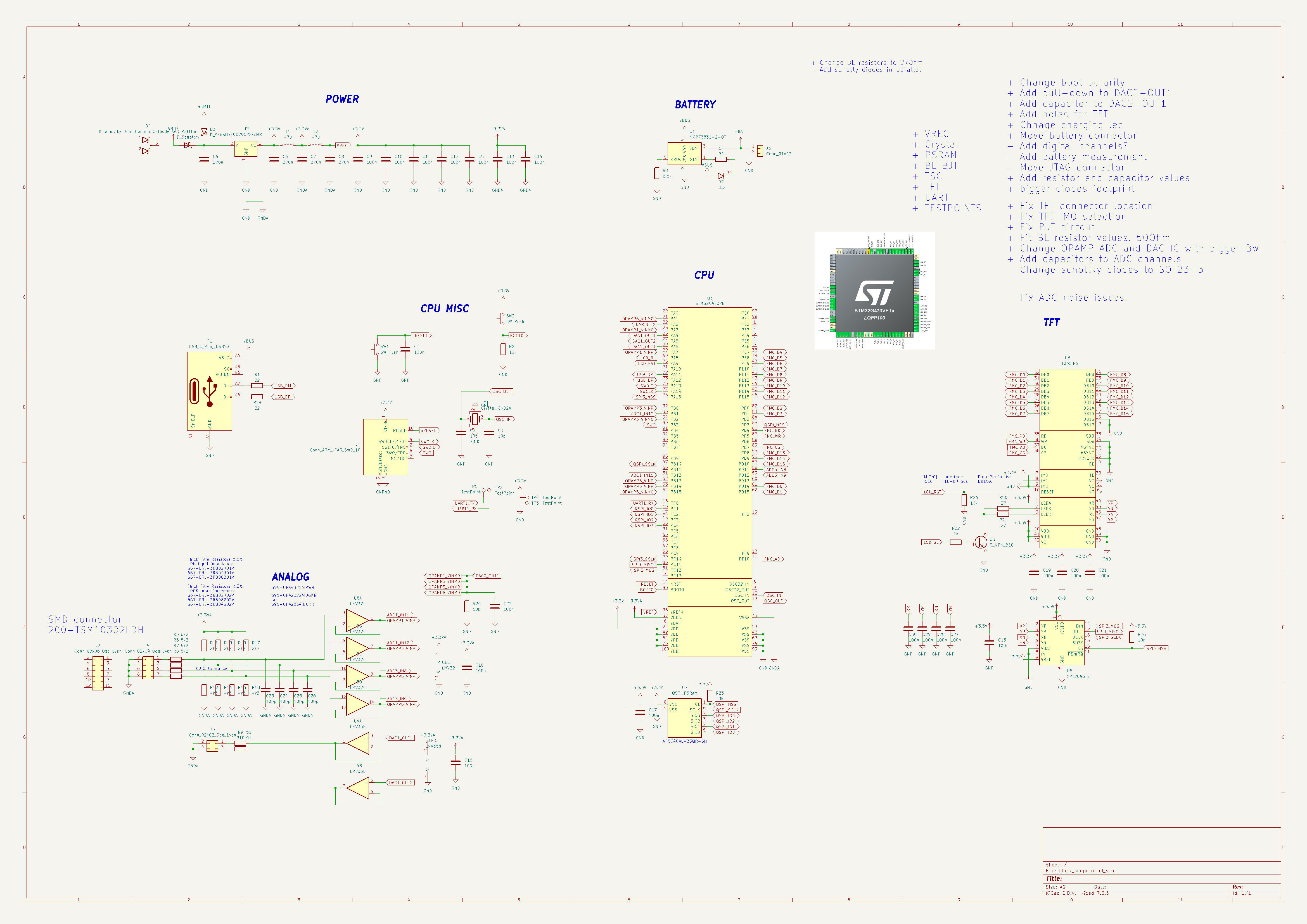

硬件

硬件设计的特点是简单,主要包括STM32微控制器、两个运算放大器(OPAMP)、一个电池充电器和一个TFT显示屏。

供电:

电源子系统主要包括一个3.3V稳压器和LiPo电池充电模块。 如果连接了USB,整个系统通过USB供电,同时为锂聚合物电池充电。 当没有USB连接时,电流通过肖特基二极管输送至电压调节器。

模拟电压直接来自数字领域,并通过电感器进行最小程度的过滤。 如果使用一个单独的稳压器为模拟电路供电效果会更好,但在这里没有采用。 该设计的内在优势在于无需对称电源,从而显着简化了物料清单 (BOM)。

在这个版本中,模拟和数字接地层是互连的,因此不需要单独的接地层。 后续版本将探索具有隔离接地层的设计,以评估其对降低噪声起到的作用,特别是在测量小电压信号时。

电池充电模块采用简单的 SOT23-6 IC 实现,可轻松为 130mAh 锂电池充电。 LED 指示灯在充电过程中亮起,完成后熄灭。 充电周期约为一小时,可提供约两小时的运行时间。 虽然这个持续时间似乎有限,但经过深思熟虑,我们选择了紧凑的电池占用空间,并且当需要延长使用时间时,示波器可以轻松地与移动电源连接。

电池供电电压约为 3.7V,而电路的运行功耗则在80mA上下。 值得注意的是,在此电流水平下测量的肖特基二极管的压降约为 400mV,对到达电压调节器的电压施加了轻微的限制。 因此,未来的改进考虑了两个肖特基二极管的并联集成,从而减轻每个二极管的电流负载并随后降低电压降。

处理器:

该系统的核心是STM32G474VE,这是一款以170 MHz 时钟频率运行的 Cortex-M4F 处理器。 该微控制器采用 TQFP-100 封装,拥有值得称赞的 512 KB 闪存和 128 KB RAM。 目前,代码库仅占用 20% 的可用闪存,而操作需求则占用 90% 的已分配 RAM。 此外,硬件接口使用了一半的可用 GPIO 引脚。

该微控制器固有的广泛集成外设一直是大幅削减物料清单 (BOM) 的关键推动因素。 特别是,包含 4 个 ADC 非常有帮助。 同样值得注意的是集成运算放大器 (OPAMP),它超出了其传统用途,可用作具有独立偏移输入的可编程增益放大器 (PGA)。 这种多功能性极大地增强了系统的功能,提供了适应不同输入条件的便捷方法。

TFT和TSC

TFT 显示屏拥有令人印象深刻的480x320 像素分辨率,并由 ILI9488 控制器支撑。 它通过 16 位 8080 并行总线实现与 CPU 的无缝链接,建立强大的连接以适应高速数据传输。

CPU 利用灵活内存控制器 (FMC) 外设,利用内存映射方法与 LCD 接口。 这种便捷的数据访问方法不仅可以加快图像渲染速度,还有助于实现显着提高的帧速率,超过 50 FPS。 FMC 将 LCD 视为存储器的无缝扩展,从而显着提高了数据传输效率。

TFT 显示器的采购不仅仅是从 Mouser 等老牌供应商处购买集成组件。 通常,在亚马逊或全球速卖通等平台上追求经济高效的解决方案会导致价格低廉的显示器缺乏全面的文档,包括数据表、引脚排列和尺寸规格。 buydisplay.com 是应对这一挑战的可靠资源,它提供各种显示器以及必要的文档,从而简化了集成过程。

触摸屏控制器 (TSC) 通过 SPI 总线连接到 CPU,能够以 1 MHz 读取速率高效运行。 在整个软件开发阶段,很明显 TSC 测量表现出一定程度的噪声,促使读取频率增加以实现有效过滤。 正如原理图设计所示,最初尝试通过在 XP/XN/YP/YN 线路中引入电容器来减轻这种噪声,但在评估后却产生了不确定的结果。 这方面仍然是进一步研究的焦点,因为优化降噪的努力继续推动不断的探索和完善。

设计中有两个需要改进的领域值得关注。 首先,集成了 IPS(面内切换)TFT 显示屏,该显示屏以其卓越的视觉质量和显着增强的视角而闻名。 尽管这些显示器可以通过 buydisplay.com 等来源轻松获得,但采购过程中的不幸疏忽导致我们选择了替代显示技术。 这一调整有望显着提升整体用户体验,最终增强视觉保真度和更广阔的观看视角。

另一个重要方面涉及亮度考虑。 由于紧凑型电池的限制,亮度和电池寿命之间的相互作用显得尤为突出。 提高的亮度总是会对操作耐久性产生相应的影响。 因此,为了确保使用时间超过一小时,有意识地将亮度降至最低。 平衡亮度与电池寿命成为一项关键工作,需要进行战略优化以达到平衡,从而在不影响显示可视性的情况下延长操作时间。

模拟输入和输出级

输入级由五个不同的块组成,其中一些集成在 STM32 中:

- 电阻分压器和低通滤波器:

入口点需要一个电阻分压器网络,每个通道都有一个电容器。 这种复合配置具有多方面的作用,包括阻抗匹配、电压范围调节、适应负电压的偏移配置以及高频滤波。 这种混合物确保了后续处理的精细输入信号。

- 外部运算放大器 (OPAMP):

信号路径中的关键元件是外部运算放大器 (OPAMP)。 通过采用 TI 的 OPA4322,信号经历了必要的转换,起到射极跟随器的作用。 该运算放大器的带宽为 20 MHz,超过了输入级的带宽,有助于高转换率信号处理,而不会引入失真。

-内部运算放大器和PGA:

经过外部放大后,信号进入集成运算放大器和可编程增益放大器 (PGA) 单元。 这些多功能组件能够放大 x2 至 x64 范围内的信号。 该放大范围带来了动态多功能性,允许捕获从毫伏到伏特范围内的信号,而无需外部电路。 PGA 的外部偏移输入的结合,以及使用额外 STM32 DAC 的补充,避免了任何残余偏移的放大。

-偏移DAC:

为了响应前一阶段引入的偏移,STM32 上的专用数模转换器 (DAC) 可以抵消这种影响,确保信号保真度并减轻偏移失真。

-ADC:

最终阶段需要将放大并经过偏移校正的信号传输到各个模数转换器 (ADC),每个模数转换器服务于一个单独的通道。 这种细致的分配有助于每个通道实现最大采样率,从而保持信号完整性。

该设计的主要限制涉及所有通道的统一偏移。 输入级电阻的高容差可能会阻碍每个 PGA 的放大过程。 为了缓解这个问题,输入级电阻经过精心选择,精度为 0.5%,确保均匀的放大性能。

此外,还出现了一个意想不到的挑战,涉及指定用于 PGA 偏移的引脚,这些引脚在 ST 的引导加载程序操作期间同时充当 UART2 引脚。 通过引入下拉电阻器和电容器实现整流,从而在正常工作阶段保持稳定的 DAC 电压。

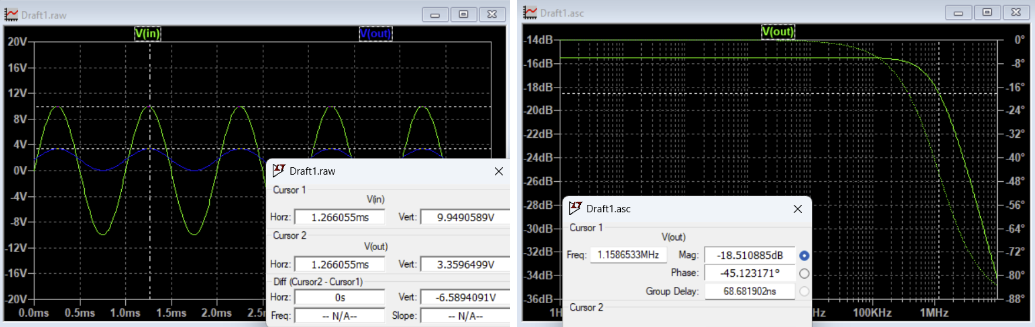

过渡到输出级,这种布置合并了 STM32 的 DAC、运算放大器和 50 欧姆电阻。 这种协同作用能够生成各种波形,包括 PWM、正弦波、三角波甚至仲裁模式,最大频率高达 1 MHz,但始终限制在 0 至 3.3V 电压范围内。

此外,模拟信号输入部分被设想为提供四个输入通道以及两个差分通道的潜力。 虽然尚未得到验证,但硬件的基础结构可以适应这种预期的扩展。

PSRAM

PSRAM 的加入为微控制器设计引入了一个迷人的维度,尤其是它们在 ESP32 等平台中的普遍使用。 这种独特的硬件资源释放了利用数兆字节内存的潜力,同时发挥最少的引脚数,并且不会带来不必要的软件复杂性。 在此背景下,无缝集成了 8 MB 的 PSRAM 模块,通过四路串行外设接口 (QSPI) 互连,与直接内存访问 (DMA) 功能协同工作时,可提供每秒10MB 的令人印象深刻的读写速度 。

这种务实的集成带来了多种好处,包括增加可用内存,这是支撑多方面应用程序的基石。 虽然 PSRAM 确实有助于内存映射,但此功能是专为读取操作而定制的。 因此,该设计明智地保留了通过 QSPI 寄存器进行的访问,与 DMA 协调一致,优化了数据流并增强了整体性能。

PSRAM 的战略部署增强了设计的数据处理能力,实现无缝数据存储、检索和处理,从而增强了微控制器在要求苛刻的计算和数据密集型场景中的功效。 这种增强与支撑整个设计工作的效率和资源优化的精神相协调。

印刷电路板

PCB 外形紧凑,尺寸为 90x60mm,经过精心设计,与 TFT 显示器规格相协调。 该设计采用 4 层配置,封装了复杂电路的共生融合,促进无缝操作。

这种设计叙述的核心是将 CPU 战略定位在主板的核心,并方便地由一系列战略性外围组件包围。 正如所见,TFT 的柔性印刷电路 (FPC) 连接器占据了电路板右侧的整个长度,建立了定义性的设计范例。 特别是,这种空间分配赋予了引人入胜的视觉维度,因为曾经空置的区域被巧妙的创造所点缀:人工智能生成的机器人,象征着技术和创意独创性的逐步融合。

设计规则

值得注意的是,PCB 的制造成本仅为 2 欧元——这是一项非常经济的投资,但却掩盖了复杂设计的潜力。 传统的设计范例通常优先考虑功能而不是尺寸优化,这种方法被认为足以满足大多数应用的需求。 然而,在实验冲动的推动下,该项目的轮廓出现了分歧。 在 16 位 TFT 总线的指导下,我们共同努力确定制作超紧凑设计的可行性,并以利用 JLCPCB 的制造能力这一雄心勃勃的目标为基础。

结果证明了创新设计和先进制造技术的融合。 该项目只花费了象征性的费用,推出了经过精心蚀刻的 4 层 PCB,以适应显着提高的复杂程度。 结果简直令人着迷。 以具有成本效益的方式实现如此精致的设计,凸显了当代制造能力的变革潜力,举例说明了如何不断重新定义成本和规模的限制,从而可以追求曾经超越可行性界限的大胆设计理念。

PSRAM长度匹配

迭代开发过程中夹杂着宝贵的见解,为项目设计的演变提供了信息。 这种动态的一个显着例子是在探索 PSRAM 通信速度期间展现的,揭示了最终转化为性能优化的重要观察结果。

在 PCB 的首次迭代中,追求与 PSRAM 的最佳通信速度提出了挑战。 值得注意的是,事实证明,高速运行的尝试难以实现,这促使人们重新评估设计的架构。 后续版本(标记为 v2)带有您解决此问题的决心。 一个新颖的概念被提出:专门匹配 PSRAM 接口的走线长度。 从理论上讲,这种调整可能看起来不协调,因为走线长度匹配传统上是为明显超过 100 MHz 阈值的频率保留的。 然而,创新精神占了上风,PCB 的空间配置适应了这种实验性的偏离。

在部署 v2 PCB 时,经验观察优先于理论预测。 然而,机缘巧合发挥了作用,因为预期的改善仍然难以捉摸。 事实证明,根本原因不在于走线长度,而在于 GPIO 速度配置。 这一发现虽然偏离了最初的假设,但却体现了迭代设计的本质——在这个过程中,实验和调查往往会带来微妙的启示。

这一令人心酸的事件不仅展示了设计工作固有的弹性和适应性,还强调了设计软件 KiCad 中嵌入的丰富功能。 务实探索和技术细微差别的融合协调一致地扩大了该项目的发展轨迹,而该项目本身证明了支撑电子设计领域的完善和创新能力。

3D外壳

为了追求具有专业外观的电子设计,将其封装在外壳内的前景具有不可否认的吸引力。 然而,对于那些缺乏经验的人来说,3D 设计领域可能是一个巨大的挑战。 值得庆幸的是,机缘巧合让我发现了一些库(通过 Hackaday 的一篇文章发现),它提供了一个无缝创建紧密包裹 PCB 外壳的途径,并配有方便定位的孔。 更重要的是,这个过程是由编程逻辑支撑的,这是经验丰富的软件工程师经常涉足的领域。

这些 3D 设计库与我的工程智慧之间的共生关系已转化为精确性与创造力的和谐结合。 制造与 PCB 无缝集成并容纳其组件的外壳的能力不仅实用,而且具有固有的审美吸引力。

当我开始这项事业时,技术专长与设计天赋的融合变得显而易见。 这种协同作用使我能够超越单纯功能的领域,深入研究触觉美学和触觉美学的领域,其中形式与功能的交集被巧妙地精心策划。 通过这些库和以软件为中心的方法,电子产品的封装过程呈现出一种新的可访问性,开创了一个专业技巧和手工独创性的时代。

事实上,三维可视化的实用性超出了外壳设计的范围。 有时,需要在开始制造过程之前获取 PCB 模型。 这一先发制人的步骤用于验证尺寸、评估连接器布局并确保整体设计的一致性。 在 Kicad 领域内,此功能是无缝集成的,能够在三维环境中可视化 PCB,然后以 STL 格式导出,为 3D 打印做好准备。

这种能力成为一种无价的资产,弥合了抽象数字布局和有形物理表现之间的鸿沟。 与 PCB 的触觉、视觉表示进行交互的能力超越了二维设计的传统限制,提高了制造过程的信心和准确性。

通过利用 Kicad 的沉浸式 3D 可视化和导出功能,工程之旅达到了一个新的维度——精心的规划与切实的成果相结合。 数字精度和触觉参与的融合不仅简化了设计迭代,而且还培养了对理论与具体化之间错综复杂的相互作用的更深刻的理解。 因此,从概念化到实现的道路变得更加清晰和丰富的可能性。

软件

介绍

该项目的软件尚未完成,但它已经包含主要部分,例如使用触发器或图形库进行信号捕获。 它基于 FreeRTOS,但目前它只有两项任务,一项是捕获 TSC,另一项是管理屏幕和 ADC。

采集系统

整个项目的核心在于通过 ADC(模数转换器)精心策划的复杂的信号捕获过程。 这一关键工作是通过协同 TIMER、ADC 和 DMA(直接内存访问)子系统来执行的。 此外,ADC 的窗口检测器用于触发检测,而附加计时器则在检测到触发时发挥停止操作的作用,从而以四重排列编排这首交响曲,反映了四个通道的作用。 值得注意的是,四个可编程增益放大器 (PGA) 和一个数模转换器 (DAC) 有助于生成必要的偏移。

该过程通过在信号捕获开始时启动 TIMER1+ADC+DMA 来启动。 编排扩展到通过 HAL_ADC_ConvCpltCallback 机制耐心等待第一次中断,以确保缓冲区中不断填充当前数据。

ADC 中断后,AWD1 被激活,负责检测触发器的启动,当输入电压低于阈值时启动。 触发电压的下降会产生 AWD1 触发的中断。 随后,AWD2 配置随之发生,准备识别随后的电压浪涌 - 代表“上升沿”的事件。

当 AWD2 触发中断实现时,TIMER2 在 OnePulseMode 下被调用。 TIMER2 被定位为一个警惕的哨兵,在缓冲区的剩余一半逐渐填满时等待时机。

随着渐强的临近,TIMER2 精心策划其最后的动作——一个同时停止 TIMER1、ADC 和 DMA 操作的中断。 在此编排过程中,DMA 寄存器充当精确触发发生时间戳的保管人,以及为后续可视化做好准备的大量数据。

该系统由定时器、转换器和内存访问组成的复杂舞蹈不仅实现了信号采集,而且展示了将原始数据转化为有意义的洞察画布的艺术性。 这种细致的编排体现了工程与精度的交叉,为整个项目奠定了基础。

信号产生

与信号采集的复杂性相比,信号生成领域采用更直接的方法。 这个方面是通过 TIMER、DAC 和 DMA 协作的经过验证的结构来实现的。

编排随着定时器、DAC 和 DMA 的同步展开,每个组件和谐地执行其指定的角色。 这种协同作用最终会生成精确的受控信号,从而精细而准确地呈现复杂的波形。

在这一努力中,定时器充当指挥者,决定信号发射的节奏。 DAC 类似于艺术大师,将数字指令转换为模拟和声。 同时,DMA 充当灵活的中介,促进数据从内存到 DAC 的无缝传输,从而进入模拟域。

这些努力的顶峰体现在波形的交响乐中,精度和电子技巧的优雅相互作用。 虽然信号生成在概念上可能比其采集对应部分更简单,但它仍然是一个不可或缺的组成部分,赋予项目多功能性和完整性。

液晶显示屏

LCD 由使用灵活内存控制器 (FMC) 接口的 ILI9488 控制器驱动。 FMC 配置通过 CubeMx 中提供的图形工具得到简化。 为了与 LCD 进行交互,需要映射两个内存地址,从而能够将命令和数据传输到 LCD。

用于 LCD 访问的存储器地址如下:0x60000000 作为 FMC 映射的基地址,而 0x60000002 激活 LCD 的数据/命令(DC)引脚,该引脚链接到 A0 引脚。 使用 0x02 而不是 0x01 是由于使用了 16 位总线宽度。

这种细致的内存映射在控制器和 LCD 之间建立了一座通信桥梁,协调指令和数据的流畅交换。 内存地址的战略性利用提高了项目的效率,并为显示子系统提供了结构化的基础。

随后,更高级别的功能开始发挥作用,为 LCD 管理提供更抽象的方法。 这些功能促进了从 LCD 初始化和像素渲染到图像传输的任务,简化了与显示子系统的交互。

在初始化阶段,这些函数提供了一种简化的方法来配置 LCD,微调参数以获得最佳性能。 这不仅加快了设置过程,而且还确保显示器在所需规格内无缝运行。

此外,绘制单个像素或传输整个图像的能力体现了这些高级功能的多功能性。 通过封装复杂的低级操作,这些功能使开发人员能够专注于项目的更广泛目标,而不会陷入错综复杂的显示问题的泥潭。

通过这些直观的界面,LCD 成为一个富有表现力的画布,随时可以显示可视化、用户界面或任何所需的内容。 低级硬件交互和高级抽象的融合形成了一个强大的框架,无缝地弥合了技术复杂性和创意表达之间的差距。

帧缓冲区

访问 LCD 本质上是很快的,但是当访问内部 RAM 时,速度会进一步加快。 因此,通常的做法是利用 CPU RAM 的一部分进行绘图操作,然后通过一次操作将整个内容传输到 LCD。 这种策略消除了在屏幕上操纵光标的需要——对于 LCD 和 CPU 来说,这是一个相对悠闲的过程。 相反,在 CPU 领域内,通过诸如“fb->buf[x+y*fb->width]=color;”之类的语法,操作变得方便。

在此架构中,帧缓冲区 (framebuf) 发挥着关键作用,包含用于渲染线条、矩形、文本等的基本例程。 它建立了一个抽象层,在 CPU 的 RAM 缓冲区内协调像素级操作。 这个中间步骤充当桥梁,使开发人员能够专注于图形设计和内容创建,而不会受到与 LCD 操作相关的复杂问题的阻碍。

帧缓冲区的利用不仅提高了操作效率,而且还促进了更符合人体工程学的开发工作流程。 它强调了硬件级加速与基于 CPU 的操作固有的灵活性之间的共生和谐,最终带来流畅且动态的连贯视觉体验。

字体

字体构成了在屏幕上呈现文本的关键工具,与封装文本内容的数组协同工作。 该项目的这个方面需要一组选定的功能,包括确定字符和单词尺寸,以及将单个字符转换为像素表示的机制。

字体管理的本质在于它的简单性——提供一系列简洁的函数来测量字符或单词的宽度和高度。 这些功能赋予了有效测量和分配空间的能力,确保文本适当地容纳在屏幕画布内。

此外,负责字符到像素转换的函数是关键,将每个字符的抽象本质转换为其图形表现形式。 此操作的执行将艺术性与工程精度无缝地融合在一起,使角色在屏幕上栩栩如生。

从本质上讲,字体管理封装了文本操作的本质,将字符转换为视觉实体,同时遵守空间限制。 这些功能的合并不仅丰富了视觉呈现,还简化了将文本内容集成到整体显示环境中的过程。

Nuklear IMGUI

Nuklear 库最初是为 PC 游戏开发量身定制的,通过无缝穿越从游戏到微控制器的领域,证明了其多功能性。 它的 ANSI-C 基础和缺乏依赖性使其成为移植的即时候选者。 这个库是简单中优雅的缩影,很容易接受 TSC 坐标作为输入,作为回报,编排线条、框和文本的动态整体的创建。 这些图形实体合并成一个连贯的视觉表示,并通过帧缓冲区进一步实现。

Nuklear 将自己区分为立即模式 GUI,它引入了一种与以回调为特征的传统 GUI 范例不同的方法。 在 Nuklear 中,GUI 的代码直接集成到应用程序中,赋予它简单性和控制性的有趣组合。 这种独特的特性营造了一种环境,其中 GUI 的行为根深蒂固于应用程序的逻辑中,将其提升为用户体验的沉浸式且不可或缺的方面。

Nuklear 和framebuf 的共生融合超越了单纯的美学,提供了用户交互的有形表现。 这种集成植根于编程的优雅和以用户为中心的设计,最终实现了功能和美学的和谐结合——证明了软件开发领域蓬勃发展的适应性和独创性。

一个有趣的方面在于能够避开覆盖整个屏幕的帧缓冲区,而是选择局部部分。 这种策略选择可以大幅减少 RAM 消耗,考虑到帧缓冲区阵列通常容量巨大,这是一个显着的优势。 然而,这种权衡体现在需要遍历要多次渲染的元素。 尽管如此,由于这些屏幕外元素在渲染过程中基本上被跳过,因此该过程仍然足够快。

这种内存分配方法体现了资源节约和性能优化之间的明智平衡。 通过明智地分配内存,该项目充分利用了更精简的占用空间的优势,同时减轻了渲染过程中的潜在瓶颈。 这一架构决策展示了对内存效率和计算便利性的细致入微的评估,体现了贯穿该项目软件设计的独创性。

PSRAM

PSRAM 内存容量高达 8 MB,可容纳可即时访问的数据。 最初的概念围绕着利用这一资源——要么作为帧缓冲区的存储库,要么作为 ADC 数据的增强缓冲区——但到目前为止,这一前景尚未开发。 该低级驱动程序经过精心设计,可确保功能和测量读/写吞吐量,坚持其讨价还价的目的,展示了两项操作每秒超过 10 兆字节的令人印象深刻的吞吐量。

QSPI 外设旨在通过模拟内部 RAM 使 CPU 能够直接访问 PSRAM,但存在一个小问题。 虽然 STM32 设备确实通过 QSPI 内存映射提供只读访问,但该项目需要具备读写能力。 因此,这一限制需要在两个方向上诉诸基于寄存器的访问,尽管 DMA 的能力得到了加强。

在此框架内进行操作需要一种细致入微的方法,乍一看类似于 SPI。 然而,用于命令、地址和数据传输的引脚数(范围从 0 到 4)的动态配置出现了复杂性。 这种编排在驱动程序的幕后进行,使应用程序层只需调用两个带有地址和缓冲区参数的函数(读取和写入)即可方便。 这种优雅的封装将复杂性提炼成简化的 API,促进无缝交互并有效利用这种扩展的内存资源。

TSC

触摸屏控制器 (TSC) 由久负盛名的 TSC2046 体现,它是 TI 的经典产品,已在许多先前的项目中占有一席之地。 该器件无缝集成到 LCD 引脚中,利用其嵌入式 ADC 进行读取。 驱动程序的角色简化为读取两个寄存器的任务,从而产生令人垂涎的 X 和 Y 坐标。

该硬件接口与旨在提高准确性和响应能力的软件层完美协调。 对精度的追求包含两个策略:首先,认真应用线性校正,将坐标与 LCD 的参考系对齐。 其次,该应用程序通过对多个读数进行平均来采取务实的方法,从而减轻噪声或变化的潜在影响。

硬件和软件的共生结合表现为触觉画布,它可以无缝捕获用户的触摸并将其转换为数字坐标。 这种技术的结合(TSC 硬件和软件的数据处理能力)共同创建了一个界面,在该界面中,人机交互具体化为连贯、直观的命令,丰富了用户的体验并强调了项目对细节的关注。

用户界面

用户界面 (UI) 模块充当用户界面状态的保管人,通过 Nuklear 库巧妙地将这种状态转换为视觉表示。 其架构被精心划分为不同的部分,每个部分专用于特定的功能菜单——采集、水平、垂直等。

为了响应触发更改的用户交互(例如更改采样率),新发现的值会被认真存储在 tUI 结构中。 这种精心安排的封装为 Scope 类中的后续调整铺平了道路,从而推动了必要的配置更改。 当前的实现在 UI 模块内直接调用 ST 的硬件抽象层 (HAL)。

这种层次结构可以导航用户交互的复杂领域,将人类意图无缝地转化为技术调整。 UI 模块在桥接用户操作和设备配置方面的关键作用体现了深思熟虑的架构设计,其中以用户为中心的考虑因素与基础硬件机制和谐地集成在一起。

波形产生

该模块控制双输出通道,协调它们的行为和功能。 它封装了一系列函数,旨在生成各种波形——正弦波、三角信号、PWM 等。 这些功能结合起来可配置定时器、DAC 和 DMA 外设的相互作用,最终实现所需信号的精确提取和传播。

这些组件的编排为信号生成的概念注入了活力,将抽象波形转变为有形的电气表现。 全面的可用功能不仅满足多功能性,还使开发人员能够自由地创作复杂的定制波形。

该模块的贡献是典型的——抽象信号定义、硬件配置和波形生成的无缝融合。 通过协调这些元素,它在整个项目中发挥着关键作用,在这个项目中,精确性与创造力、工程能力与表达潜力相结合。

示波器

Scope 模块充当监督整个采集系统的哨兵。 其任务包括配置设置的编排、采集过程的启动和停止。

在其范围内,具有利用和操作硬件组件的强大能力,将定时器、ADC、DMA 和触发检测器的复杂性连接在一起。 通过统一的界面,开发人员能够根据自己的规格塑造采集系统,无论是需要建立采样率、选择通道、定义触发条件还是启动实时数据捕获。

该模块的统治不仅仅局限于机制; 它是工程精度与用户意图融合的纽带。 Scope 模块的典型作用——弥合硬件复杂性和用户控制之间的鸿沟——体现了该项目的本质。 它概括了控制和洞察力的本质,其中单一的界面使操作员能够轻松而巧妙地命令和检查信号的复杂相互作用。

结论

见证这个示波器项目如何发展成为一项充满激情和创造力的工作,真是令人振奋。 尽管它在不断发展和完善,但该项目已经成熟为值得称赞的创作。 虽然输入范围和采集频率可能有其限制,但 UI 的多功能性和视觉上引人注目的 3D 打印饰面提升了项目的整体吸引力。