众筹网站CrowdSupply上的一些软件定义无线电(SDR)平台

收藏

分享

脑图

众筹网站CrowdSupply上的一些开源的SDR平台

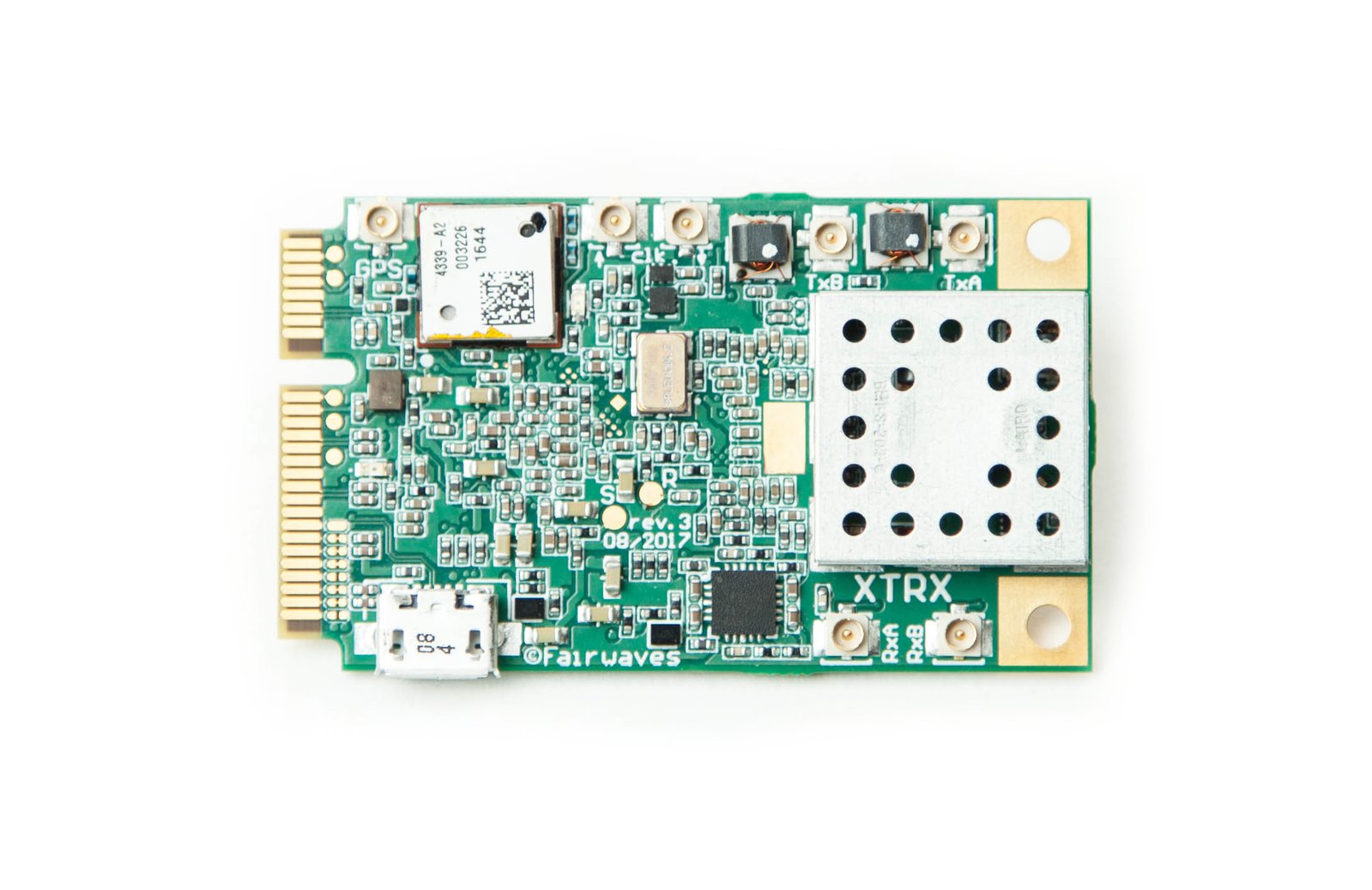

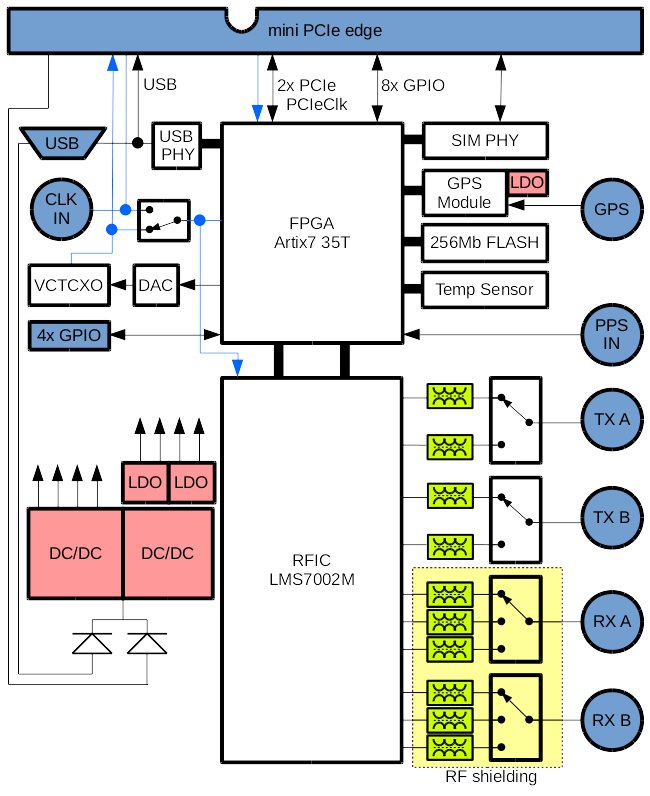

特性

RF Chipset: Lime Microsystems LMS7002M FPRF

FPGA Chipset: Xilinx Artix 7 35T/50T (CS/Pro)

Channels: 2 × 2 MIMO

RF Output Power: 0 to 10dBm depending on frequency

Sample Rate: ~0.2 MSPS to 120 MSPS SISO / 90 MSPS MIMO

Tuning Range: 30 MHz - 3.8 GHz

Rx/Tx Range:

10 MHz - 3.7 GHz

100 kHz - 3.8 GHz with signal level degradation

PCIe Bandwidth:

PCIe x2 Gen 2.0: 8 Gbit/s

PCIe x1 Gen 2.0: 4 Gbit/s

PCIe x1 Gen 1.0: 2 Gbit/s

Reference Clock:

Frequency: 26 MHz

Stability w/o GPS: 100 ppb or 500 ppb over the temperature range (depends on the XTRX version)

Stability w/GPS: <10 ppb stability after GPS/GNSS lock

Form Factor: full-size Mini PCIe (30 × 51 mm)

Bus Latency: <10 µs, stable over time

Synchronization: synchronize multiple XTRX boards for massive MIMO

GPIO:

FPC Edge Connector: four lines (usable as two diff-pairs)

Mini PCIe Reserved Pins: eight lines (including two diff-pairs, 1pps input, 1pps output, TDD switch control, and three LEDs)

Accessories:

Antennas + Cables

USB 3 Adapter with Aluminium Enclosure

PCIe x2 Lite Adapter

框图

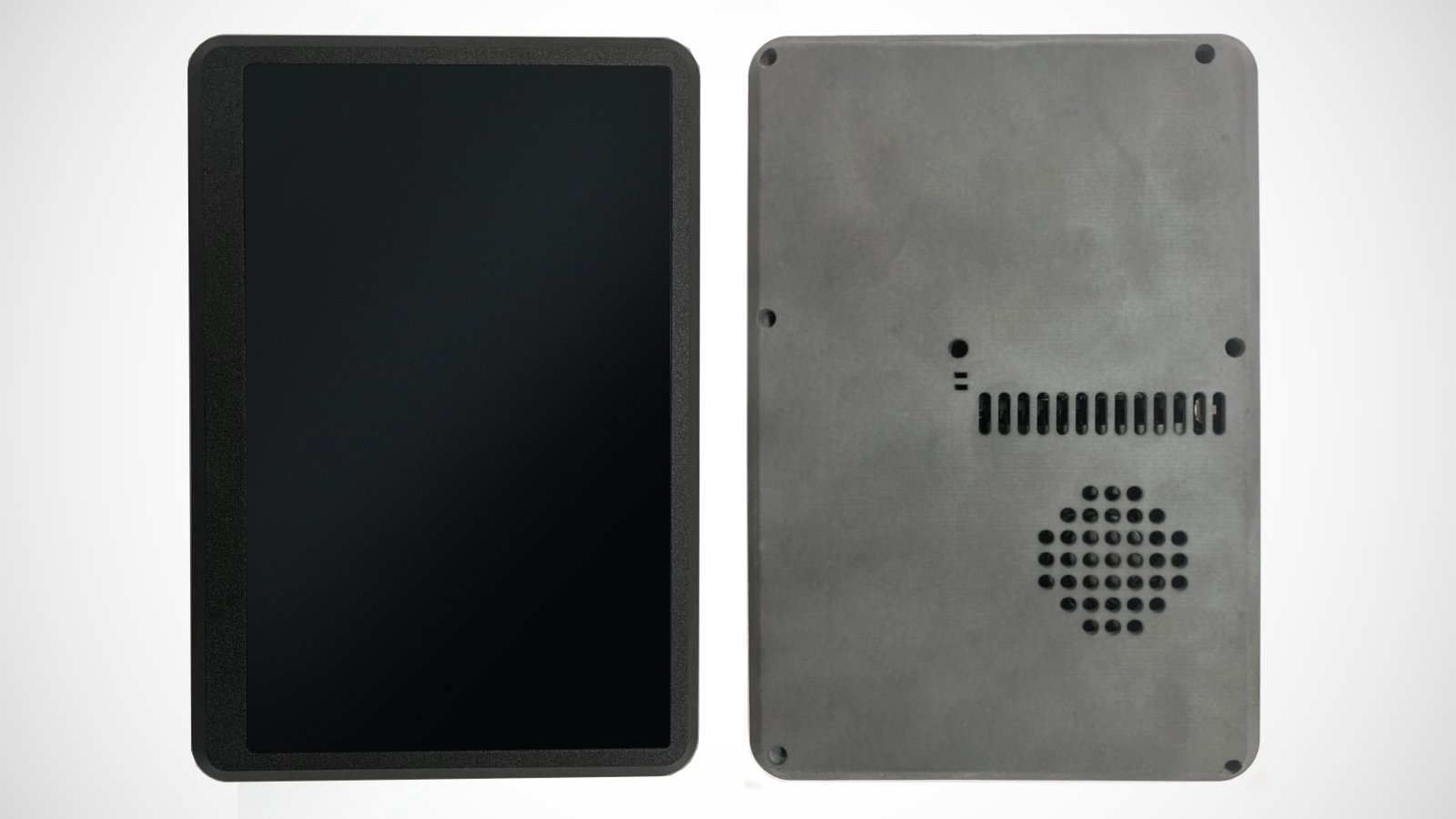

特性

Tablet

CPU Intel M3 8100Y 1.1 to 3.4 GHz, dual-core

MCU Arduino Leonardo

GPU Intel UHD Graphics 615, 300 to 900 MHz

RAM 8 Gb LPDDR3

Storage 64 GB eMMC 5.0

Screen 1024 x 600 pixel touchscreen

Connectivity

Wi-Fi 802.11ac at 2.4 & 5 GHz

Bluetooth Version 4.2

Ethernet Gigabit

USB One external USB Type-C connector & three internal USB Type-A connectors

M.2 One internal M-keyed connector & one internal E-keyed connector

Sound 3.5 mm audio jack

SDR

HackRF Customized to add TCXO clock & RF shielding and remove USB port & SMA clock-in/out

LimeSDR Mini Internal aluminum mounting bracket for standard LimeSDR Mini board

Power

Charging port USB Type-C

Capacity Approximately 24,000 mAh at 3.7 V or 12,000 mAh at 7.4 V

Lo-power modes Suspend

Main batteries Internal 18650 (not included)

RTC backup battery Internal CR927 (not included)

Operating System

GNU/Linux Ships with a recent long-term support (LTS) version of Ubuntu

Windows Full hardware support, software, and license not included

Software

Supported tools GNSS-SDR, GPS-SDR-SIM, HackTV, GNU Radio, etc.

HackRF Includes tutorials and code for analog video receving, BLE decoding, and NRF24L01 decoding

LimeSDR Mini srsLTE, OsmoNiTB, etc.

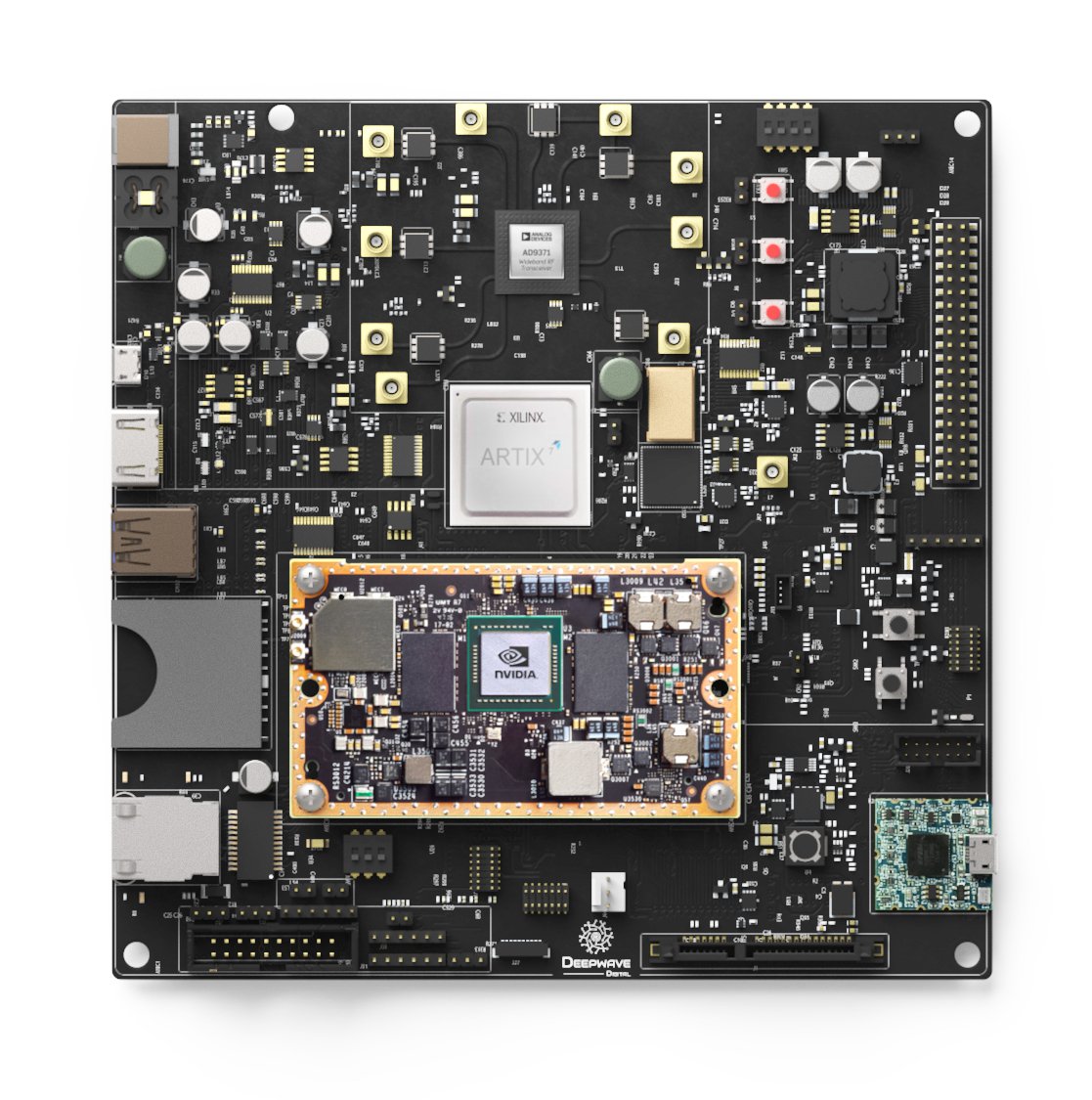

特性

RF Transceiver

Manufacturer Analog Devices 9371

Number of Receive Channels 2

Number of Transmit Channels 2

Maximum Bandwidth 100 MHz

Maximum Sample Rate 125 MSPS

Frequency Tuning Range 300 MHz - 6 GHz

Receiver Power Level Control AGC or manual gain control

Transmitter Power Level Control TPC or manual gain control

External Reference Input Yes

Built in Calibrations

Quadrature error correction

LO suppression

LO leakage correction

Processors

Manufacturer NVIDIA Jetson TX2

CPU 1 ARM A-57 (4-core)

CPU 2 ARM Denver2 (2-core)

GPU Pascal (256-core)

Memory 8 GBytes shared memory

Storage 32 GBytes flash

FPGA

Manufacturer Xilinx Artix-7 FPGA

LUTs 47.2k

DSP Slices 180

RAM 3.75 kbits

Networking

Ethernet 10/100/1000 BASE-T

WLAN 802.11a/b/g/n/ac dual-band 2x2 MIMO

Bluetooth Version 4.1

Display

HDMI 3840 x 2160 (4k)

Peripheral Interfaces

SATA Version 3.1

SD Card SD 3.0 or SD-XC cards up to 2 TB

USB

USB 3.0 Super Speed mode (up to 5Gb/s)

USB 2.0 High Speed mode (up to 480Mb/s)

USB On-The-Go

UART See NVIDIA Jetson TX2 datasheet for information

GPIO See NVIDIA Jetson TX2 datasheet for information

SPI See NVIDIA Jetson TX2 datasheet for information

I2C See NVIDIA Jetson TX2 datasheet for information

Audio See NVIDIA Jetson TX2 datasheet for information

Power

Input 8-15 VDC

Mechanical

Board Form Factor Mini-ITX

Dimensions 170 × 170 x 35 mm (6.7" × 6.7" x 1.4")

Weight 285 grams (0.63 pounds)

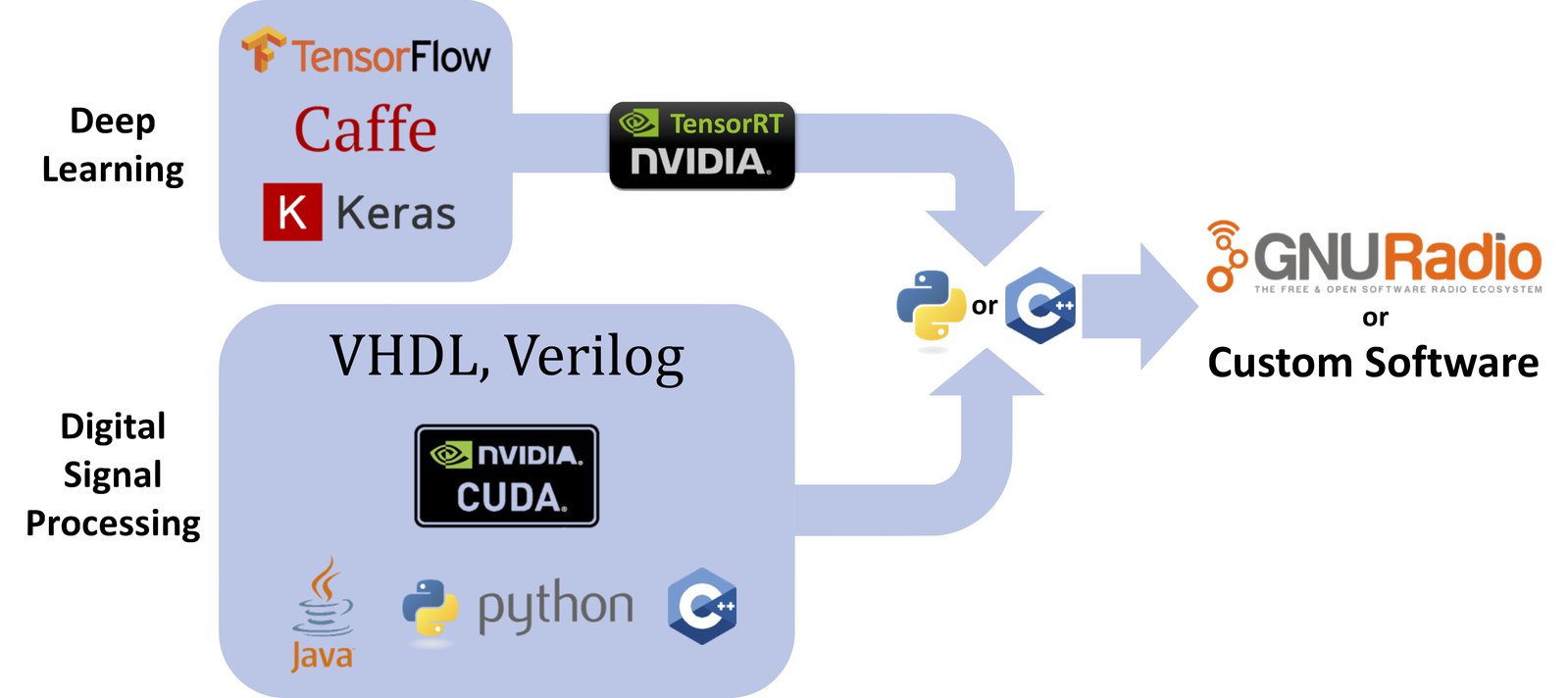

Software

Operating System Ubuntu (Linux)

Drivers AirStack

框图

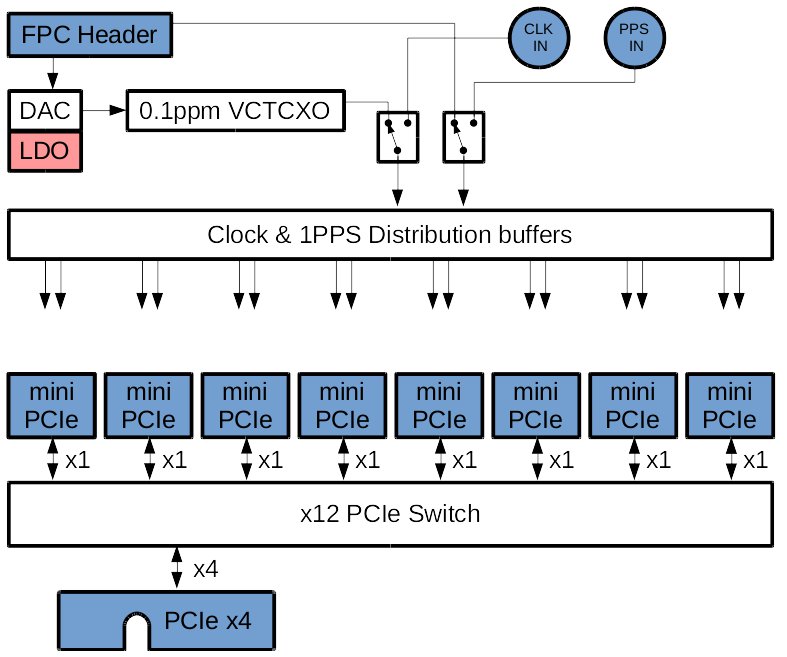

特性

RF Chipset: 8x Lime Microsystems LMS7002M FPRF

FPGA: 8x Xilinx Artix 7 50T

Channels: 16×16 MIMO

Sample Rate: ~0.2 MSPS to 120 MSPS per channel (subject to the limitations explained above)

PCIe Throughput: PCIe x4 Gen 2.0, 16 Gb/s

RF Amplifier: Qorvo QPL9503SR

RF Output Power: 0 to 10 dBm depending on frequency

RF Bandwidth: 1.4 MHz to 130 MHz

Tuning Range: 30 MHz - 3.8 GHz

RX/TX Range:

10 MHz - 3.7 GHz

100 kHz - 3.8 GHz with signal level degradation

Reference Clock:

Stability w/o GPS: 100 ppb from 0°C to 70°C

Stability w/GPS: <10 ppb stability after GPS/GNSS lock

Form Factor: full-size PCIe

Bus Latency: <10 µs, stable over time

Synchronization: synchronize two XYNC boards directly or more than two XYNC boards with an external clock distribution network

框图

特性

COM Express Type 10 Mini Rev. 3.0:

Low-cost Portwell PCOM-BA01: Atom E3940, 4 GB RAM, i210 Gigabit Ethernet

High-end AAEON NANOCOM-KBU: Core i7-7600U, 4 GB RAM, i219 Gigabit Ethernet

Dimensions (without enclosure): 102 x 73 x 36 mm with only vertical connectors

Power:

8.5 V to 50 V DC (12 V to 50 V DC for SATA support)

Input voltage monitoring

Polarity protection circuits

miniPCIe: 2x PCIe lanes (full XTRX SDR bandwidth support), no USB

Storage: M.2 SATA or SATA

I/O: DisplayPort, 2x USB 3.0, 1GbE, 2x RS232, SMBus, 16x GPIO, 4x ADC lines, RGB LED driver

Software-controlled high-load DCDC with 2x outputs

EEPROM: 128kB with one write-lockable page

Hardware watchdog

特性

Frequency range: 70-6000 MHz

Bandwidth: 40 MHz

Digital receiver IC: AD9364

Data interface: USB 3, using a Cypress FX3

Open source: software and hardware

Control: GNU Radio support

框图

特性

Mainboard

Form Factor: 105 x 110 mm

Processor: Intel Core i7-7500U, two cores, 2.7 GHz (3.5 GHz boost)

Memory: 32 GB (2 x 16 GB SO-DIMM) DDR4 2133 MHz

Storage: 512 GB SSD

Video

Intel HD Graphics 620

Mini DisplayPort 1.2: 3840 x 2160 @ 60 Hz

HDMI 2.0: 4096 x 2160 @ 60 Hz

Audio: Realtek ALC255

Connectivity

1 x USB 3.1 Type-C

1 x USB 3.1

2 x USB 3.0

1 x Gigabit Ethernet

Wi-Fi + Bluetooth (tentatively Intel Dual Band Wireless-AC 3168)

Power Supply

Power adaptor: 19 VDC input @ 3.42 A, 65 W

Cooling: single fan

Enclosure

Material: injection molded plastic and stainless steel

Dimensions: 11.2 x 12.0 x 5.2 cm (exclusive of antennas)

Partitions: top (black) holds mini PC, bottom (green) holds LimeSDR

Radio (Integrated)

Board: LimeSDR USB micro Type-B

Shielding: attached to LimeSDR

Antennas: five (of which one is dedicated for HF reception)

Cables: 5 x U.FL (internal and pre-installed)

Transmit Range: Approximately 15 meters for LTE

Power Amplifier: None

Filters: None

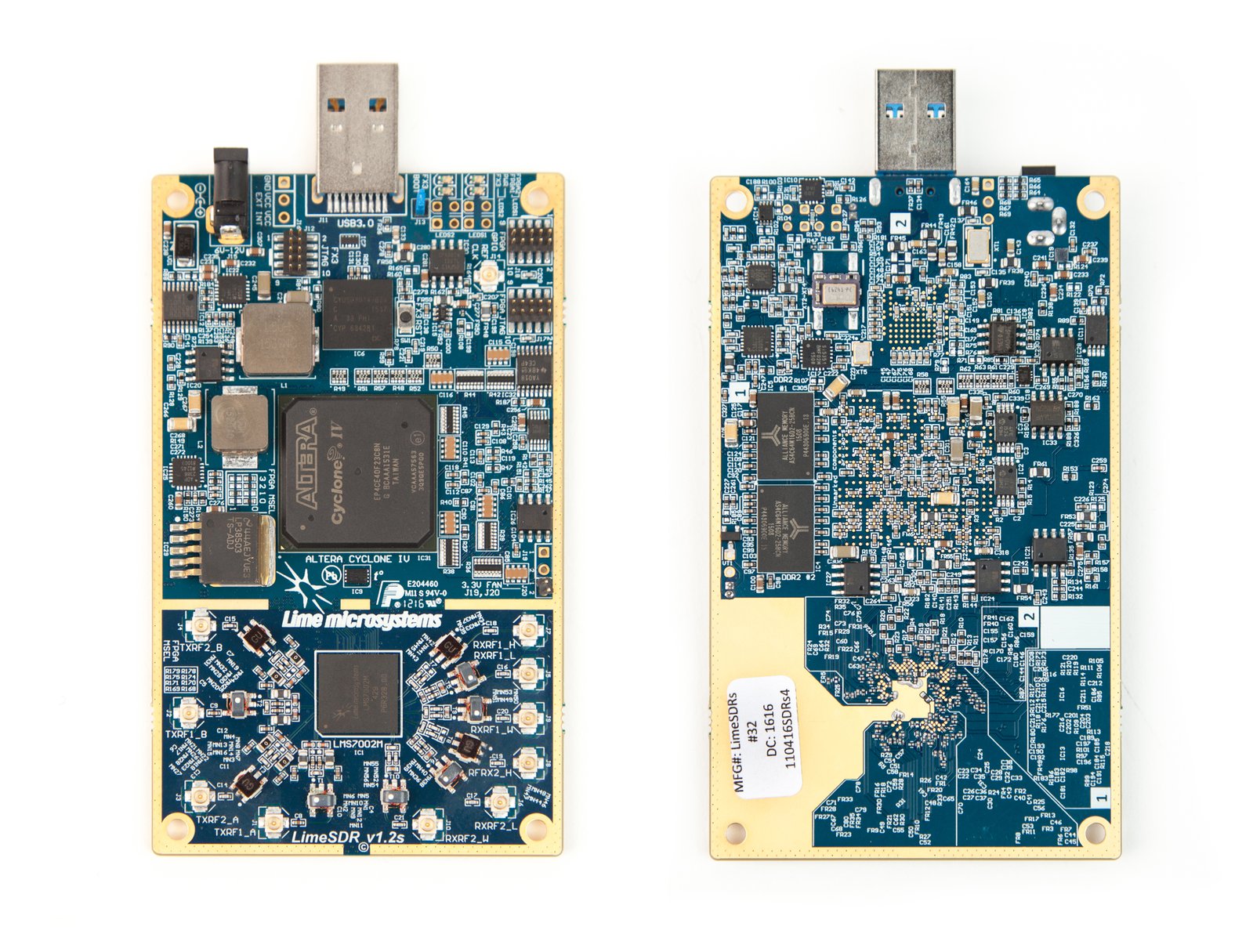

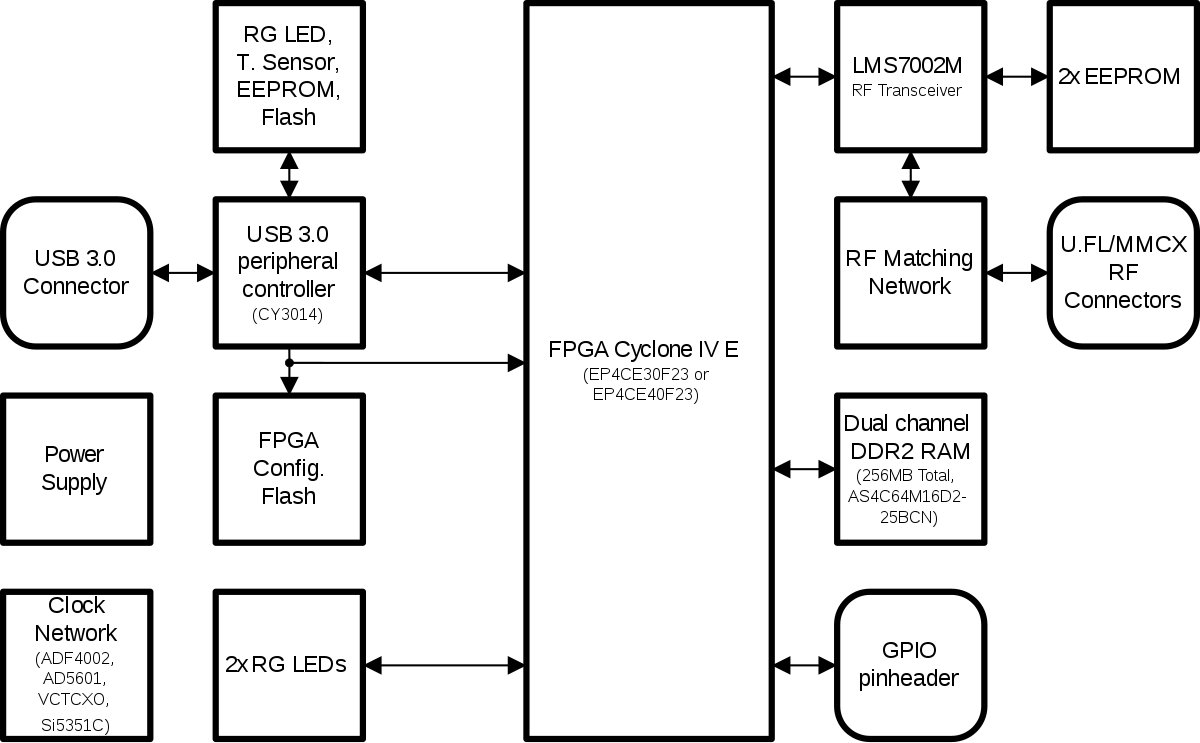

特性

RF Transceiver: Lime Microsystems LMS7002M MIMO FPRF (Datasheet)

FPGA: Altera Cyclone IV EP4CE40F23 - also compatible with EP4CE30F23

Memory: 256 MBytes DDR2 SDRAM

USB 3.0 controller: Cypress USB 3.0 CYUSB3014-BZXC

Oscillator: Rakon RPT7050A @30.72MHz (Datasheet)

Continuous frequency range: 100 kHz – 3.8 GHz

Bandwidth: 61.44 MHz

RF connection: 10 U.FL connectors (6 RX, 4 TX)

Power Output (CW): up to 10 dBm

Multiplexing: 2x2 MIMO

Power: micro USB connector or optional external power supply

Status indicators: programmable LEDs

Dimensions: 100 mm x 60 mm

框图

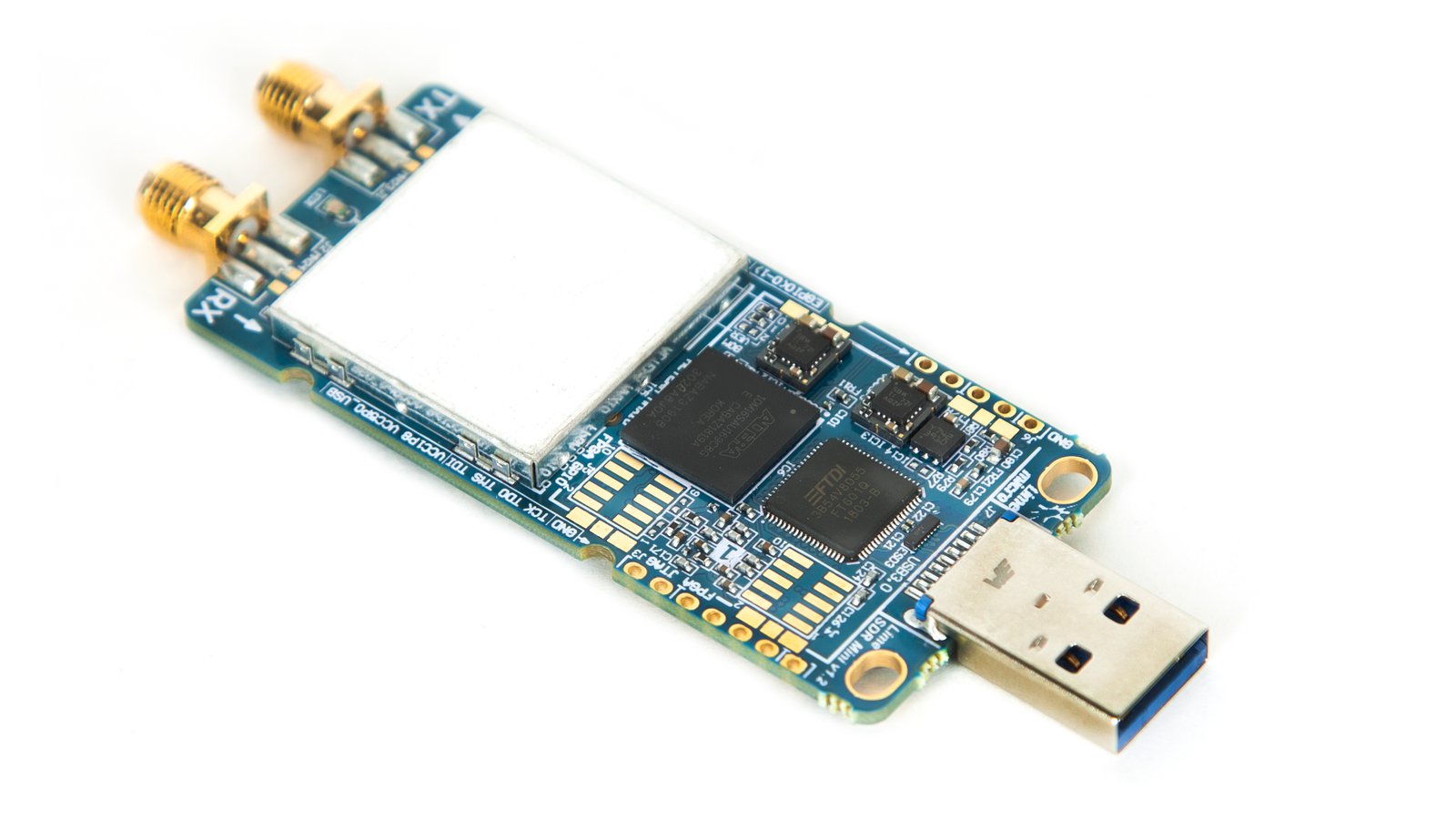

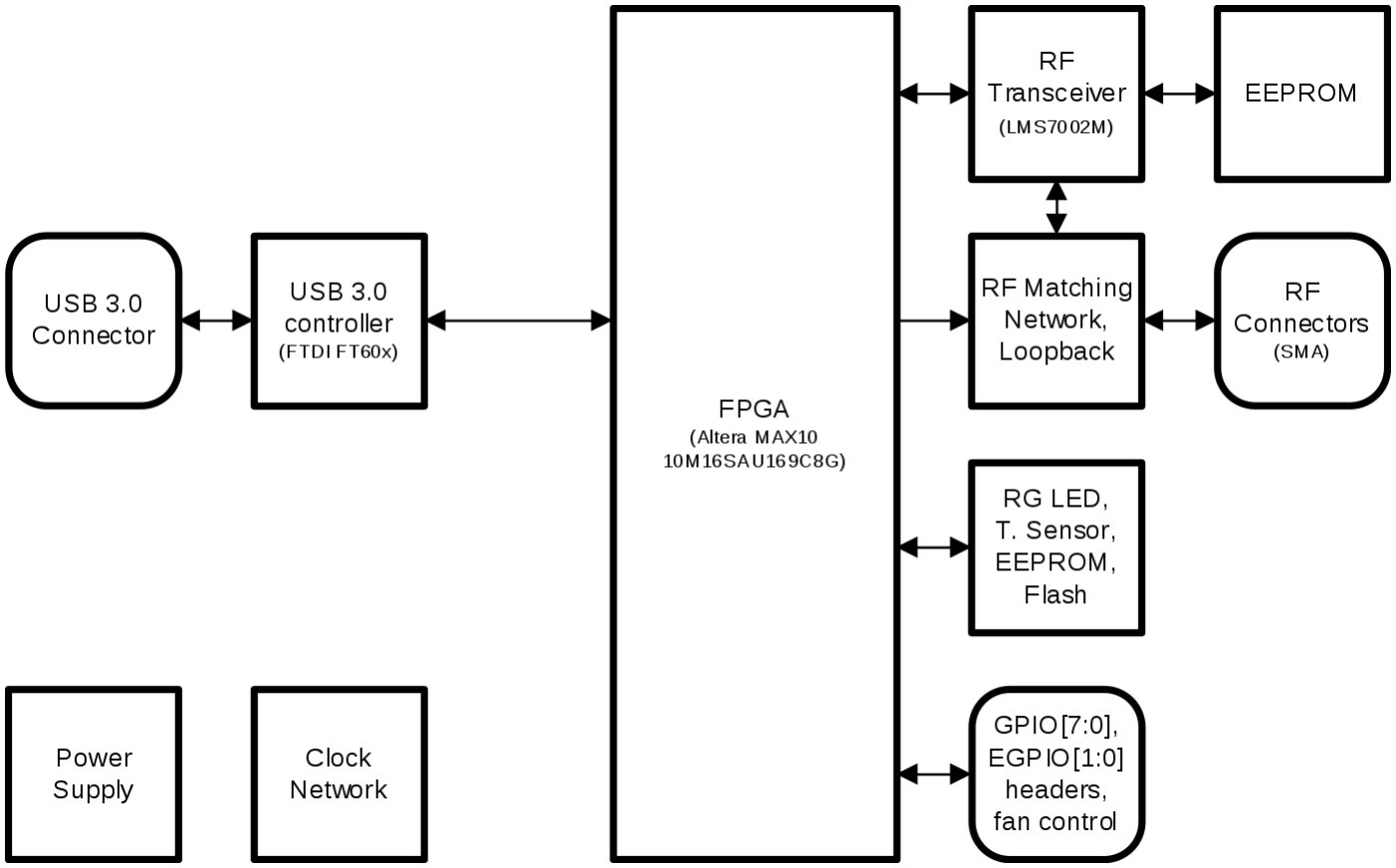

特性

RF transceiver: Lime Microsystems LMS7002M

FPGA: Intel Altera MAX 10 (10M16SAU169C8G)

169-pin FBGA package

16 K Les

549 KB M9K memory

2,368 KB user flash memory

4 x fractional phase locked loops (PLLs)

45 x 18x18-bit multipliers

130 x general purpose input/output (GPIO)

Single supply voltage

Flash feature

FPGA configuration via JTAG

EEPROM memory: 2 x 128 KB for RF transciever MCU firmware and data

Flash memory: 1 x 4 MB flash memory for data

General user inputs/outputs:

2 x dual color (red + green) LED

8 x FPGA GPIO pinheader (3.3 V)

Connectivity:

USB 3.0 Type-A (FTDI FT601 controller)

2 x coaxial RF (SMA) connectors (each can be switched between high and low frequency bands)

U.FL connector for external clock source

FPGA GPIO headers

FPGA JTAG connector

Clock system:

30.72 MHz onboard VCTCXO

Possibility to tune VCTCXO with onboard DAC

External clock input via U.FL connector

Board dimensions: 69 mm x 31.4 mm

Board weight: 20 grams

框图

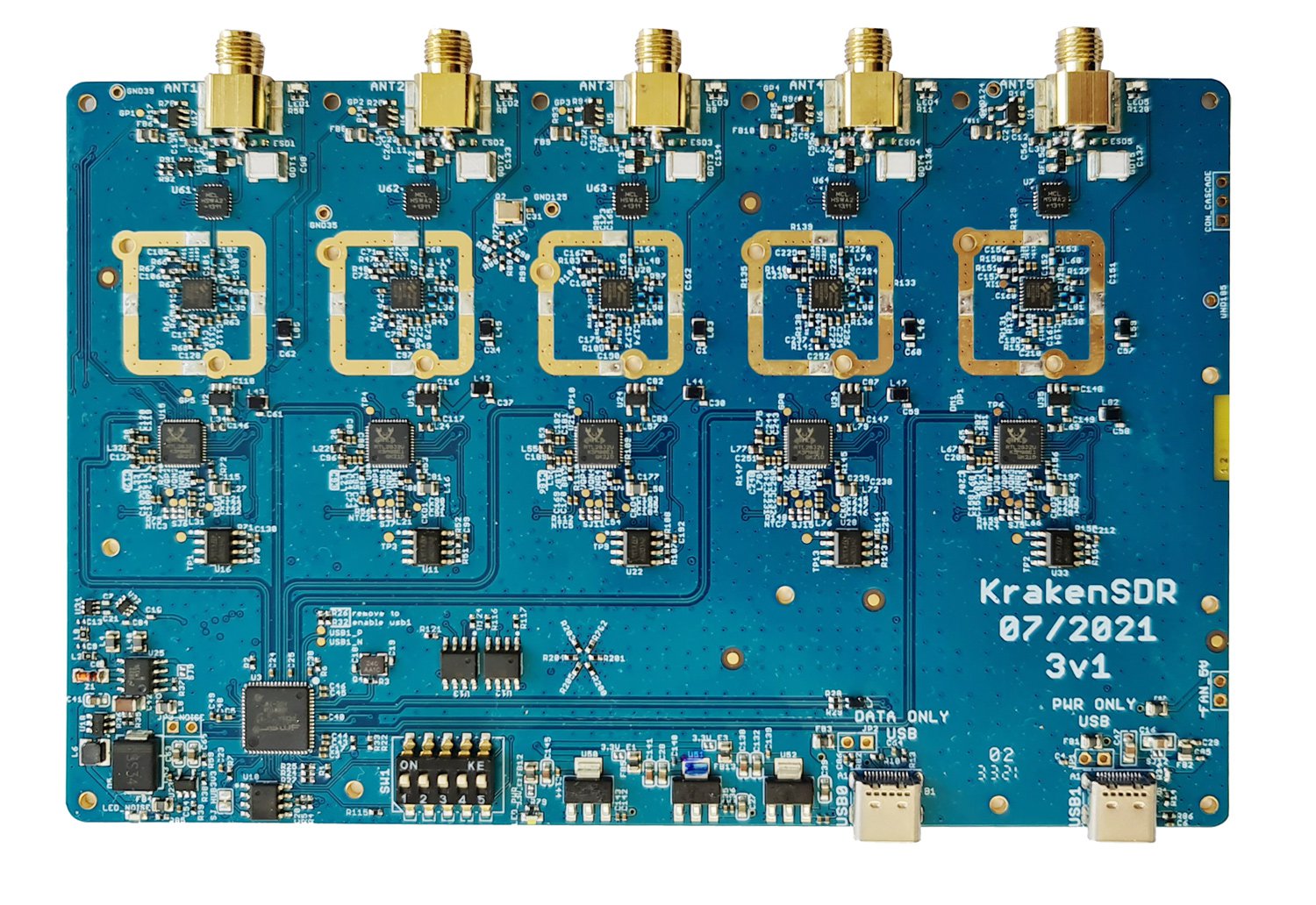

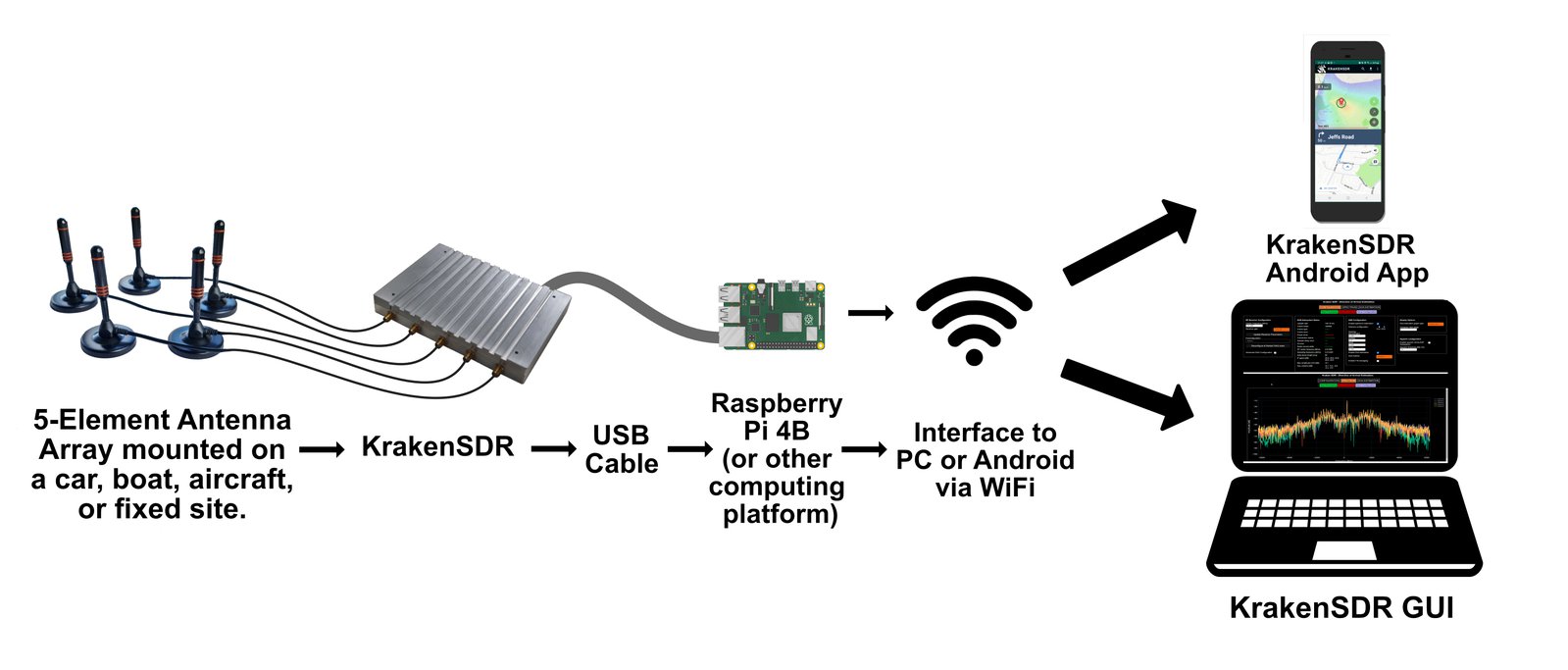

特性

Five-channel, coherent-capable RTL-SDR, all clocked to a single local oscillator

Built-in automatic coherence synchronization hardware

Automatic coherence synchronization and management via provided Linux software

24 MHz to 1766 MHz tuning Range (standard R820T2 RTL-SDR range, and possibly higher with hacked drivers)

4.5 V bias tee on each port

Core DAQ and DSP software is open source and designed to run on a Raspberry Pi 4 (see links below)

Direction-finding software for Android (free for non-commercial use)

Custom antenna set available

框图

特性

Transceiver: Analog Devices AD9364

Center Frequency: 70 MHz - 6 GHz

Maximum Analog Filter Bandwidth: 56 MHz

Sample Rate: 61.44 MSPS

Resolution: 12 bit

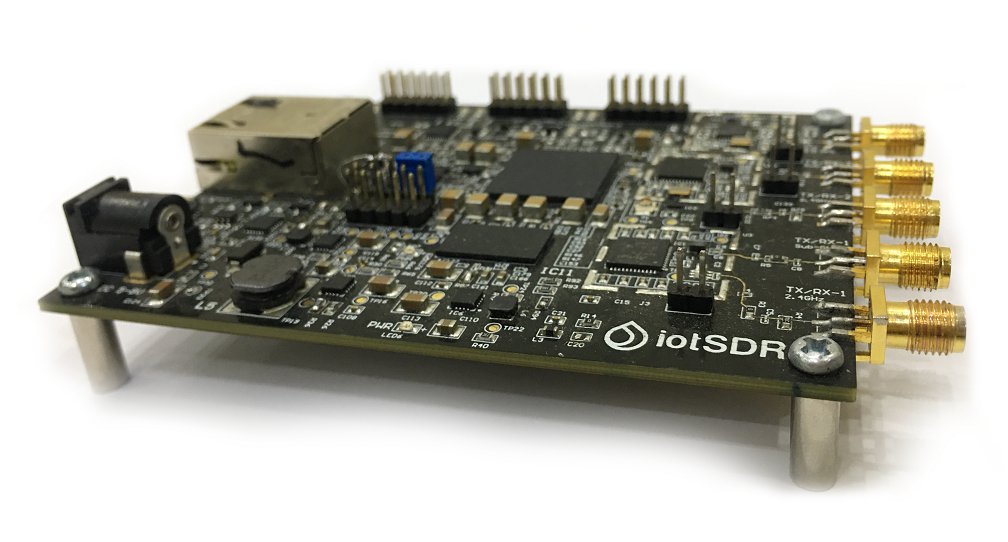

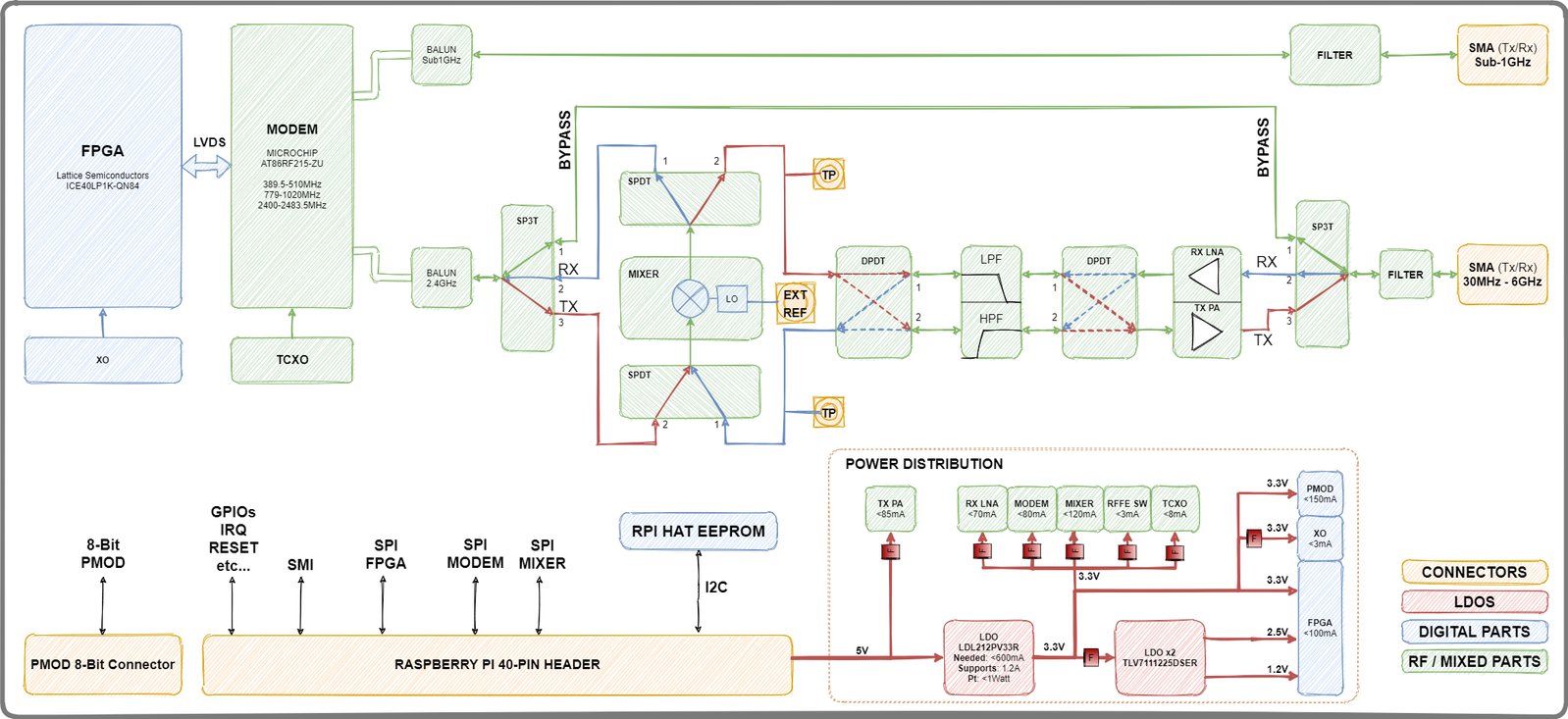

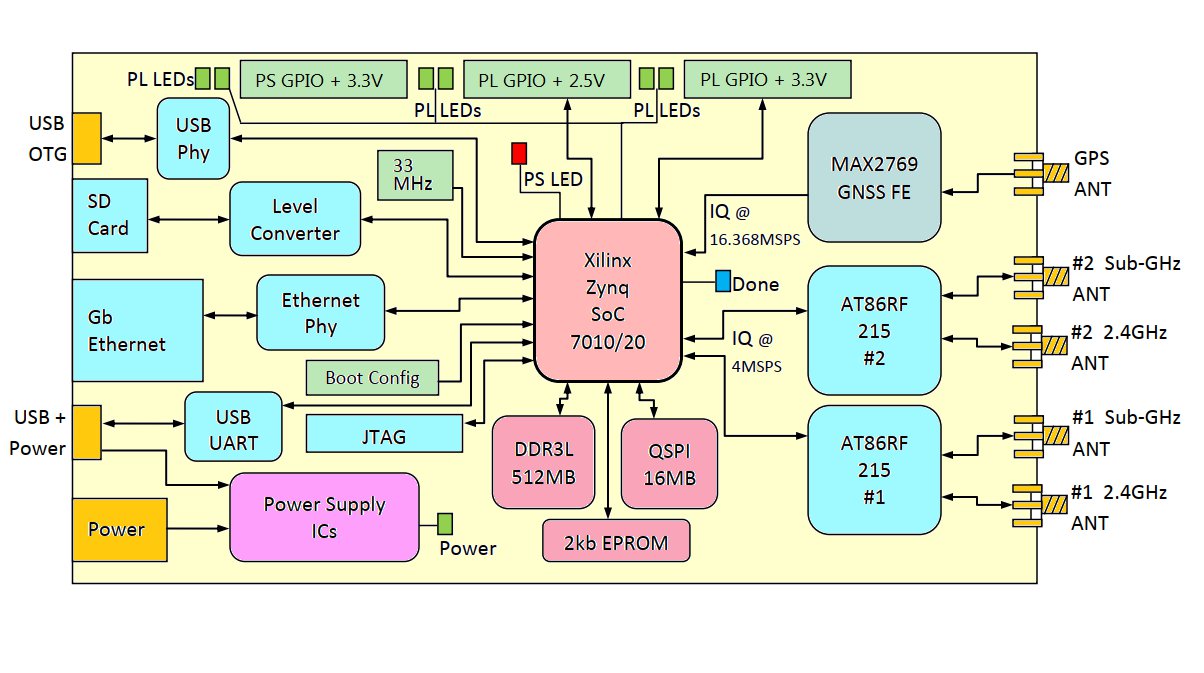

特性

RF Transceiver: 2x Microchip/Atmel AT86RF215

European band: 863-870 MHz / 870-876 MHz / 915-921 MHz

Chinese band: 470-510 MHz / 779-787 MHz

North American band: 902-928 MHz

Korean band: 917-923.5 MHz

Japanese band: 920-928 MHz

World-wide ISM band: 2400-2483.5 MHz

GNSS Receiver: Maxim MAX2769B supporting GPS, GLONASS, Galileo, and BieDou

SoC: Two options available

Xilinx ZYNQ XC7Z010-1CLG400C

Dual-core ARM Cortex-A9 MPCore

256 kb on-chip memory

DDR3 support

28,000 logic cells

17,600 LUTs

2.1 Mb block RAM

80 DSP slices

2x UART, 2x CAN 2.0 B, 2x I²C, 2x SPI, 4x 32-bit GPIO

FPGA configuration via JTAG

Xilinx ZYNQ XC7Z020-1CLG400C

Dual-core ARM Cortex-A9 MPCore

256 kb on-chip memory

DDR3 support

85,000 logic cells

53,200 LUTs

4.9 Mb block RAM

220 DSP slices

2x UART, 2x CAN 2.0 B, 2x I²C, 2x SPI, 4x 32-bit GPIO

FPGA configuration via JTAG

EEPROM Memory: 1x Microchip AT24MAC602 for RF transceiver MCU firmware and data

Flash Memory: 1x QSPI 128 Mb flash memory for firmware

RAM: 512 MB DDR3

SD Card: Micro SD card slot

General User Inputs/Outputs:

2x 8-bit PL (Programmable Logic) interfaces

1x 8-bit PS (Programmable Subsystems) interface

Connectivity:

1x Gigabit Ethernet

USB 2.0 High Speed (Microchip USB3310)

USB 2.0 Full Speed (Silicon Labs CP2104)

2x SMA RF connector for Low Frequency IoT band

2x SMA RF connector for 2.4 GHz band

1x SMA connector for GNSS receiver

FPGA JTAG connector for external JTAG programmer/debugger

Clock System:

Single clock source for both RF frontends

Separate clock for GNSS receiver

Board Dimensions: 76.2 mm x 101.6 mm

框图

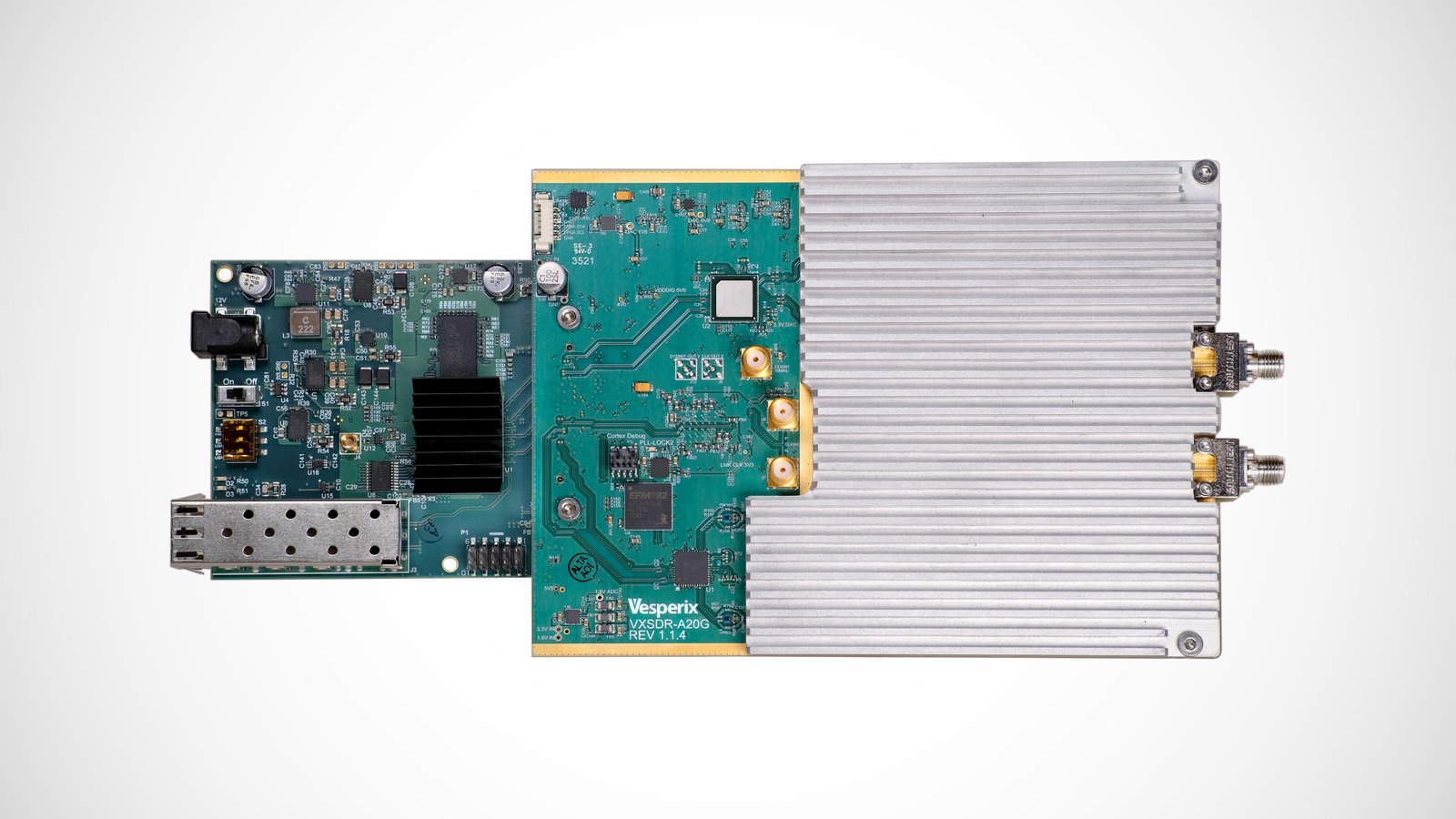

特性

Analog RF and IF

5.0 - 20.0 GHz transmit and receive (usable to 22 GHz)

5 - 9 dB receive noise figure

10 - 15 dBm output power

low-IF design (160 MHz IF)

TX output and TX/RX input/output (field replaceable SMA)

Digital

14-bit 160 MSPS A/D for receive

16-bit 160 MSPS D/A for transmit

JESD204B interfaces

Intel Cyclone 10 FPGA (85k - 220k logic elements)

Control and Data Transfer

10 gigabit Ethernet interface (SFP+)

Simultaneous full rate transmit and receive

PPS and 10 MHz inputs for synchronization

Software

C++ using boost::asio and boost::lockfree::spsc_queue (for data)

API similar to UHD, commonly used calls map easily

Currently supports Linux; Windows and Mac support in progress

Python bindings planned

GPL v3 licensing planned with GitHub repo

Power

12 V DC power input

22 W active, 16 W idle

Physical

9.4 inches (23.9 cm) long (including connectors)

4.1 inches (10.5 cm) wide

1.0 inches (2.4 cm) high

评论

0 / 100

查看更多

2022-02-03

1604

FPGA

SDR

软件定义无线电

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号