ZIPCPU及相关的设计资源

收藏

分享

脑图

ZIPCPU及相关的设计资源

关于ZIPCPU

由Gisselquist Technology, LLC.公司开发的运行在FPGA上的开源、全功能软核CPU

32位CPU - 所有的寄存器都是32位宽、地址也是32位,指令也是32位

RISC架构

Load/Store架构

兼容Wishbone,所有外设都通过存储器映射的I/O来寻址

冯诺伊曼结构:指令和数据共享总线

流水线结构

可以根据逻辑资源进行配置的CPU

可以用于各个厂商的FPGA

采用的工具

关于入门FPGA/Verilog的课程(PDF文件)

寄存器以及点灯

参考项目

An FPGA Design Automation routine

移植在FPGA上的ZipCPU

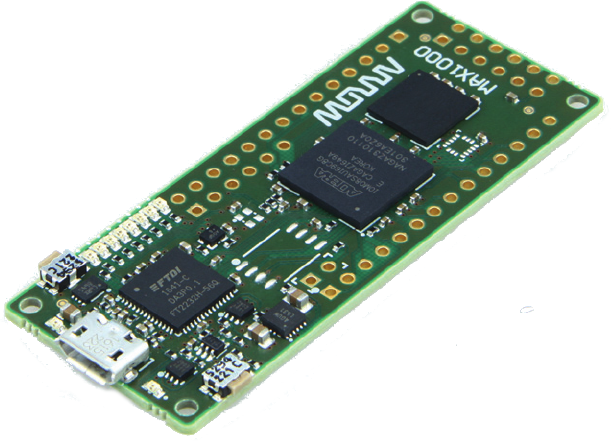

使用MAX1000开发板

DSP相关的Cores

与CPU外设相关的Cores

技术文章

如果调试FPGA?

开源FPGA设计工具

FPGA设计基础

如何构建和调试一个软核的CPU

How to debug a CPU core for an FPGA

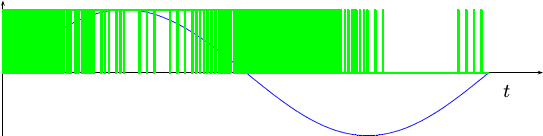

Besides building the toolchain, this post offers a fun way to view how the logic moves its way through the ZipCPU as a result of the three separate ZipCPU prefetch modules.

Profiling your CPU using Verilator

o How a really simple Operating System works.

Wishbone总线

AXI总线

互联

SoC + FPGA架构

CPU设计话题

DSP话题

Interpolation

o A filter based upsampling interpolation method

o Polynomial Interpolation a.la Harris

o Why splines are entirely inappropriate for real-time DSP

CIC Filters

o CIC upsampler

o CIC downsampler

Sine, Cosine, and Arctangent calculation

Downconverting an incoming signal using a CORDIC

Generating AM, FM, and QAM types of signals using the CORDIC

o A quadratic table based sin/cos generator, optimized for reduced phase noise and reduced spur energy. This requires two multiplies, and so it improves performance over the CORDIC approach

关于数字滤波器的一些通用话题

o High speed filtering. These filters will run at your system clock speed, or not at all.

High speed symmetric FIR implementation

Halfband FIR implementation

Hilbert Transform

o Low-speed filtering. These filters run N times slower than your system clock speed. They are more efficient, if you can use them.

In general, these will be the same filters as their high speed counterparts.

A cascaded slow FIR filter. This article will present an approach that allows you to cascade filter blocks together in order to implement a longer filter.

o Building a delay

o Estimating a filter’s cost

多数率信号处理

How to test a digital filter

o Finding IIR limit cycles

Digital PLL design

o PLLs with better (CORDIC-based) phase estimators

o Using a PLL together with a FIFO, for asynchronous sample rate conversion

FFT and other spectral estimation topics

o Building a scrolling raster framebuffer

o Color mapping the FFT’s results to the framebuffer

o Maximally resolved FFT window functions

o Optimizing the window function for high spectral resolution

评论

0 / 100

查看更多

2021-12-19

3109

FPGA

数字逻辑

软核

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号