2021年全国大学生电子设计竞赛E题-数字-模拟信号混合传输收发机

收藏

分享

脑图

2021年全国大学生电子设计竞赛E题-数字-模拟信号混合传输收发机

任务

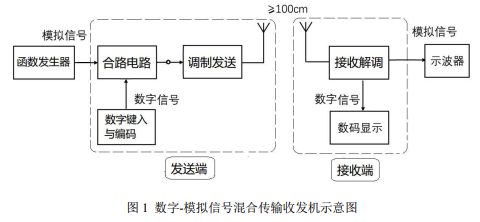

设计并制作在同一信道进行数字-模拟信号混合传输的无线收发机。其中,数字信号由 4 个 0~9 的一组数字构成;模拟信号为语音信号,频率范围为100Hz~5kHz。采用无线传输,载波频率范围为 20~30MHz,信道带宽不大于 25kHz,收发设备间最短的传输距离不小于 100cm。收发机的发送端完成数字信号和模拟信号合路处理,在同一信道调制发送。

收发机的发送端完成数字信号和模拟信号合路处理,在同一信道调制发送。收发机的接收端完成接收解调,分离出数字信号和模拟信号,数字信号用数码管显示,模拟信号用示波器观测。

基本要求

(1) 实现模拟信号传输。模拟信号为 100Hz~5kHz 的语音信号,要求接收端解调后的模拟信号波形无明显失真。在只有模拟信号传输时,接收端的数码显示处于熄灭状态。

(2) 实现数字信号传输。首先键入 4 个 0~9 的一组数字,在发送端进行存储并显示,然后按下发送键对数字信号连续循环传输。在接收端解调出数字信号,并通过 4 个数码管显示。要求开始发送到数码管显示的响应时间不大于 2 秒。当发送端按下停止键,结束数字信号传输,同时在发送端清除已传数字的显示,等待键入新的数字。

(3)实现数字-模拟信号的混合传输。任意键入一组数字,与模拟信号混合调制后进行传输。要求接收端能正确解调数字信号和模拟信号,数字显示正确,模拟信号波形无明显失真。

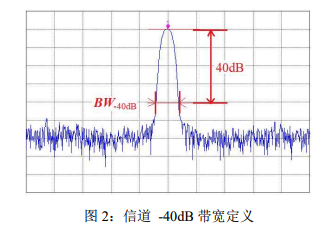

(4) 收发机的信道带宽不大于 25kHz,载波频率范围为 20~30MHz。要求收发机可在不少于 3 个载波频率中选择设置,具体的载波频率自行确定。

发挥部分

(1)在发送端停止数字信号传输后,接收端数码显示延迟 5 秒自动熄灭。

(2)在满足基本要求的前提下,收发机发送端的功耗越低越好。

(3)在满足基本要求的前提下,收发机所传输的模拟信号频率范围扩展到50Hz~10kHz。

说明

(1)数字和模拟信号必须先经过合路电路处理,然后在同一信道上调制传输,其调制方式和调制度自行确定。在合路电路的输出端应留有观测端口,用于示波器观测合路信号的波形变化。

(2)收发机的发送端和接收端之间不得有任何连线。

(3)收发机的发送端与天线的连接采用 SMA 接插头,发送端为 F(母)头,天线端为 M(公)头。天线的长度不超过 1 米。

(4)收发机的发送端和接收端均采用电池单电源供电,发送端的供电电路应留有供电电压和电流的测试端口。

(5)收发机的载波频率选取应尽量避开环境电波干扰。

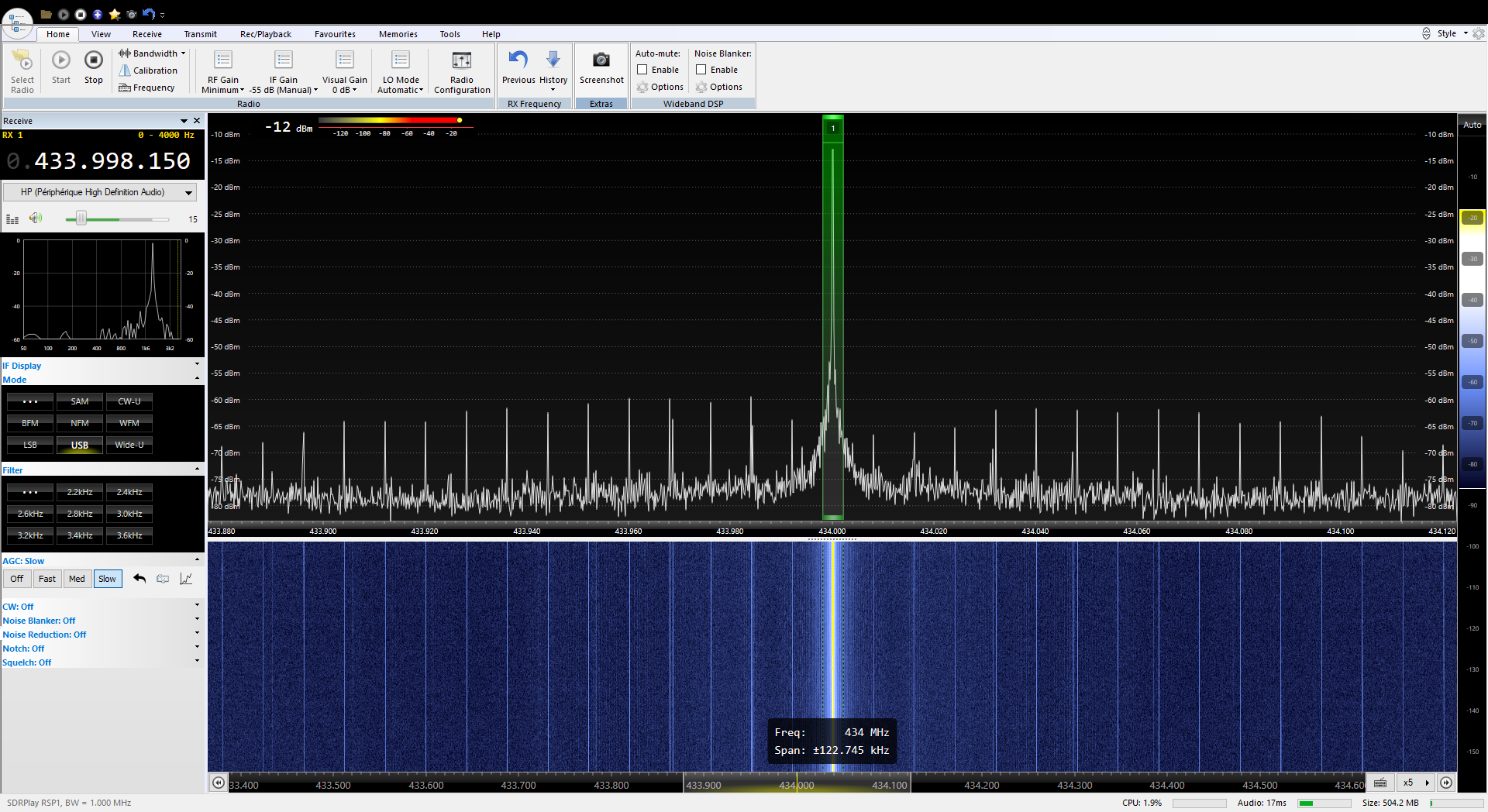

(6)本题目中信道带宽约定为已调信号的 -40dB 带宽,通过频谱仪进行测量。具体如图 2 所示。

要点

语音信号的量化

5KHz模拟带宽,大于10Ksps

8bit ADC

如果使用FPGA,可以使用高速比较器 + Sigma Delta实现ADC的功能,能够支持到对语音信号的采样

Mux

制定一套简单的协议,标记语音和数据

数字调制/DDS

建议采用PSK/FSK

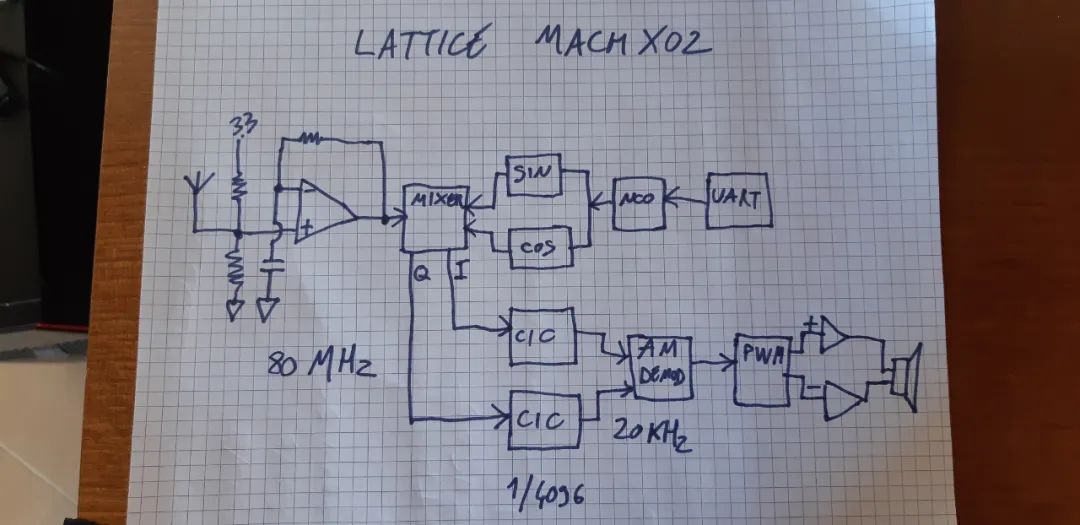

载波通过FPGA的NCO产生

Mixer在FPGA里面实现

要生成20-30MHz的载波信号,建议使用80Msps以上的DAC,如果使用50Msps的DAC,可以使用其混叠频率

建议使用10bit/100Msps的DAC,10bit/50Msps也可以用

数字解调

ADC

取样频率50Ksps以上的就可以,模拟带宽要在30MHz以上

数字下变频

NCO

Mixer

数字解调

时钟恢复

数据判决

语音/数据 Demux

天线

频率范围在20-30MHz,波长较长~10-15米

网上找开源的Verilog代码

使用的器件

FPGA

ADC

高模拟带宽/50ksps以上转换率用于接收机

普通ADC - 10Ksps/8bit

DAC

高速建议:50Msps/10bit

参考资料

搜索关键词 digital modulator或digital modulation

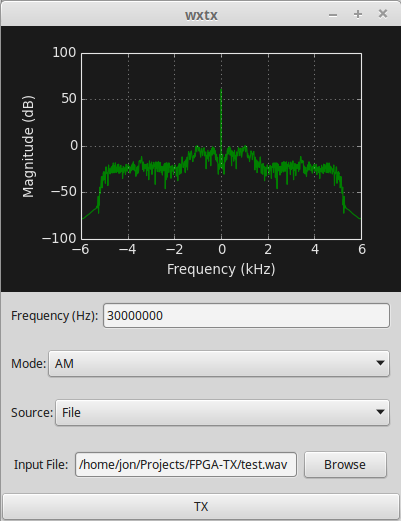

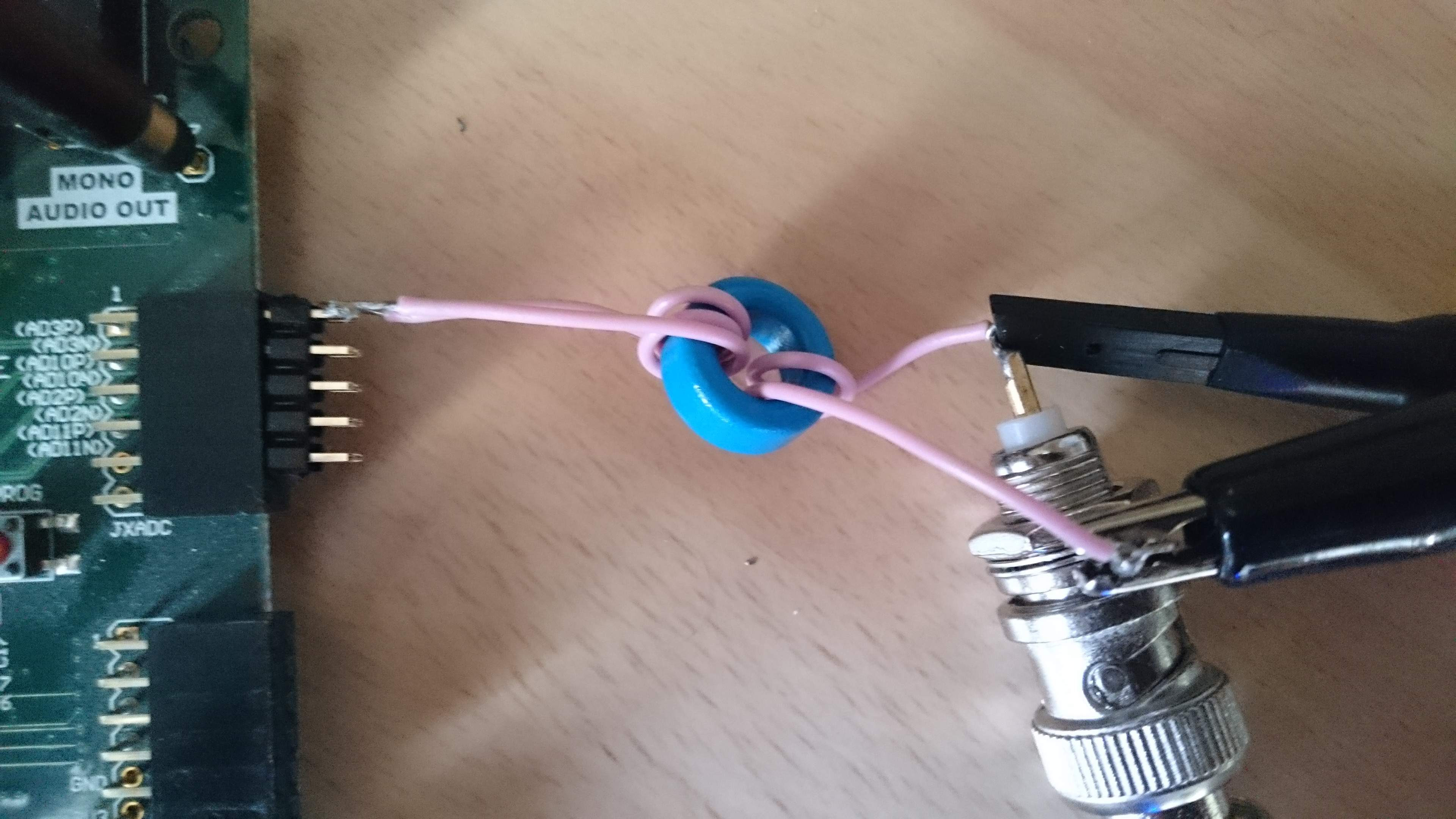

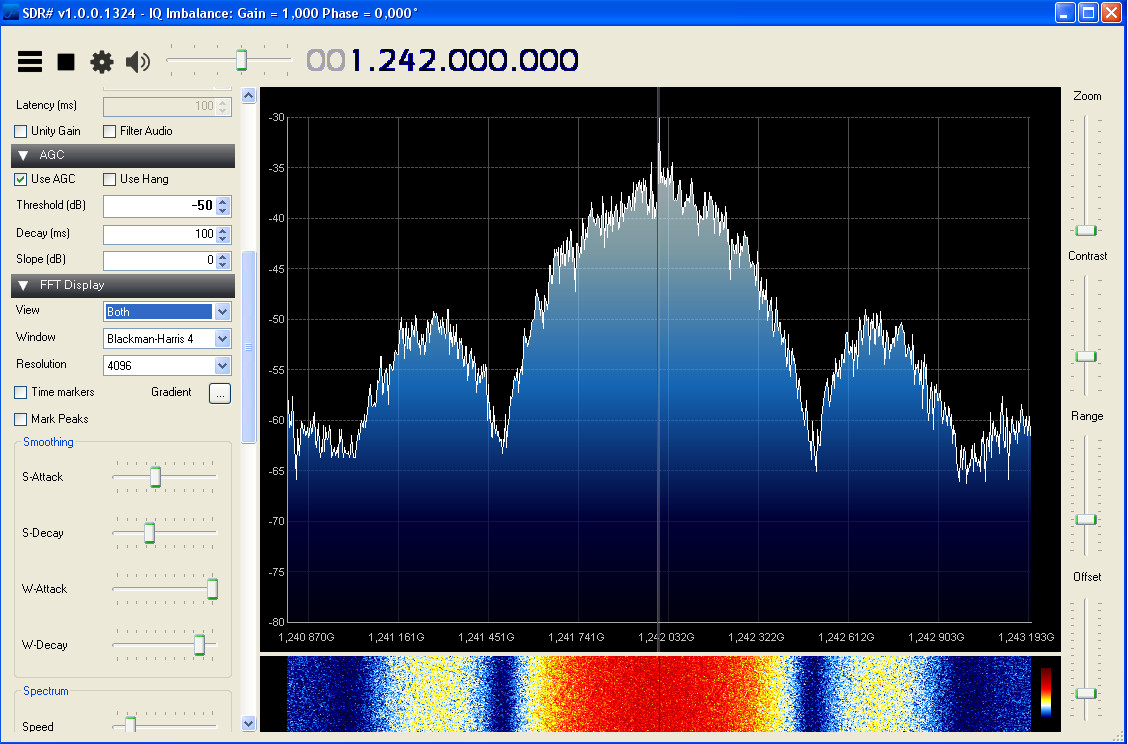

FPGA-TX can transmit at frequencies of up to 400 MHz and current supports AM, FM, LSB, USB, Wideband FM and Wideband FM Stereo transmission modes. It runs on Linux. The FPGA transmitter has been tested combined together with an amplifier and filter. It can also interface with a GPS unit for clock calibration.

用树莓派制作FM发射机

Audio file in WAV format 22050Hz, 8 bits, MONO is simply transmitted to the board via the serial port. The board accepts bytes and broadcasts this stream in the FM band at a frequency of 90 MHz.

The frequency modulator itself is written in Verilog HDL and is very simple. The project uses an initial frequency of 450 MHz and is almost always divided by 5 with a resulting frequency of 90 MHz. Since for frequency modulation it is necessary to change the frequency within small limits, sometimes after many divisions by 5 the insert “division by 4” is done. The more such inserts, the higher the average frequency of the digital sequence. This is sufficient for the receiver to detect the signal.

评论

0 / 100

查看更多

2021-11-10

8867

电赛

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号